# Электротехника и электроника Лекция 14

Элементы цифровой электроники, Логические элементы, комбинационные устройства. Триггеры. Булева алгебра.

Мириленко Андрей Петрович, к.т.н. кафедра Электротехники

#### Основы цифровой электроники

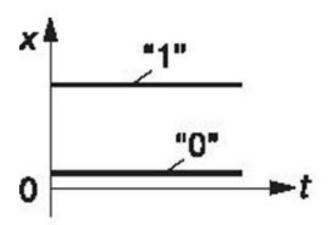

*Цифровыми* называют устройства, предназначенные для формирования, преобразования и передачи **кодовых слов**. Кодовые слова (или числа) в электронных цифровых устройствах представляются в виде электрических импульсов (сигналов с ДВУМЯ уровнями напряжения: высоким и низким),

Элементами и узлами цифровых устройств, служащими основой для построения микропроцессоров, микропроцессорных систем, компьютеров, автоматизированных систем управления объектами, технологическими процессами: дешифраторы, сумматоры, триггеры, регистры, счетчики и многие другие.

### Объекты цифровой электроники

#### Логические переменные

Переменная, принимающая только логические значения: "истина" или "ложь"

$$1 = ucmuha = true$$

$$0 = ложь = false$$

#### Двоичные числа

$$A = a_1 \cdot 2^{n-1} + a_2 \cdot 2^{n-2} + \dots + a_n \cdot 2^0$$

$$27_{(2)} = 1 \times 16 + 1 \times 8 + 0 \times 4 + 1 \times 2 + 1 \times 1$$

$$27_{(2)} = 1 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0$$

$$27_{(2)} = 11011$$

также как

$$132_{(10)} = 1 \times 10^2 + 3 \times 10^1 + 2 \times 10^0$$

Для оценки количества цифровой информации используют *бит* и *байт* (1 байт = 8 бит). 1 бит — это мера информации, выражающая такое её количество, которое может передать один символ двоичного алфавита при равной вероятности появления каждого символа алфавита:

Так, в 8-разрядном слове информационная ёмкость равна 8 битам или 1 байту

Логическими устройствами называют схемные элементы, с помощью которых осуществляется преобразование поступающих на их входы двоичных (бинарных) сигналов и непосредственное выполнение предусмотренных логических операций.

## Функции булевой алгебры

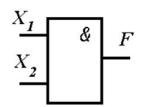

Конъюнкция = логическое умножение = операция  $И = \& = * = ^$

| X1 | X2 | F |

|----|----|---|

| 1  | 1  | 1 |

| 1  | 0  | 0 |

| 0  | 1  | 0 |

| 0  | 0  | 0 |

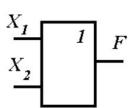

Дизнъюнкция = логическое сложение = операция ИЛИ = 1 = + = v

| X1 | X2 | F |

|----|----|---|

| 1  | 1  | 1 |

| 1  | 0  | 1 |

| 0  | 1  | 1 |

| 0  | 0  | 0 |

## Функции булевой алгебры

Инверсия = логическое отрицание = операция НЕ

$$F = \overline{X}$$

$$X_1$$

$I$   $F$

Отрицание логического умножения = операция И-НЕ

$$F = \overline{X_1 * X_2}$$

$$X_1$$

&  $F$

Отрицание логического сложения= операция Или-НЕ

$$F = \overline{X_1 + X_2}$$

$$X_1$$

$I$   $F$

| X1 | F |

|----|---|

| 1  | 0 |

| 0  | 1 |

| X1 | X2 | F |

|----|----|---|

| 1  | 1  | 0 |

| 1  | 0  | 1 |

| 0  | 1  | 1 |

| 0  | 0  | 1 |

| X1 | X2 | F |

|----|----|---|

| 1  | 1  | 0 |

| 1  | 0  | 0 |

| 0  | 1  | 0 |

| 0  | 0  | 1 |

#### Цифровые устройства. Комбинационные устройства

В комбинационных устройствах (автоматах без памяти) значения F в течение каждого такта работы определяются значениями X только в этот же такт, и не зависят от того, какие переменные подавались на входы в предыдущие такты, т. е. F = f(X).

Эти устройства лишены памяти: не хранят информацию о прошлом. Входные и выходные сигналы комбинационных устройств могут принимать только два значения: 1 и 0.

По функциональному назначению можно выделить следующие классы КУ:

- сумматоры,

шифраторы и дешифраторы,

цифровые компараторы,

мультиплексоры и демультиплексоры,

преобразователи кодов,

программируемые логические матрицы,

перемножители,

- □ арифметикологические устройства.

#### Цифровые устройства. Дешифраторы

Дешифратор или декодер — комбинационная схема с п входами и т выходами (m > n), преобразующая двоичный входной п-код в унитарный.

На одном из *m* выходов дешифратора появляется логическая единица, а именно на том, номер которого равен поданному на вход двоичному числу. На всех остальных выходах дешифратора выходные сигналы равны нулю.

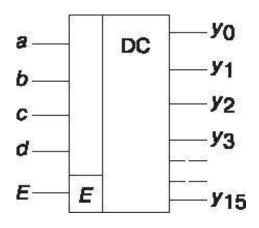

Условное изображение дешифратора 4-16 (читаемого "четыре в шестнадцать")

Дешифраторы часто имеют *разрешающий* (управляющий, стробирующий) вход *E*. При *E* = 1 дешифратор функционирует как обычно, при *E* = 0 на всех выводах устанавливается 0 независимо от поступающего кода адреса.

#### Цифровые устройства. Шифратор

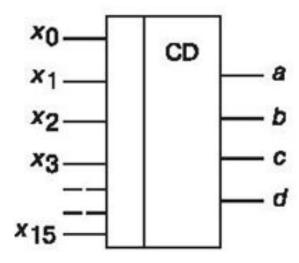

Шифратор (CD) или кодер выполняет функцию, обратную дешифратору. Условное изображение шифратора 16-4 на схемах показано на рис. 4.48, а. Классический шифратор имеет п входов и т выходов (т < п), и при подаче сигнала на один из входов (и не более) на выходе узла появляется двоичный код номера возбуждённого выхода. Число входов и выходов такого шифратора связано соотношением п = 2m

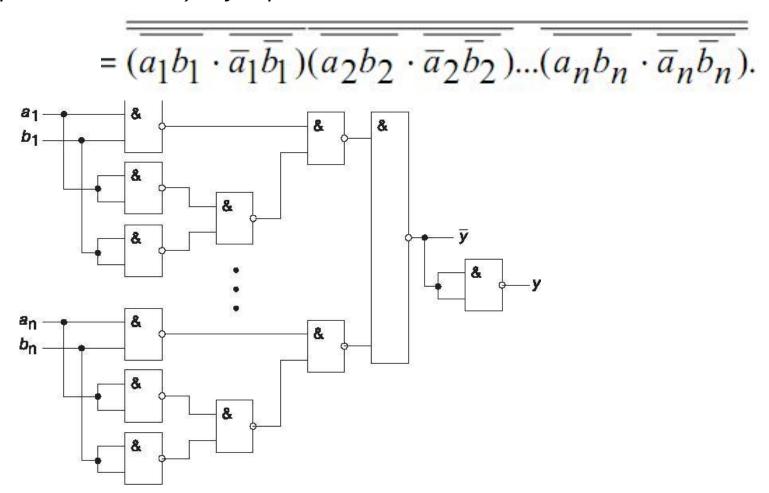

### Цифровые устройства. Компаратор (сравниватель)

Цифровой компаратор предназначен для определения равенства двоичных чисел. Операция поразрядного сравнения заключается в выработке признака равенства (равнозначности) или неравенства (неравнозначности) двух сравниваемых двоичных чисел

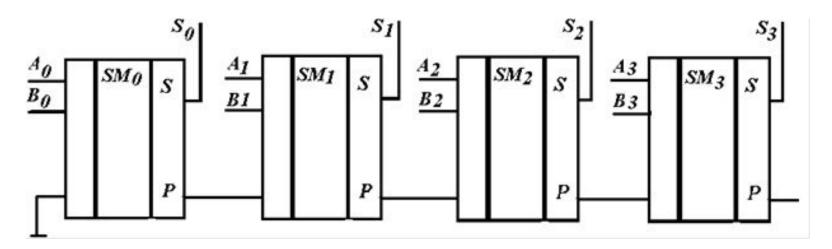

Сумматор — это узел, в котором выполняется арифметическая операция суммирования цифровых кодов двух двоичных чисел.

Двоичнокодированные десятичные сумматоры. На входы *a*0, *a*1, *a*2, *a*3 подается двоичный код одной из суммируемых десятичных цифр, на входы *b*0, *b*1, *b*2, *b*3 — двоичный код второй десятичной цифры, а на вход *pi* — значение переноса из соседнего младшего разряда. На выходах *S*0, *S*1, *S*2, *S*3 образуется двоичный код десятичной цифры данного разряда суммы, а на выходе *pi*+1 — значение переноса в соседний старший разряд.

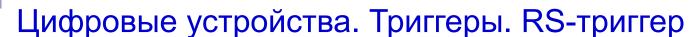

### Цифровые устройства. Триггеры

Триггер — устройство, обладающее двумя устойчивыми состояниями и способное переходить из одного состояния в другое под воздействием внешнего управляющего сигнала, превышающего пороговое значение. При отсутствии внешних воздействий триггер может сколь угодно долго находиться в одном из устойчивых состояний.

Различают триггеры асинхронные, которые переключаются в момент подачи вход¬ного сигнала, и синхронные (тактируемые), которые переключаются только при пода¬че синхронизирующих импульсов, а момент перехода связан с определенным уровнем синхросигнала (статические триггеры) или с моментом фронта либо среза синхро¬сигнала (динамические триггеры).

Триггер имеет два раздельных входа — R (установки нуля на выходе, Q = 0) и S (установки 1 на выходе, Q = 1) и два выхода — прямой Q и ин¬версный Q

| S | R | $Q^{t+1}$ |

|---|---|-----------|

| 0 | 0 | $Q^t$     |

| 0 | 1 | 1         |

| 1 | 0 | 0         |

| 1 | 1 | -         |

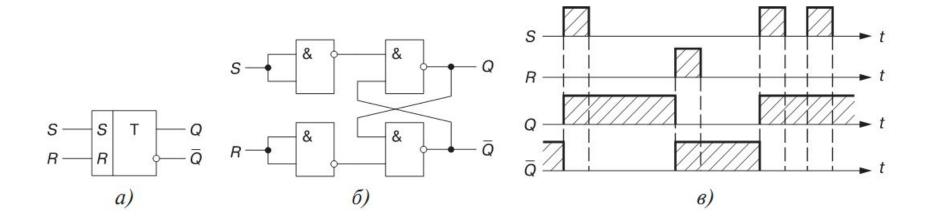

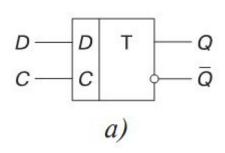

#### Цифровые устройства. Триггеры. D-Триггер

Триггер задержки (*D*-триггер) имеет один информационный *D*-вход и тактовый *C* вход.

| $C^t$ | $D^t$ | $Q^t$ | $Q^{t+1}$ |

|-------|-------|-------|-----------|

| 0     | 0     | 0     | 0         |

| 0     | 0     | 1     | 1         |

| 0     | 1     | 0     | 0         |

| 0     | 1     | 1     | 1         |

| 1     | 0     | 0     | 0         |

| 1     | 0     | 1     | 0         |

| 1     | 1     | 0     | 1         |

| 1     | 1     | 1     | 1         |

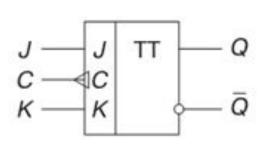

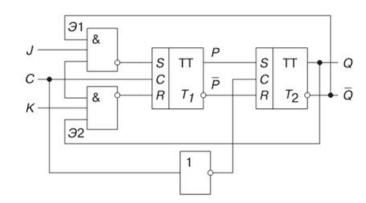

### Цифровые устройства. Триггеры. ЈК-триггеры

*JK-*триггер имеет информационные входы *J* и K, при J = 1, K = 0 триггер по тактовому импульсу С устанавливается в состояние Q = 1; при J = 0, K = 1 — переключается в состояние Q = 0, а при J = K = 0 — хранит ранее принятую информацию. Одновременное присутствие логических 1 на информационных входах не является для ЈК-триггера запрещенной комбинацией; при J = K = 1 триггер работает в счетном режиме, т. е. переключается каждым такто вым импульсом на входе С.

| K <sup>t</sup> | $Q^t$                 | $Q^{t+1}$             |

|----------------|-----------------------|-----------------------|

| 0              | 0                     | 0                     |

| 0              | 0                     | 1                     |

| 1              | 0                     | 0                     |

| 1              | 0                     | 1                     |

| 0              | 1                     | 1                     |

| 0              | 1                     | 1                     |

| 1              | 1                     | 0                     |

| 1              | 1                     | 0                     |

|                | 0<br>0<br>1<br>1<br>0 | 0 0 0 0 1 0 1 0 1 0 1 |

#### Цифровые устройства. Счетчики

Счётчик предназначен для счёта поступающих на его вход импульсов, в интервале между которыми он должен хранить информацию об их количестве.

Поэтому счётчик состоит из запоминающих ячеек — триггеров обычно D или JK типа.

Каждому числу импульсов соответствовали состояния 1 или 0 определенных ячеек. При этом совокупность единиц и нулей на выходах п ячеек, называемых разрядами счетчика, представляет собой п-разрядное двоичное число, которое однозначно определяет количество прошедших через входы импульсов.

#### Основные понятия