Память

Memory

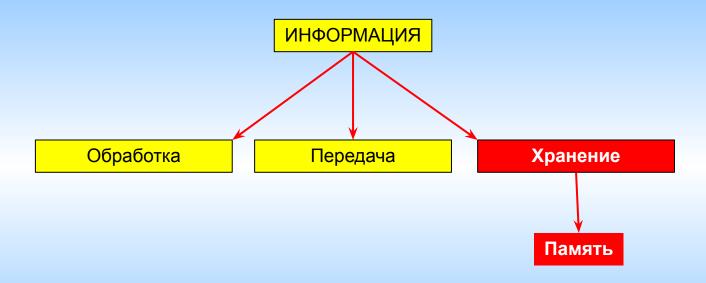

# Информация

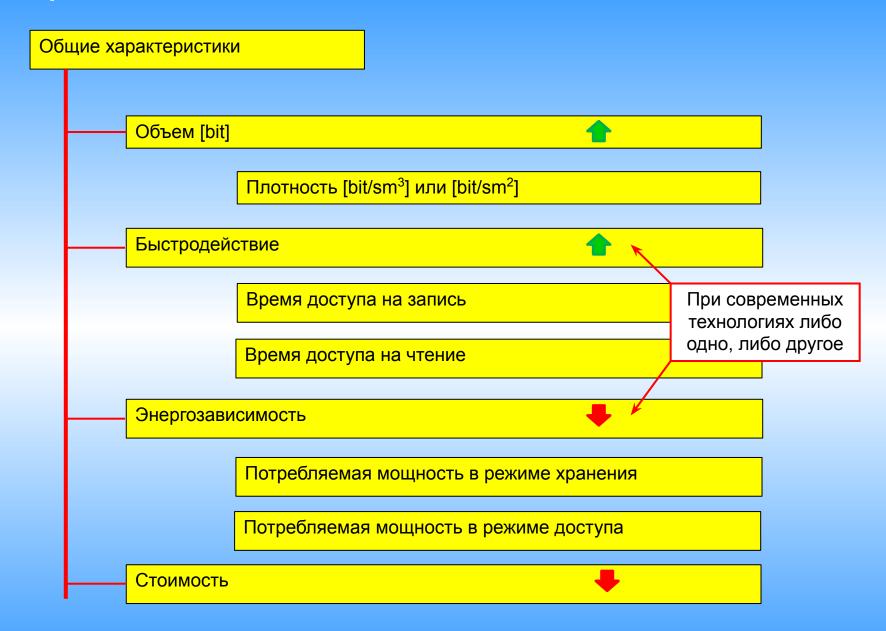

#### Характеристики памяти

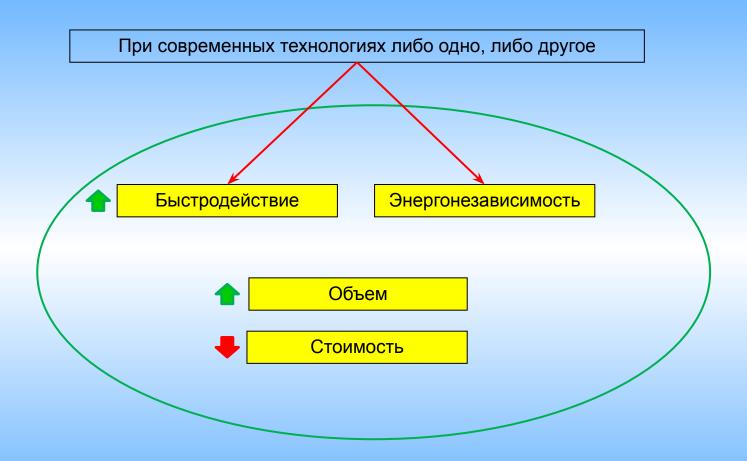

# Идеальная (универсальная) память

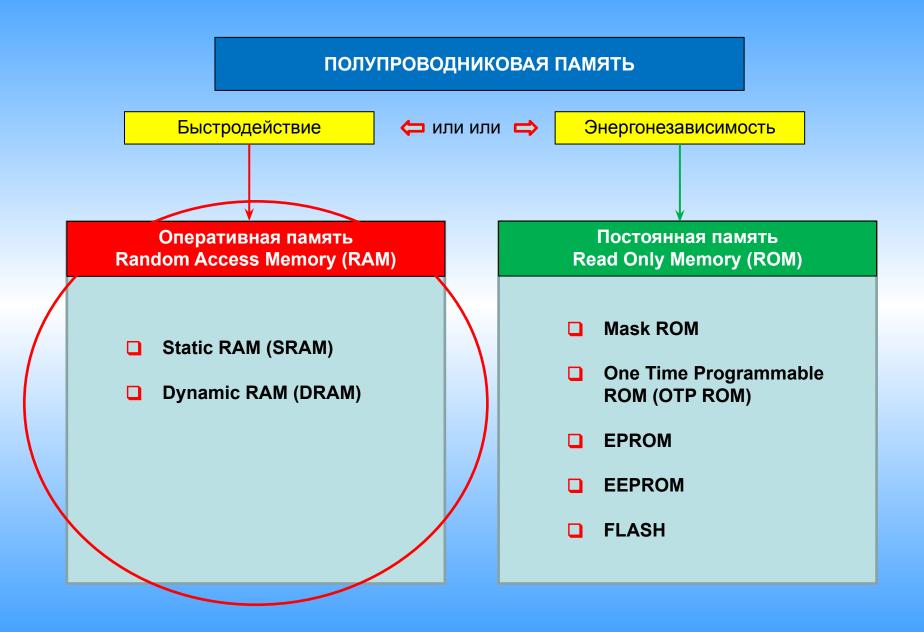

## Полупроводниковая память

## Структура памяти

Контроль доступа Access Control

> Последовательный доступ Sequential Access (SAM)

Произвольный доступ Random Access (RAM)

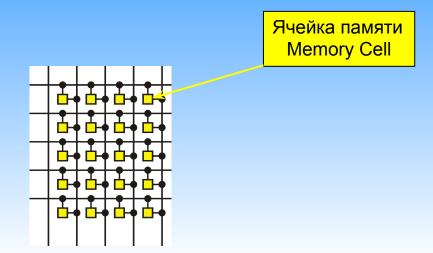

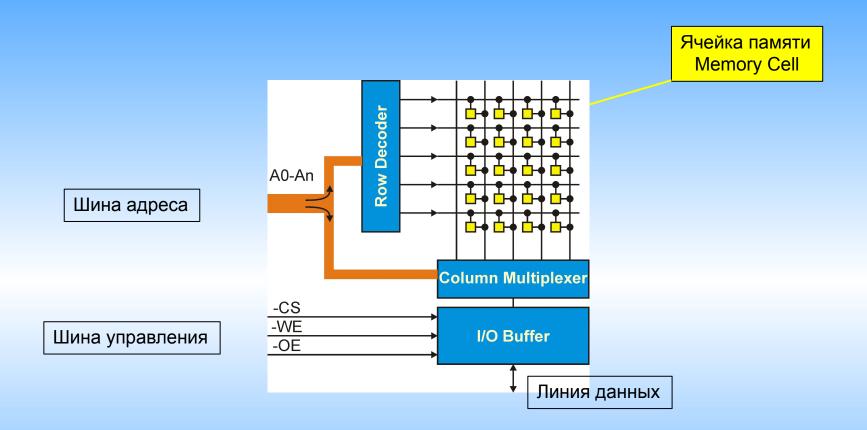

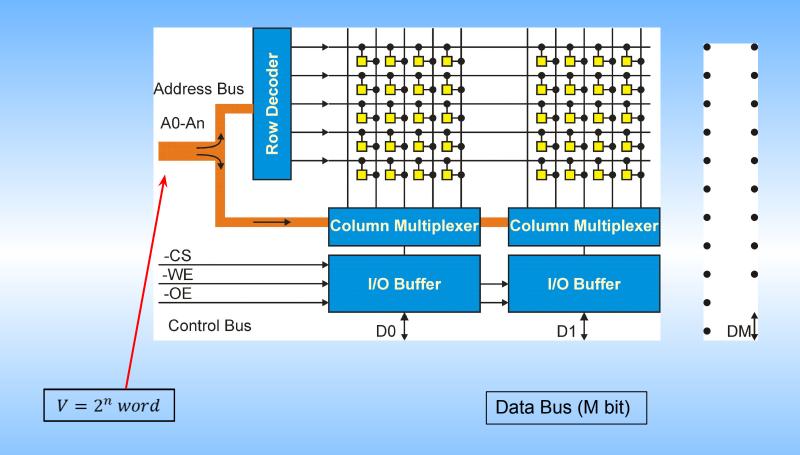

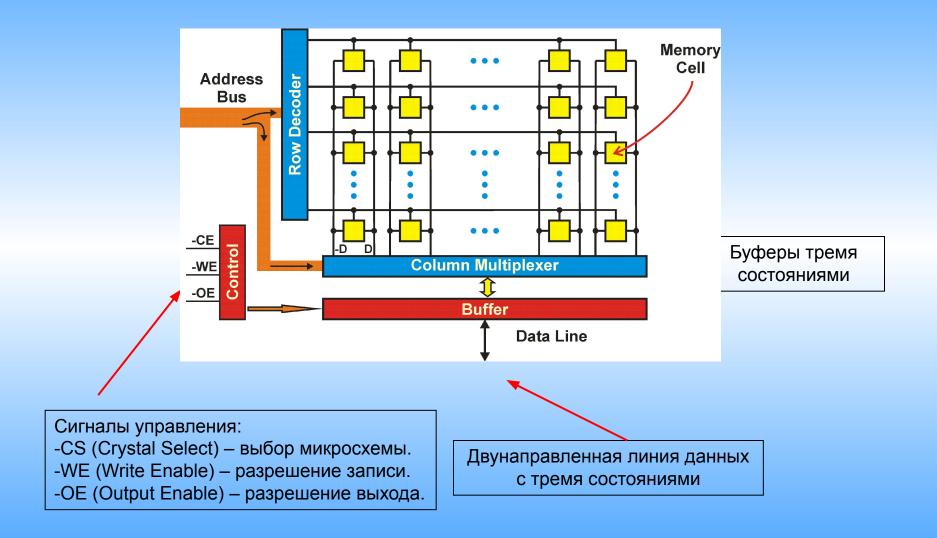

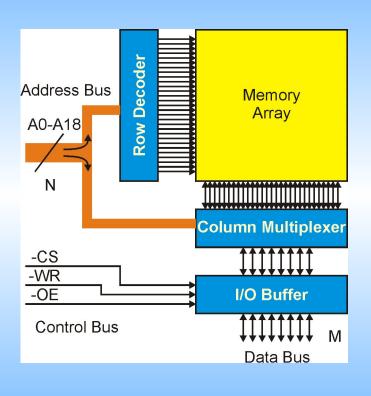

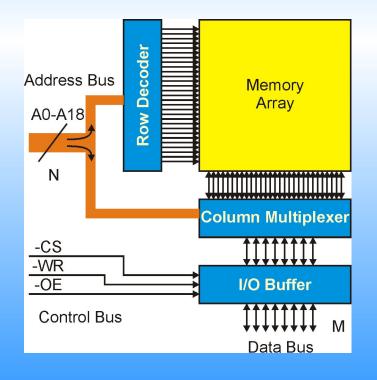

# Структура памяти с произвольным доступом

## Структура памяти с произвольным доступом

## Структура памяти с произвольным доступом

$$V[bit] = 2^n \times M$$

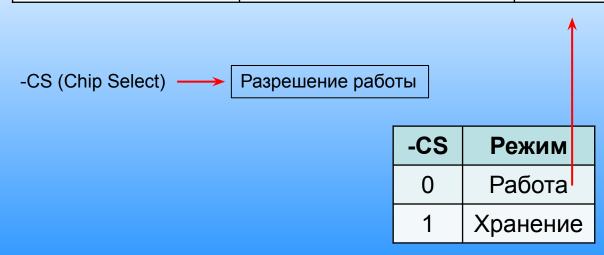

## Шина управления

**Control Bus**

| -WR (Write) | -OE (Output Enable) | Операция               |

|-------------|---------------------|------------------------|

| 1           | 1                   | Хранение               |

| 0           | 1                   | Запись                 |

| 1           | 0                   | Чтение                 |

| 0           | 0                   | Запрещенная комбинация |

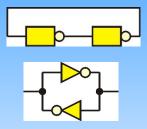

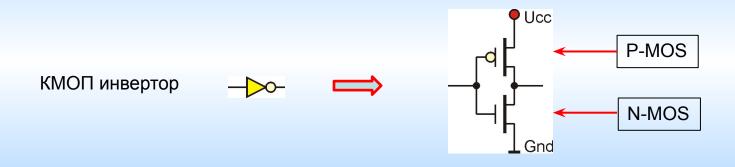

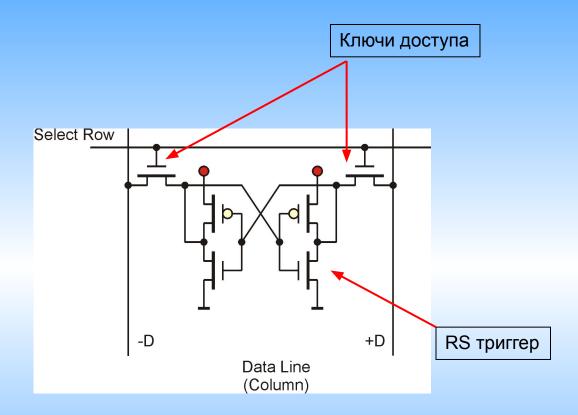

## Ячейки памяти SRAM

#### **SRAM Memory Cell**

RS триггер - простейшая запоминающая ячейка

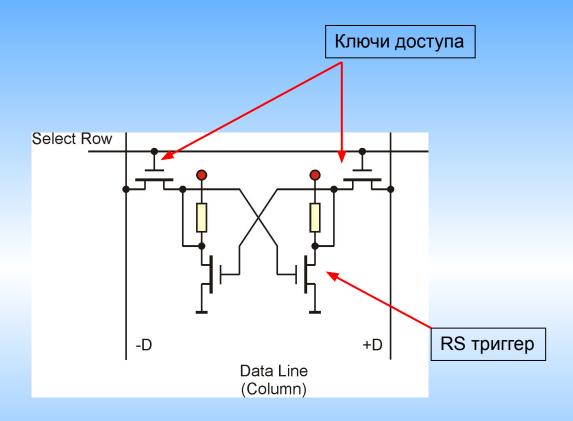

## Ячейки памяти SRAM

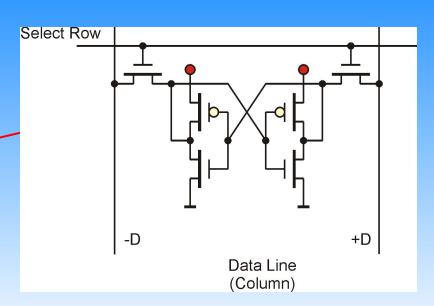

## 6-и транзисторная ячейка статической памяти SRAM

## Ячейки памяти SRAM

## 4-х транзисторная ячейка статической памяти SRAM

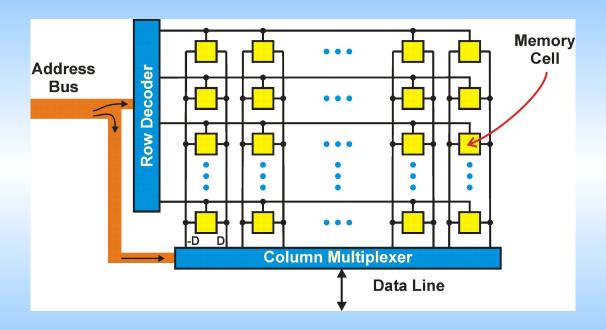

## SRAM

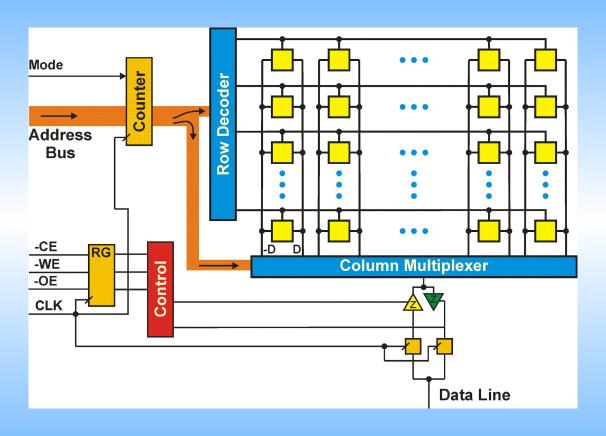

## Матричная организация ячеек памяти с произвольным доступом

# SRAM

## ПРИМЕР: 4Mb асинхронная SRAM GS74108 с организацией 512Кх8

#### **Features**

- Fast access time: 7, 8, 10, 12 ns

- CMOS low power operation: 135/120/95/85 mA at minimum cycle time

- Single 3.3 V power supply

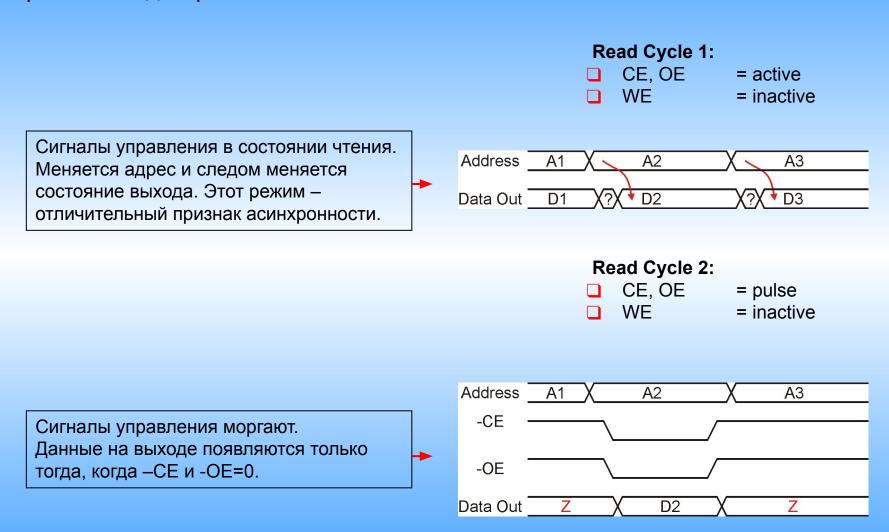

ПРИМЕР: 4Mb асинхронная SRAM GS74108 с организацией 512Кх8. Временные диаграммы. Чтение.

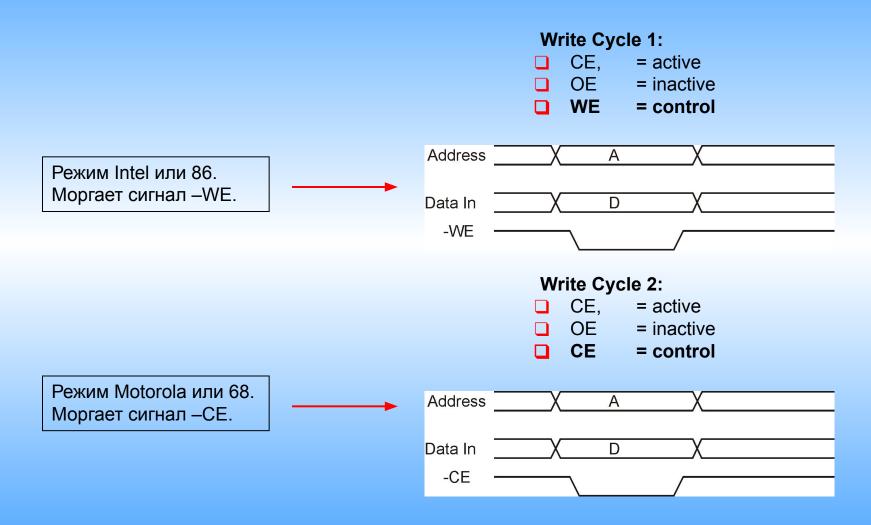

ПРИМЕР: 4Mb асинхронная SRAM GS74108 с организацией 512Кх8. Временные диаграммы. Запись.

ПРИМЕР: 4Mb асинхронная SRAM GS74108 с организацией 512Кх8. Временные диаграммы. Запись.

При записи необходимо всегда моргать либо –CE либо –WE.

#### Вопрос:

Почему нельзя использовать режим с удержанием –СЕ и –WE в состоянии записи и перебирая адреса записывать информацию?

Такой режим чтения – возможен!

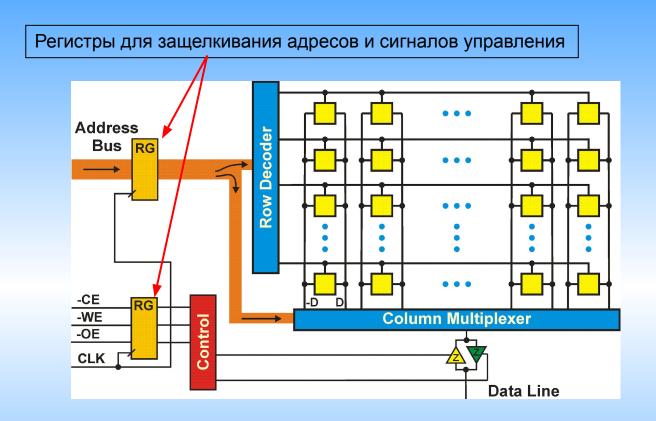

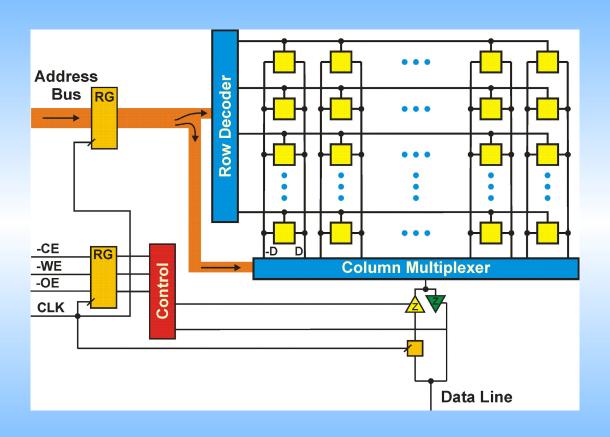

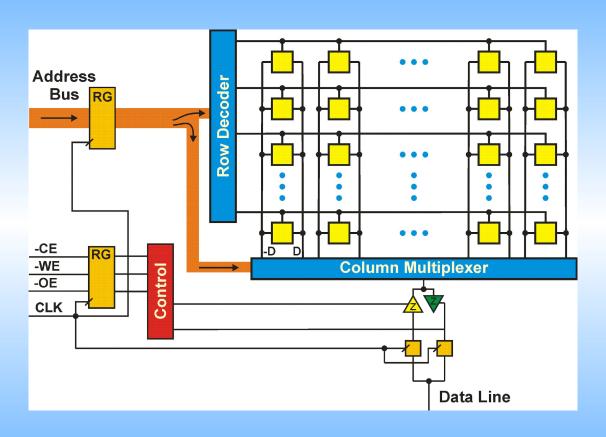

На шину данных тоже ставятся регистры. Возможно два варианта.

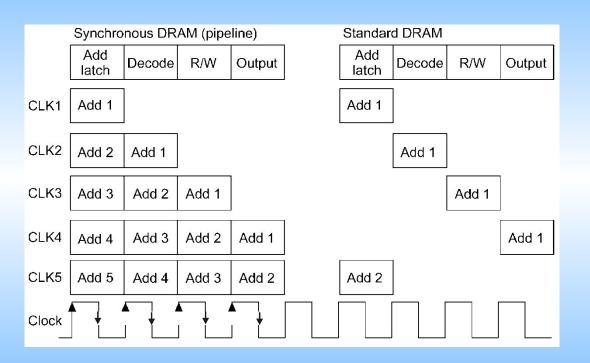

## Flow-through (F/T) Synchronous SRAM

## Pipelined (P/L) Synchronous SRAM

## **BURST SRAM**

## Ограничения SRAM

- Большая ячейка памяти: 6 транзисторов.

- Мало ячеек на кристалле.

- Большая цена кристалла.

- Большое количество выводов. Для 1 мегабайтной памяти уже необходимо 20 линий адреса.

- Большая цена корпуса.

#### Задача:

- 1. Уменьшить размеры ячейки памяти.

- 2. Сделать интерфейс с мультиплексированием.

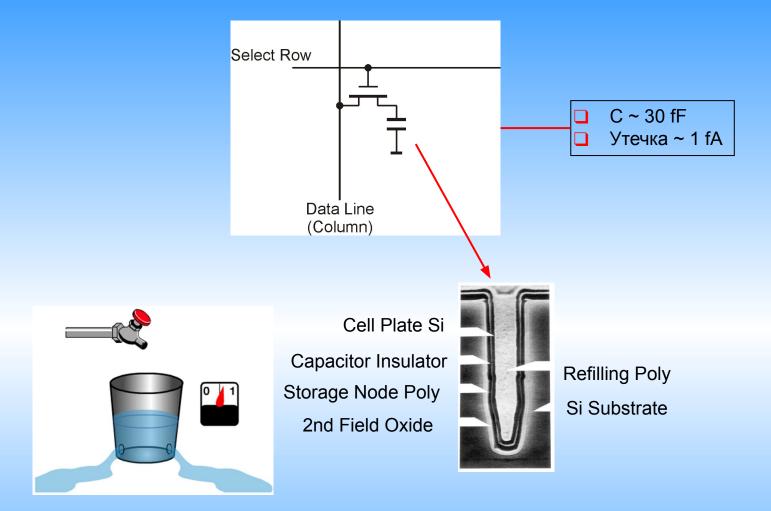

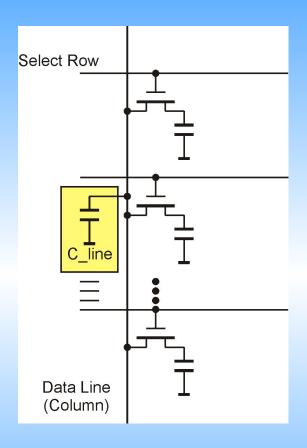

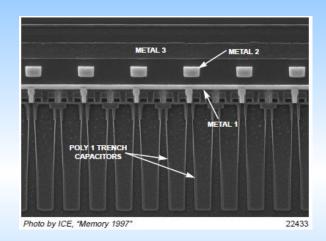

#### Ячейка DRAM

Ячейка динамической памяти:

- Достоинство простота

- □ Недостаток время хранения заряда на конденсаторе менее 100 мс

Как почувствовать заряд заряжена ли емкость в ячейке памяти?

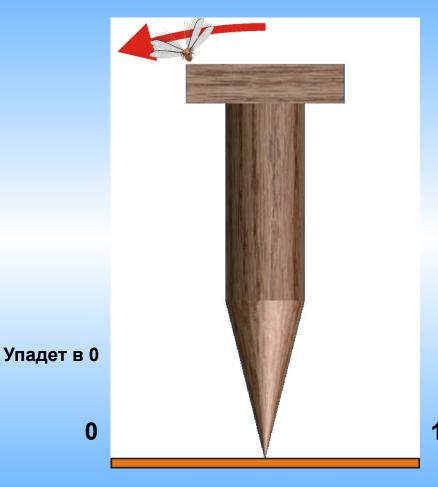

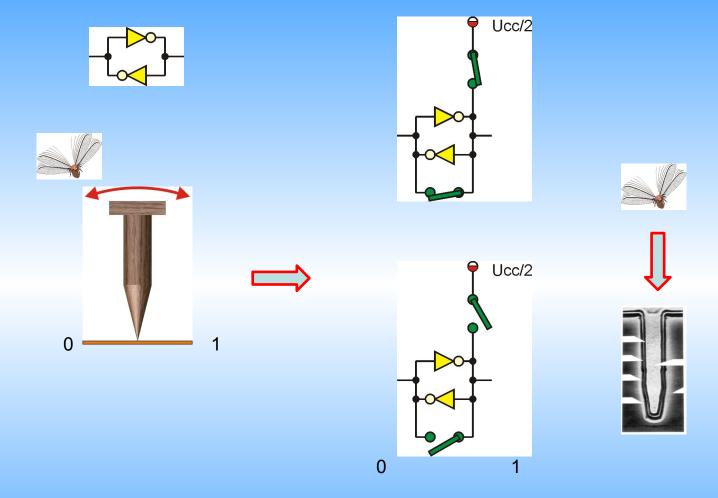

Аналогия с неустойчивым равновесием

Куда упадет?

Два устойчивых состояния

Аналогия с неустойчивым равновесием

#### Очень маленькое воздействие приносит определенность

Два устойчивых состояния

#### Аналогия с неустойчивым равновесием

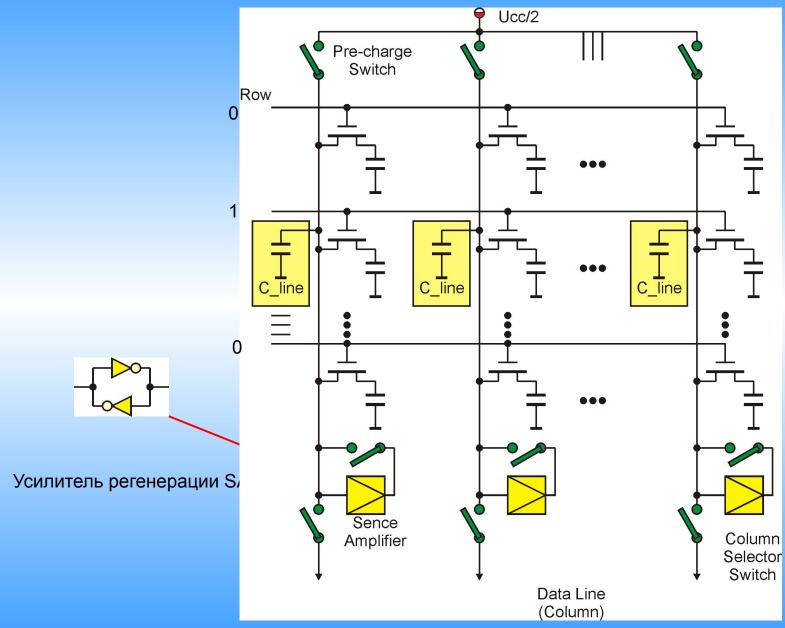

## Схема чтения-регенерации DRAM

При выборе строки происходит регенерация всех ячеек, подключенных к выбранной строке.

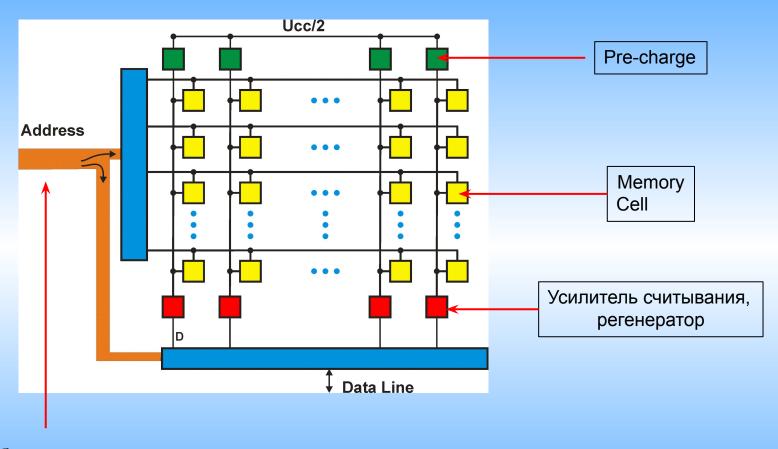

# Матрица DRAM

Необходимо уменьшить количество выводов

## Интерфейс DRAM

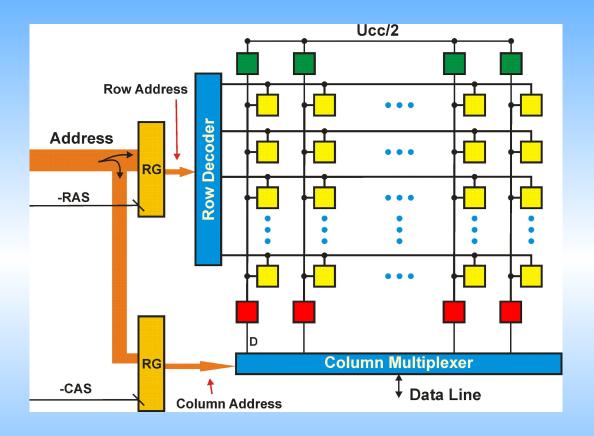

## Мультиплексирование адресов строки и колонки

20 адресных линий обеспечивают доступ к 64G ячейкам DRAM! У SRAM только 1М.

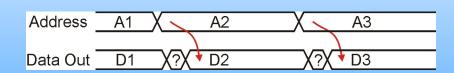

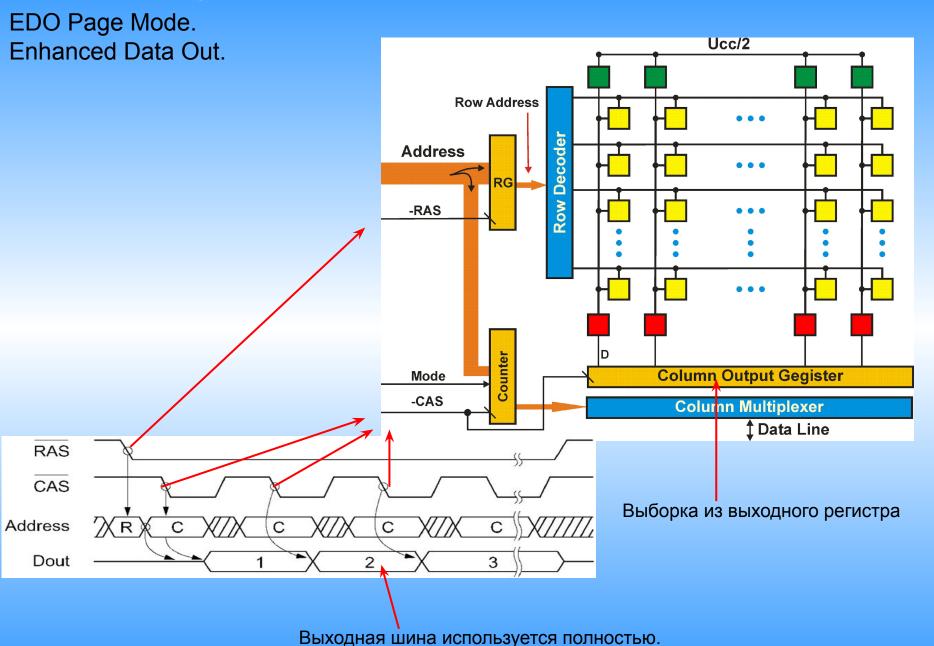

Нормальный режим. Ucc/2 Доступ по произвольному адрест **Row Address** Decoder **Address** RG Row -RAS **Column Multiplexer** -CAS **Data Line Column Address** RAS Normal Mode Для передачи полного адреса требуется 2 такта. CAS /X R X C X/ Address R: Row address Dout C: Column address Как уменьшить время доступа?

Режим быстрого доступа внутри строки. Fast Page Mode. Ucc/2 **Row Address Address** RG Row -RAS **Column Multiplexer** -CAS **Data Line Column Address** RAS Вначале полный доступ по произвольному адресу. CAS Затем доступ внутри строки за 1 такт. Address Dout

Fast Page Mode Mode

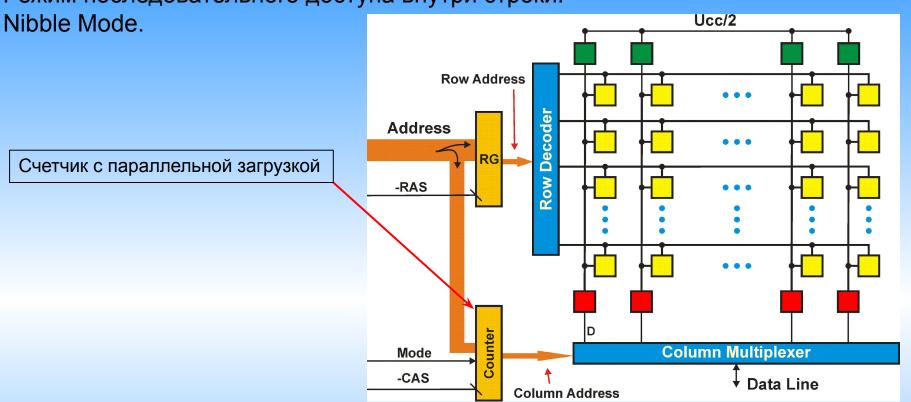

Если упорядочить информацию внутри строки, то можно отказаться от передачи адреса.

Режим последовательного доступа внутри строки.

Режим последовательного доступа внутри строки. Ucc/2 Nibble Mode. **Row Address** Decoder **Address** RG Row -RAS Column Multiplexer Mode -CAS **Data Line Column Address** RAS CAS Вначале полный доступ по R) Address произвольному адресу. Dout Затем доступ внутри строки за 1 такт.

Выходная шина простаивает значительную часть времени.

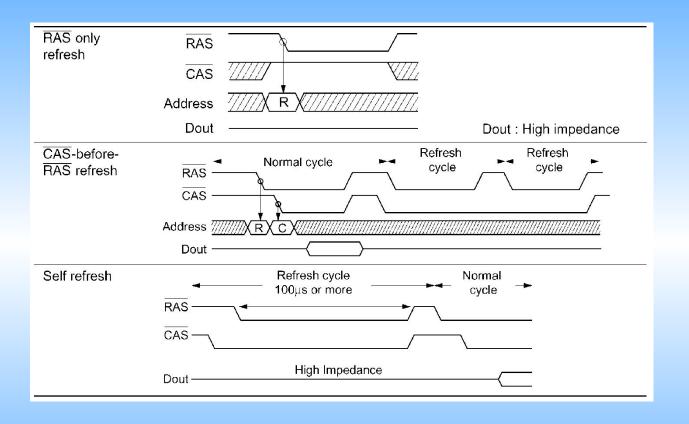

## Основные способы регенерации DRAM

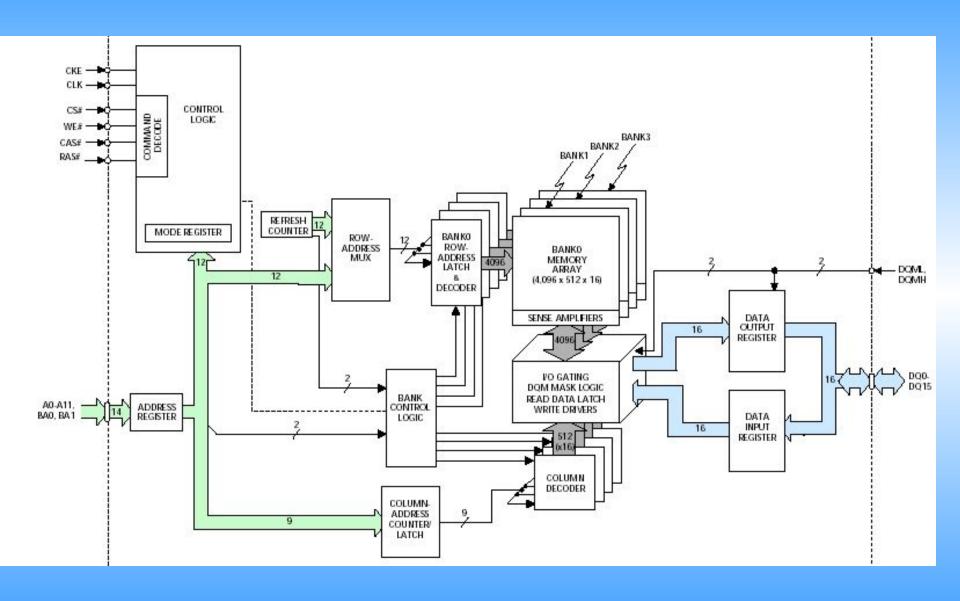

## SDRAM

## Конвейер