# Logical foundations of system devices. Logic gates. Adders.

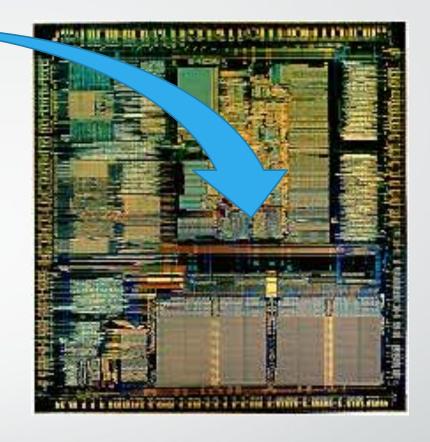

solve logistics problems at an elementary level know that the CPU is made up from logic gates

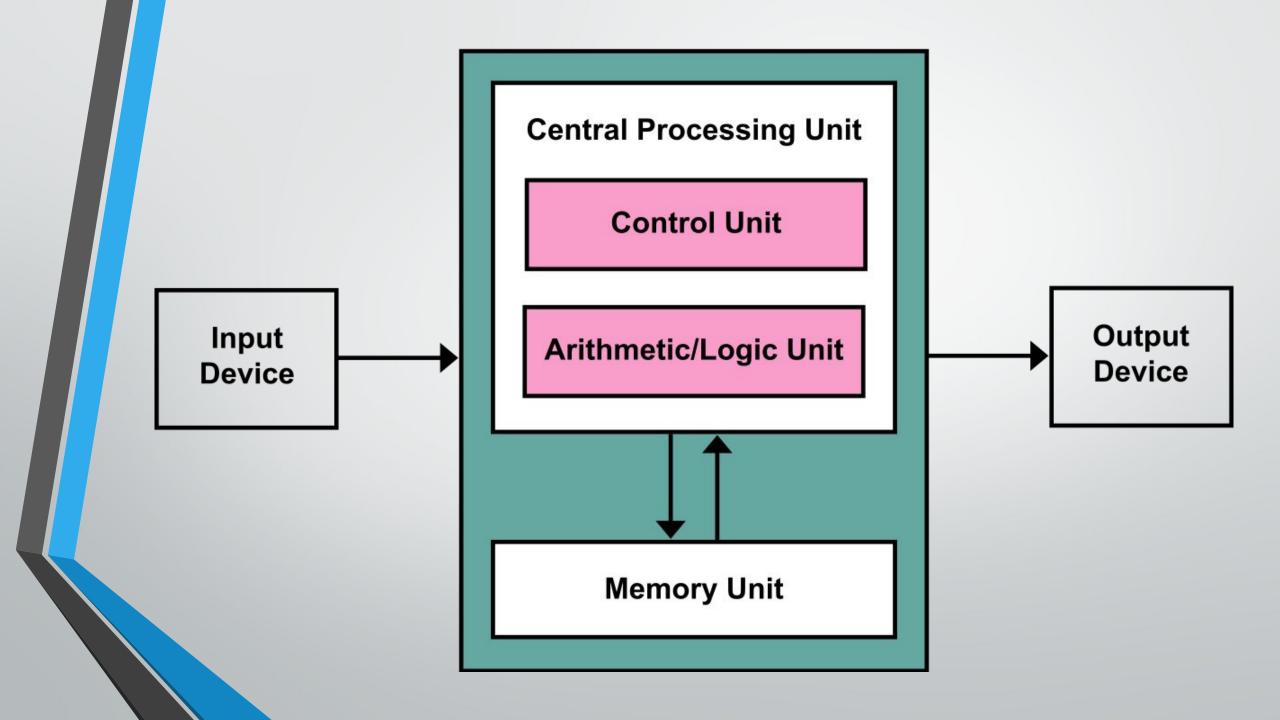

What is von Neumann architecture?

What does the microprocessor include?

What are the functions of the ALU?

An arithmetic logic unit (ALU) is a <u>combinational digital</u> <u>electronic circuit</u> that performs <u>arithmetic</u> and <u>bitwise</u> <u>operations</u> on <u>integer binary numbers</u>.

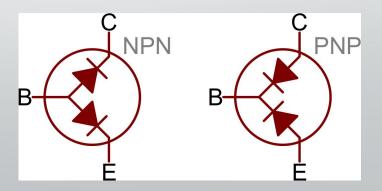

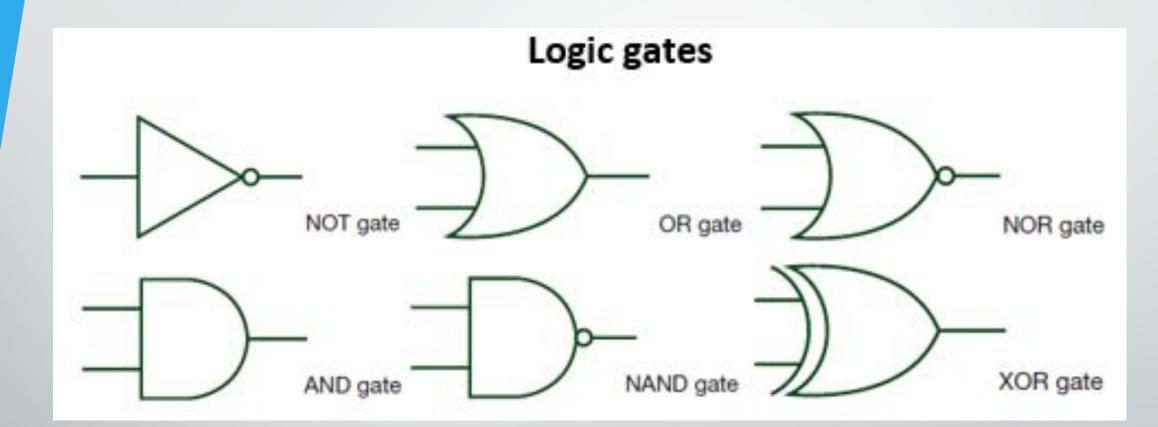

Logic gates are primarily implemented using diodes or transistors acting as electronic switches

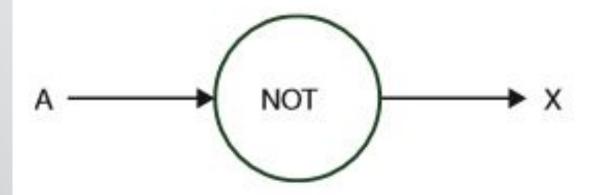

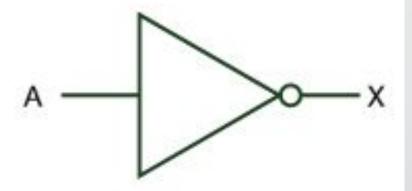

## NOT gate

The output (X) is true (i.e. 1 or ON) if:

INPUT A is NOT TRUE (i.e. 0 or OFF)

Truth table for: X = NOT A

| INPUT A | OUTPUT X |

|---------|----------|

| 0       | 1        |

| 1       | 0        |

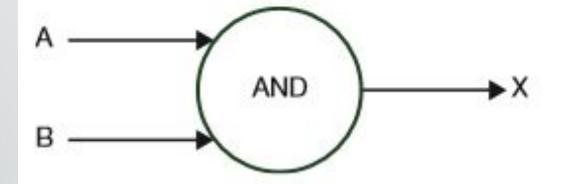

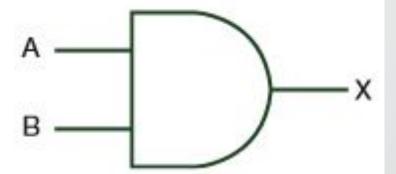

## AND gate

The output (X) is true (i.e. 1 or ON) if:

INPUT A AND INPUT B are BOTH TRUE (i.e. 1 or ON)

Truth table for: X = A AND B

| INPUT A | INPUT B | OUTPUT X |  |

|---------|---------|----------|--|

| 0       | 0       | 0        |  |

| 0       | 1       | 0        |  |

| 1       | 0       | 0        |  |

| 1       | 1       | 1        |  |

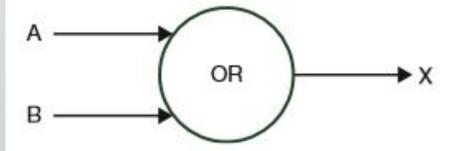

The output (X) is true (i.e. 1 or ON) if:

INPUT A OR INPUT B is TRUE (i.e. 1 or ON)

Truth table for: X = A OR B

| INPUT A | INPUT B | OUTPUT X |  |

|---------|---------|----------|--|

| 0       | 0       | 0        |  |

| 0       | 1       | 1        |  |

| 1       | 0       | 1        |  |

| 1       | 1       | 1        |  |

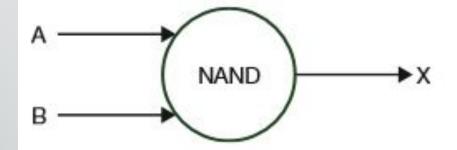

## NAND gate

The output (X) is true (i.e. 1 or ON) if:

INPUT A AND INPUT B are NOT BOTH TRUE (i.e. 1 or ON)

Truth table for: X = NOT A AND B

| INPUT A | INPUT B | OUTPUT X |

|---------|---------|----------|

| 0       | 0       | 1        |

| 0       | 1       | 1        |

| 1       | 0       | 1        |

| 1       | 1       | 0        |

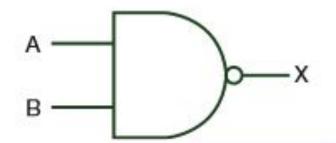

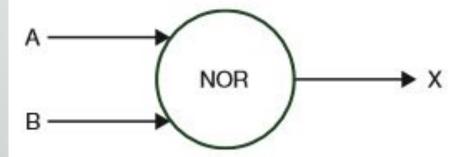

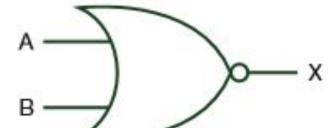

## NOR gate

The output (X) is true (i.e. 1 or ON) if:

INPUT A OR INPUT B are NOT BOTH TRUE (i.e. 1 or ON)

Truth table for: X = NOT A OR B

| INPUT A | INPUT A INPUT B |   |

|---------|-----------------|---|

| 0       | 0               | 1 |

| 0       | 1               | 0 |

| 1       | 0               | 0 |

| 1       | 1               | 0 |

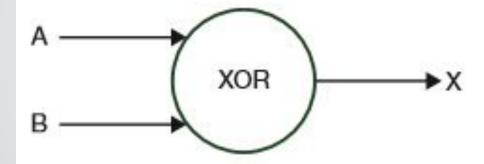

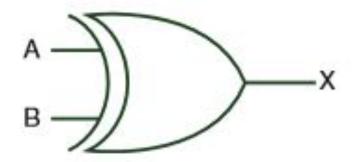

## XOR gate

The output (X) is true (i.e. 1 or ON) if:

INPUT A OR (NOT INPUT B) OR (NOT INPUT A) OR INPUT B

is TRUE (i.e. 1 or ON)

Truth table for: X = A OR (NOT B) OR (NOT A) OR B

| INPUT A | INPUT B | OUTPUT X |

|---------|---------|----------|

| 0       | 0       | 0        |

| 0       | 1       | 1        |

| 1       | 0       | 1        |

| 1       | 1       | 0        |

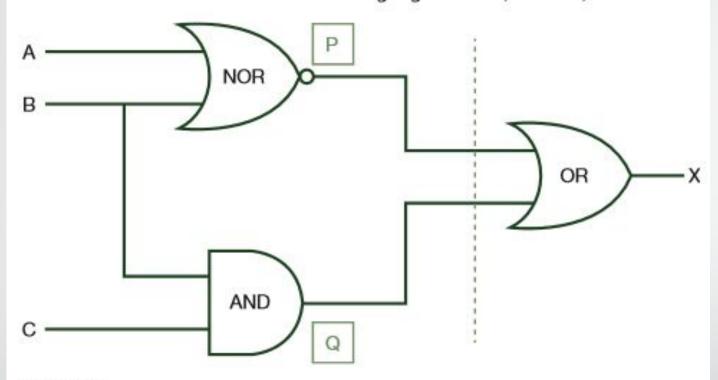

#### Example 1

Produce a truth table from the following logic circuit (network).

#### First part

There are 3 inputs; thus we must have 2<sup>3</sup> (i.e. 8) possible combinations of 1s and 0s.

To find the values (outputs) at points P and Q, it is necessary to consider the truth tables for the NOR gate (output P) and the AND gate (output Q) i.e.

$$P = A NOR B$$

$Q = B AND C$

#### We thus get:

| INPUT A | INPUT B | INPUT C | OUTPUT P | OUTPUT Q |

|---------|---------|---------|----------|----------|

| 0       | 0       | 0       | 1        | 0        |

| 0       | 0       | 1       | 1        | 0        |

| 0       | 1       | 0       | 0        | 0        |

| 0       | 1       | 1       | 0        | 1        |

| 1       | 0       | 0 0     |          | 0        |

| 1       | 0       | 1       | 0        | 0        |

| 1 1 0   |         | 0       | 0        |          |

| 1       | 1       | 1       | 0        | 1        |

#### Second part

There are 8 values from P and Q which form the inputs to the last OR gate. Hence we get X = P OR Q which gives the following truth table:

| INPUT P | INPUT Q | OUTPUT X |  |

|---------|---------|----------|--|

| 1       | 0       | 1        |  |

| 1       | 0       | 1        |  |

| 0       | 0       | 0        |  |

| 0       | 1       | 1        |  |

| 0       | 0       | 0        |  |

| 0       | 0       | 0        |  |

| 0       | 0       | 0        |  |

| 0       | 1       | 1        |  |

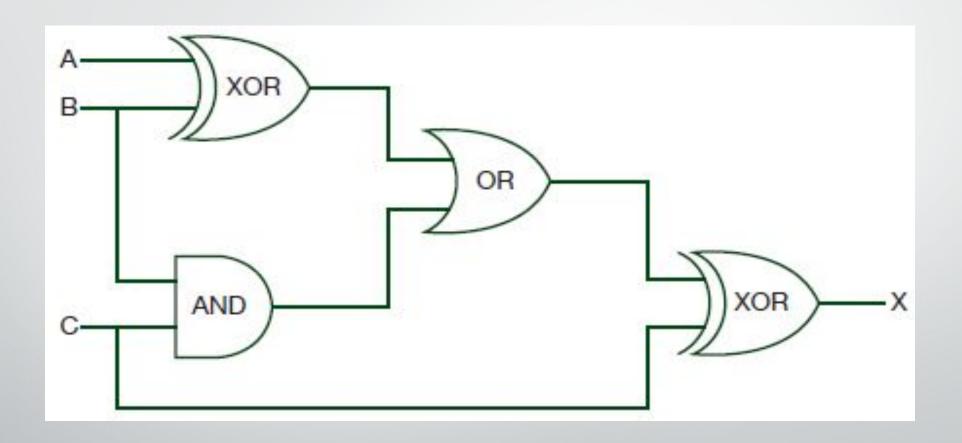

# Example 2

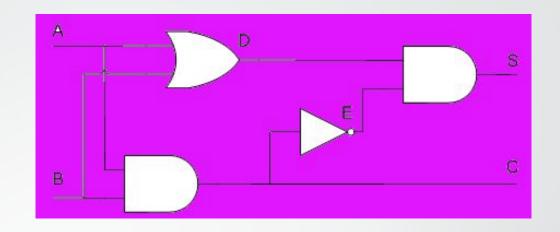

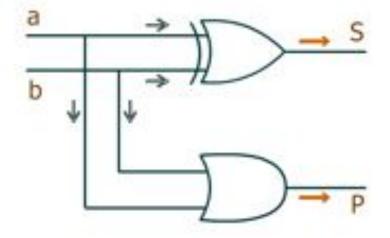

# Half-Adder

• What is the output of this circuit?

| А | В | D | E | S | С |

|---|---|---|---|---|---|

| 0 | 0 |   |   |   |   |

| 0 | 1 |   |   |   |   |

| 1 | 0 |   |   |   |   |

| 1 | 1 |   |   |   |   |

This circuit performs binary addition (C = carry)

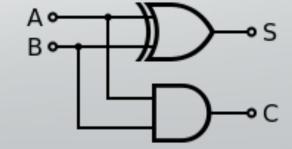

• It also has a simpler equivalent:

## Схема полусумматора

- а первое слагаемое

- второе слагаемое

- S сумна разряда

- Р перенос в следующий разряд

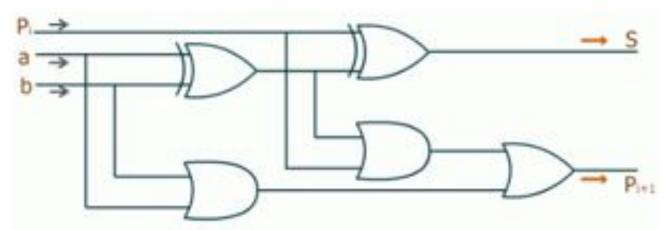

### Схема сумматора

- а первое слагаеное

- в второе слагаеное

- S сунна разряда

- Р: перенос из младшего разряда

- Рі+1 перенос в старший разряд