### Национальный исследовательский университет «МИЭТ»

# Курс «Проектирование библиотечных элементов»

Ст. преподаватель каф. ПКИМС: Коршунов Андрей Владимирович

Лекция 1. Вводная.

#### Организация курса:

- 16 лекций

- 8 лабораторных работ

- курсовой проект (диф. зачет)

- экзамен

## Литература

- R.J. Baker, H.W. Li, D.E. Boyce. CMOS. Circuit design, Layout, and Simulation (2<sup>nd</sup> Edition), 2005. 1038p.

- J.P. Uyemura. CMOS Logic Circuit Design. Kluwer Academic Publishers, 1999. 528p.

- J.H. Stephen. High-Speed Digital System Design, 2000. 347p.

- S.M. Kang, Y. Leblebici. CMOS Digital Integrated Circuits: Analysis and Design (3<sup>rd</sup> Edition), McGraw Hill, 2002. 1008p.

- M.Rabaey, A. Chandrakasan, B. Nikolic. Digital Integrated Circuits (2<sup>nd</sup> Edition). Prentice Hall, 2002. 761p.

- S. Dabral. Basic ESD and I/O Design, 1998. 328p.

## Литература (дополнительная)

- A.P. Chandrakasan and R.W. Brodersen. Low Power Digital CMOS Design. Kluwer Academic Publishers, 1995. 428p.

- Neil H.E. Weste, K.Eshraghian. Principles of CMOS VLSI Design (2<sup>nd</sup> Edition). Addison Wesley. 1994. 735p.

- D.A. Hodges, H.G. Jakcson, R.S. David. Analysis and Design of Digital Integrated circuits. McGraw-Hill Science (3<sup>rd</sup> Edition). 2003. 600p.

- B. Razavi. Design of Analog CMOS Integrated Circuits. 2000. 684p.

- Киносита К., Асада К., Карацу О. Логическое проектирование СБИС. 1988

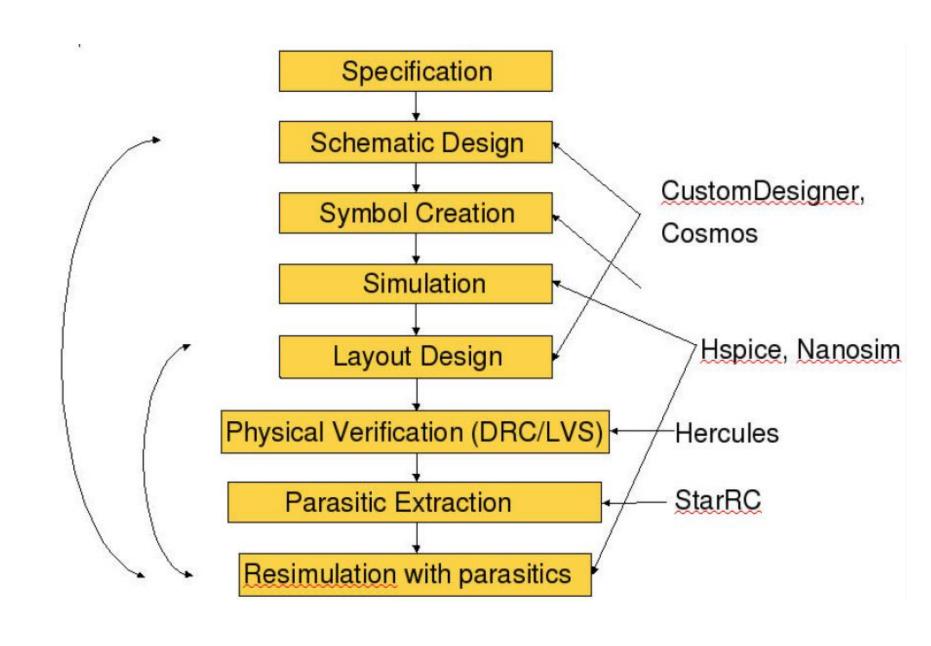

#### Разработка библиотечных элементов

- Полностью заказная схема

- Создание электрической схемы

- Характеризация

- Создание топологии

- Экстракция паразитных составляющих

- Окончательная характеризация

#### Порядок работы в HSPICE

- Создаем текстовый файл с описание схемы на языке SPICE

- Запускаем симулятор:

hspice my\_scheme.spi

- Исправляем ошибки (должно быть сообщение job concluded)

- Два варианта вывода результатов (консоль и визулизатор)

```

*первая строка не считывается

*строки со звездочкой - комментарий

***подключение параметров модели

*** prot - подавление вывода значений

** параметров в консоль

.prot

.lib './SAED 90nm.lib' TT 12

.unprot

** директивы начинаются с точки!

** в одном файле несколько вариантов

** параметров в зависимости от PVT - обычно

** используем ТТ 12

```

```

*** описание схемы

MM1 GND IN ZN GND N12 L=0.1U W=0.24U

MM2 VDD IN ZN VDD P12 L=0.1U W=0.48U

** полевой транзистор

*** М<уникальное имя> С З И П <тип модели>

*** <дополнительные параметры>

*тип модели n12 или p12 (либо n12 lvt и т.п.)

*дополнительные параметры обычно L W

*узлы подключения выводов - произвольные

* Допустимо ММЗ 1 2 3 4 N12 L=0.1U W=0.24U

```

```

*** параметры - произвольные переменные

.param\ vdd = 1

** vdd здесь название параметра, а не узел

* безразмерные величины

* используем приставки:

u - микро 10<sup>-6</sup>

n - нано 10^{\Lambda} - 9

р - пико 10^-12

f - \phi e m T o 10^-15

m - милли 10<sup>-3</sup>

k - кило 10<sup>3</sup>

MEG (или x) - мега 10^6

q - гига 10<sup>9</sup>

```

```

*** источник питания

vdd vdd gnd vdd

** источник постоянного напряжения

*** V<уникальное_имя> pin1 pin2 <значение>

*** все три слова vdd значат разное!!!

***входной сигнал

vin in 0

```

- \* Значение указывать необязательно

- \* Зададим в параметрах анализа

```

*** моделирование по постоянному току

.dc vin 0 vdd 0.01

*** .dc - ключевой слово

*** имя источника, который будет изменяться

*** диапазон изменения

*** шаг

*** расчет параметров и вывод их значений

** в консоль

.meas dc vthr in z find v(in) when

v(in) = v(zn)

** .meas или .measure - ключевой слово

** тип анализа при котором будет

** производиться расчет

```

```

* .meas dc vthr_in_z find v(in) when

v(in)=v(zn)

** произвольное уникальное имя величины

** find <что требуется найти>

** when <в какой момент>

** в конце любого файла

.end

```

# \*\* библиотека

```

.lib './SAED 90nm.lib' TT 12

*** описание схемы

MM1 GND IN ZN GND N12 L=0.1U W=0.24U

MM2 VDD IN ZN VDD P12 L=0.1U W=0.48U

*** параметры - произвольные переменные

.param vdd = 1

*** источник питания

vdd vdd gnd vdd

***входной сигнал

vin in 0

*** моделирование по постоянному току

.dc vin 0 vdd 0.01

** в консоль

.meas dc vthr in z find v(in) when v(in)=v(z)

.option post probe

.end

```

#### Типы файлов

input netlist .sp

design .cfg

configuration

Output (X is alter number, usually 0)

(N is the statement number in one netlist, starting at 0).

graph data .trX (transient analysis)

.swX (dc sweep)

.acX (ac analysis)

.mtX (tran Measure)

.msX (dc Measure)

.maX (ac Measure)

.pwIN\_trX (from .STIM <TRAN> PWL)

.datN\_trX (from .STIM TRAN DATA)

.datN\_acX (from .STIM AC DATA)

.datN\_swX (from .STIM DC DATA)

.vecN\_trX (from .STIM <TRAN> VEC)

hardcopy data .grX (from .GRAPH)

```

*** моделирование во времени

.tran 1p 10n

*** сначала шаг, потом общее время

** при временном моделированиии лучше

* использовать параметры

.param tr = 50p

.param freq = 500meg

.param per = '1/freq'

.param\ vdd = 1

.param tst = '0.5*per'

* Тогда можно написать

* .tran '0.01*tr' '3*per'

```

```

*** источник входного сигнала - импульсный

vinin gndpulse 0 vdd tst tr tr '0.5*per-tr' per

*

*Pulse PULSE(V1 V2 TD TR TF PW PER)

*Examples:

* VIN 3 0 PULSE(-1 1 2NS 2NS 2NS 50NS 100NS)

* parameters default values units

* V1 (initial value) Volts or Amps

* V2 (pulsed value) Volts or Amps

* TD (delay time) 0.0 seconds

* TR (rise time) TSTEP seconds

* TF (fall time) TSTEP seconds

* PW (pulse width) TSTOP seconds

* PER(period) TSTOP seconds

```

```

*** основные измерения

* 1 - задержка - по уровню 0,5

.meas tran tplh in out trig v(in) val='0.5*vdd'

rise=1 targ v(out) val='0.5*vdd' fall=1

* 2 - величина фронта

.meas tran ttrlh in z trig v(z) val='0.1*vdd' rise=1

targ v(z) val='0.9*vdd' rise=1

*trig - начало измеряемого интервала

*targ - окончание

*rise=1 или fall=2 номер переключения

```