- Главная

- Информатика

- О развитии российских аппаратно-программных платформ и совместимого ПО

Содержание

- 2. Универсальные микропроцессоры «ЭЛЬБРУС» и МЦСТ-R МЦСТ R2000 28нм Эльбрус-8СВ 28нм Эльбрус-16С 16нм SPARC V9 OoO 64

- 3. Преимущества архитектуры Эльбрус Параллельная энергоэффективная архитектура 25 скалярных оп. за такт за счет явного параллелизма (микро)операций

- 4. Инфобез: Технология безопасных вычислений Защита от ошибок программиста: неинициализированные данные контроль границ объектов обращение к освобождённой

- 5. Эскиз плана освоения производства ф-ки Микрон 2022 2023 2024 2025 2026 90LP – quick win МЦСТ-R4М,

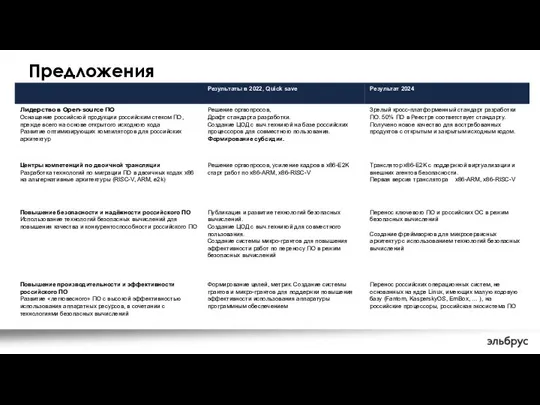

- 6. Предложения

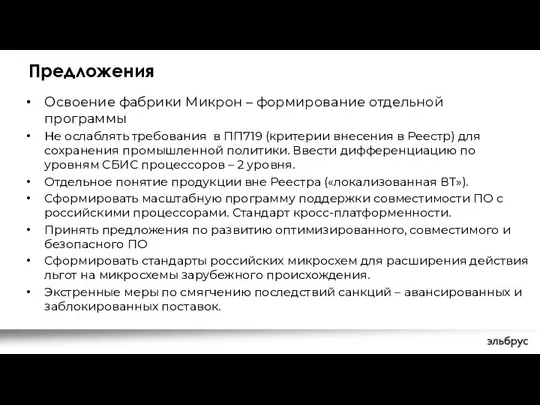

- 7. Предложения Освоение фабрики Микрон – формирование отдельной программы Не ослаблять требования в ПП719 (критерии внесения в

- 10. Скачать презентацию

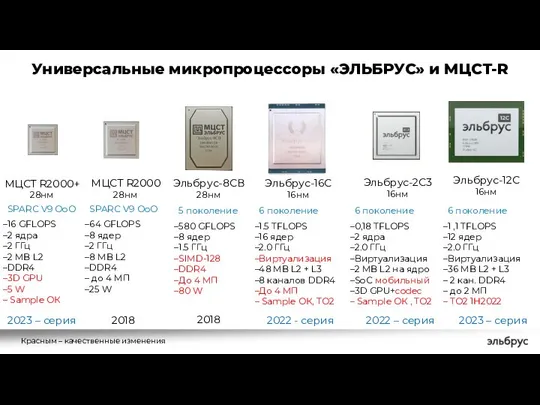

Универсальные микропроцессоры «ЭЛЬБРУС» и МЦСТ-R

МЦСТ R2000

28нм

Эльбрус-8СВ

28нм

Эльбрус-16С

16нм

SPARC V9 OoO

64 GFLOPS

8 ядер

2 ГГц

8

Универсальные микропроцессоры «ЭЛЬБРУС» и МЦСТ-R

МЦСТ R2000

28нм

Эльбрус-8СВ

28нм

Эльбрус-16С

16нм

SPARC V9 OoO

64 GFLOPS

8 ядер

2 ГГц

8

DDR4

до 4 МП

25 W

2018

5 поколение

580 GFLOPS

8 ядер

1.5 ГГц

SIMD-128

DDR4

До 4 МП

80 W

2018

6 поколение

1.5 TFLOPS

16 ядер

2.0 ГГц

Виртуализация

48 MB L2 + L3

8 каналов DDR4

До 4 МП

Sample ОК, TO2

2022 - серия

Красным – качественные изменения

2023 – серия

Эльбрус-12С

16нм

6 поколение

1 ,1 TFLOPS

12 ядер

2.0 ГГц

Виртуализация

36 MB L2 + L3

2 кан. DDR4

до 2 МП

TO2 1H2022

Эльбрус-2С3

16нм

6 поколение

0,18 TFLOPS

2 ядра

2.0 ГГц

Виртуализация

2 MB L2 на ядро

SoC мобильный

3D GPU+codec

Sample ОК , TO2

2022 – серия

МЦСТ R2000+

28нм

SPARC V9 OoO

16 GFLOPS

2 ядра

2 ГГц

2 MB L2

DDR4

3D GPU

5 W

Sample ОК

2023 – серия

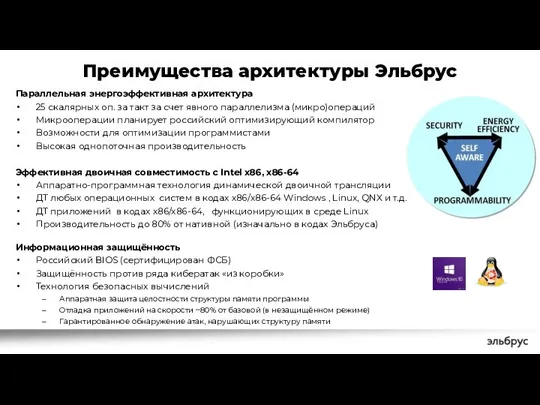

Преимущества архитектуры Эльбрус

Параллельная энергоэффективная архитектура

25 скалярных оп. за такт за

Преимущества архитектуры Эльбрус

Параллельная энергоэффективная архитектура

25 скалярных оп. за такт за

Микрооперации планирует российский оптимизирующий компилятор

Возможности для оптимизации программистами

Высокая однопоточная производительность

Эффективная двоичная совместимость с Intel x86, x86-64

Аппаратно-программная технология динамической двоичной трансляции

ДТ любых операционных систем в кодах х86/x86-64 Windows , Linux, QNX и т.д.

ДТ приложений в кодах x86/x86-64, функционирующих в среде Linux

Производительность до 80% от нативной (изначально в кодах Эльбруса)

Информационная защищённость

Российский BIOS (сертифицирован ФСБ)

Защищённость против ряда кибератак «из коробки»

Технология безопасных вычислений

Аппаратная защита целостности структуры памяти программы

Отладка приложений на скорости ~80% от базовой (в незащищённом режиме)

Гарантированное обнаружение атак, нарушающих структуру памяти

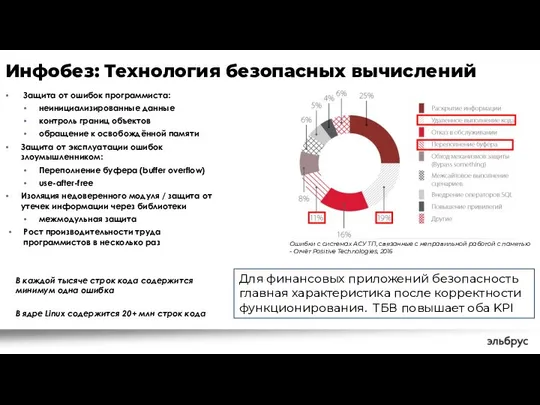

Инфобез: Технология безопасных вычислений

Защита от ошибок программиста:

неинициализированные данные

контроль границ

Инфобез: Технология безопасных вычислений

Защита от ошибок программиста:

неинициализированные данные

контроль границ

обращение к освобождённой памяти

Защита от эксплуатации ошибок злоумышленником:

Переполнение буфера (buffer overflow)

use-after-free

Изоляция недоверенного модуля / защита от утечек информации через библиотеки

межмодульная защита

Рост производительности труда программистов в несколько раз

В каждой тысяче строк кода содержится минимум одна ошибка

В ядре Linux содержится 20+ млн строк кода

Ошибки с системах АСУ ТП, связанные с неправильной работой с памятью

- Отчёт Positive Technologies, 2016

Для финансовых приложений безопасность

главная характеристика после корректности

функционирования. ТБВ повышает оба KPI

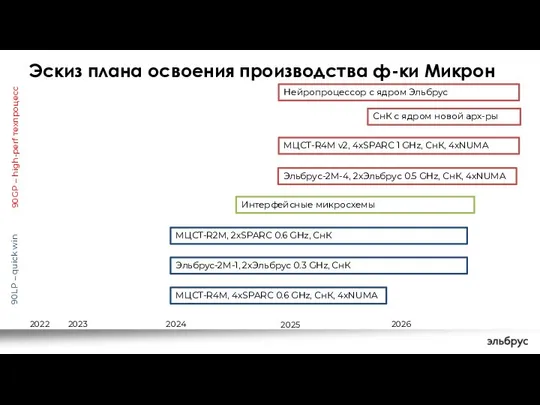

Эскиз плана освоения производства ф-ки Микрон

2022

2023

2024

2025

2026

90LP – quick win

МЦСТ-R4М, 4хSPARC 0.6

Эскиз плана освоения производства ф-ки Микрон

2022

2023

2024

2025

2026

90LP – quick win

МЦСТ-R4М, 4хSPARC 0.6

Эльбрус-2М-1, 2хЭльбрус 0.3 GHz, СнК

МЦСТ-R2М, 2хSPARC 0.6 GHz, СнК

90GP – high-perf техпроцесс

Эльбрус-2M-4, 2хЭльбрус 0.5 GHz, СнК, 4xNUMA

МЦСТ-R4М v2, 4хSPARC 1 GHz, СнК, 4xNUMA

Нейропроцессор с ядром Эльбрус

Интерфейсные микросхемы

СнК с ядром новой арх-ры

Предложения

Предложения

Предложения

Освоение фабрики Микрон – формирование отдельной программы

Не ослаблять требования в ПП719

Предложения

Освоение фабрики Микрон – формирование отдельной программы

Не ослаблять требования в ПП719

Отдельное понятие продукции вне Реестра («локализованная ВТ»).

Сформировать масштабную программу поддержки совместимости ПО с российскими процессорами. Стандарт кросс-платформенности.

Принять предложения по развитию оптимизированного, совместимого и безопасного ПО

Сформировать стандарты российских микросхем для расширения действия льгот на микросхемы зарубежного происхождения.

Экстренные меры по смягчению последствий санкций – авансированных и заблокированных поставок.

Основы алгоритмизации и программирования. Лекция 14

Основы алгоритмизации и программирования. Лекция 14 История Internet и Web, эволюция стандартов Web

История Internet и Web, эволюция стандартов Web Международная школа программирования для детей Unity 2D

Международная школа программирования для детей Unity 2D Электронное портфолио школьников

Электронное портфолио школьников Функциональное тестирование

Функциональное тестирование Прогулка по саду и огороду

Прогулка по саду и огороду  Autodesk 3ds Max

Autodesk 3ds Max Разработка инструментов оценки лояльности клиентов машиностроительного предприятия на основе интеллектуального анализа данных

Разработка инструментов оценки лояльности клиентов машиностроительного предприятия на основе интеллектуального анализа данных Корпоративные базы данных

Корпоративные базы данных Пять с создания компьютерной презентации. (Лекция 8)

Пять с создания компьютерной презентации. (Лекция 8) Создание мультимедийных презентаций

Создание мультимедийных презентаций Среда программирования Visual C++

Среда программирования Visual C++ Деловые коммуникации

Деловые коммуникации Логические основы компьютера

Логические основы компьютера Компьютерные модели различных процессов

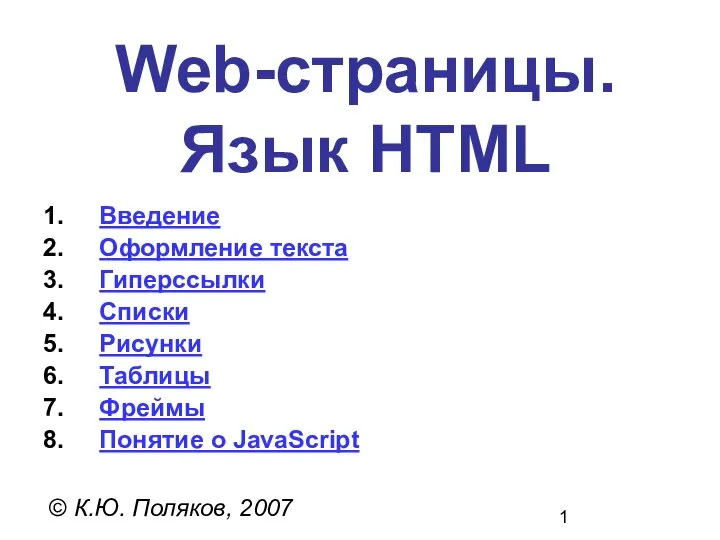

Компьютерные модели различных процессов Web-страницы. Язык HTML

Web-страницы. Язык HTML Учебный курс Введение в цифровую электронику Лекция 5 Обмен информацией в микропроцессорной системе кандидат технически

Учебный курс Введение в цифровую электронику Лекция 5 Обмен информацией в микропроцессорной системе кандидат технически Администрирование в информационных системах Безопасность информационных систем Шифрование

Администрирование в информационных системах Безопасность информационных систем Шифрование  ППС-2017, Лекция №2(3)

ППС-2017, Лекция №2(3) Государственная система защиты информации

Государственная система защиты информации Простейшие программы. Ввод-вывод. Операции в выражениях. Оператор присваивания

Простейшие программы. Ввод-вывод. Операции в выражениях. Оператор присваивания Driver assist. Additional fee for hand loading/unloading

Driver assist. Additional fee for hand loading/unloading Представление информации в компьютере

Представление информации в компьютере Информация в памяти компьютера. Системы счисления

Информация в памяти компьютера. Системы счисления Презентация Экономически активное рабочее население страны

Презентация Экономически активное рабочее население страны Типовые процедуры обработки списков в программах на языке Пролог

Типовые процедуры обработки списков в программах на языке Пролог Сложность программных систем

Сложность программных систем Краткий обзор программы АРМ Оценщика

Краткий обзор программы АРМ Оценщика