Содержание

- 2. Основные положения Программа должна быть размещена в памяти и оформлена в виде процесса для своего выполнения.

- 3. Связывание команд и данных с адресами памяти Может выполняться на разных этапах Во время компиляции: Если

- 4. Многоэтапная обработка пользовательской программы Исходный код программы (в форме текстового файла) на языке высокого уровня или

- 5. Логическое и физическое адресное пространство Концепция логического адресного пространства, которое связано с соответствующим физическим адресным пространством,

- 6. Устройство управления памятью (memory management unit – MMU) Аппаратура, преобразующая виртуальный адрес в физический. В схеме

- 7. Динамическое перемещение с использованием регистра перемещения

- 8. Динамическая загрузка Под динамической загрузкой понимается загрузка подпрограммы в память при первом обращении к ней из

- 9. Динамическая линковка Линковка откладывается до времени исполнения. Небольшой фрагмент кода – заглушка (stub) используется для размещения

- 10. Оверлейная структура (overlay) В ранних ОС, в особенности – для персональных компьютеров, для пользовательского процесса были

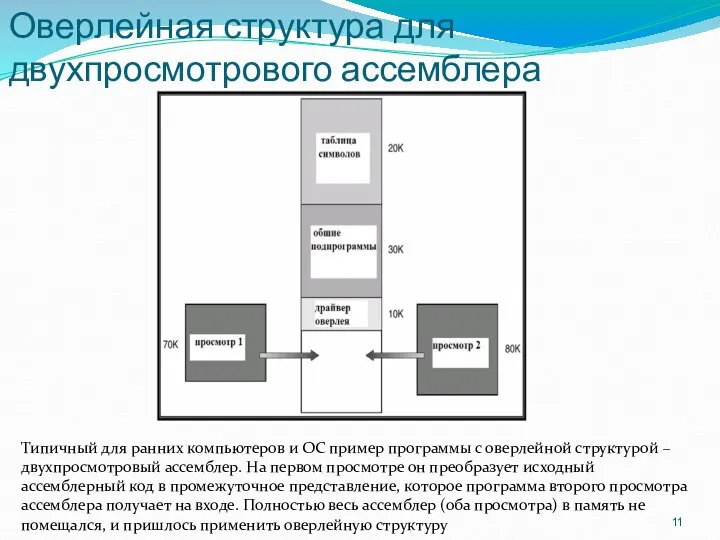

- 11. Оверлейная структура для двухпросмотрового ассемблера Типичный для ранних компьютеров и ОС пример программы с оверлейной структурой

- 12. Операционные системы Страничная организация памяти

- 13. Откачка и подкачка (swapping) Процесс может быть временно откачан в файл откачки (backing store) и затем

- 14. Схема откачки и подкачки

- 15. Смежное (contiguous) распределение памяти Обычно основная память разбивается на две непрерывных части (partitions): Резидентная ОС +

- 16. Аппаратная поддержка регистров перемещения и границы

- 17. Смежное распределение (продолжение) Распределение в нескольких смежных областях Свободная область (hole) – блок доступной памяти; свободные

- 18. Стратегии динамического распределения памяти Как удовлетворить запрос на участок памяти длиной n, используя список свободных областей?

- 19. Фрагментация Внешняя фрагментация – имеется достаточно большая область свободной памяти, но она не является непрерывной .

- 20. Страничная организация (paging) Логическое адресное пространство процесса может и не быть непрерывным; процессу выделяется физическая память

- 21. Схема трансляции адресов Адрес, генерируемый процессором, подразделяется на: Номер страницы (p) – используется как индекс в

- 22. Архитектура трансляции адресов

- 23. Пример страничной организации

- 24. Пример страничной организации

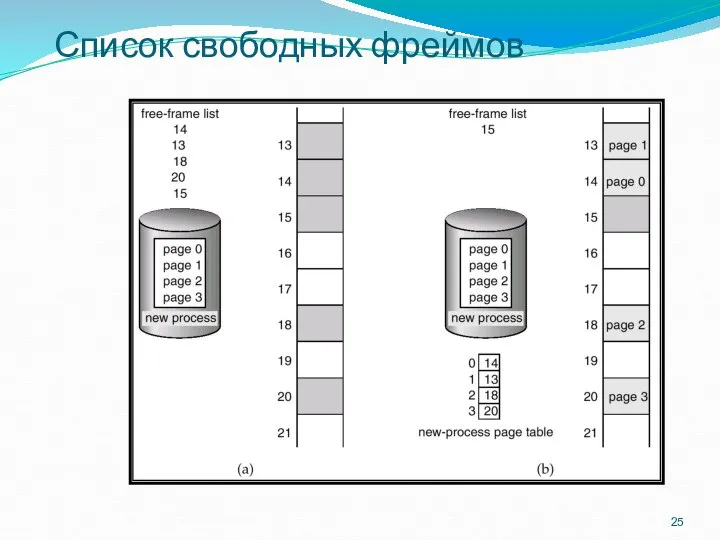

- 25. Список свободных фреймов

- 26. Реализация таблицы страниц Таблица страниц хранится в основной памяти. Базовый регистр таблицы страниц(PTBR) указывает на таблицу

- 27. Ассоциативная память Ассоциативная память: параллельный поиск Таблица пар: (номер страницы, номер фрейма) Трансляция адресов (A´, A´´)

- 28. Аппаратная поддержка страничной организации: TLB

- 29. Эффективное время поиска (effective access time – EAT) Ассоциативный поиск = ε единиц времени Предположим, что

- 30. Защита памяти Защита памяти может быть реализована описанием каждого фрейма специальным битом (valid/invalid). Данный бит хранится

- 31. Бит valid/invalid в таблице страниц

- 32. Структура таблицы страниц Иерархические таблицы страниц Хешированные таблицы страниц Инвертированные таблицы страниц

- 33. Иерархические таблицы страниц Логическое адресное пространство разбивается на несколько таблиц страниц. Простой метод: двухуровневая таблица страниц.

- 34. Пример двухуровневой таблицы страниц Логический адрес (на 32-битной машине с размером страницы 4 K) подразделяется на:

- 35. Схема двухуровневых таблиц страниц

- 36. Схема адресной трансляции

- 37. Хешированные таблицы страниц Общеупотребительны, если адресное пространство > 32 битов. Виртуальный номер страницы в результате вычисления

- 38. Хешированная таблица страниц

- 39. Инвертированная таблица страниц Один элемент для каждой реальной страницы в памяти. Элемент состоит из виртуального адреса

- 40. Архитектура инвертированной таблицы страниц

- 41. Разделяемые страницы Разделяемый код Единственная копия неизменяемого (реентерабельного - reentrant) кода, совместно используемого несколькими процессами, -

- 42. Пример: разделяемые страницы

- 43. Операционные системы Сегментная организация памяти

- 44. Сегментная организация памяти (segmentation) Схема распределения памяти, соответствующая пользовательской трактовке распределения памяти. Программа – набор сегментов.

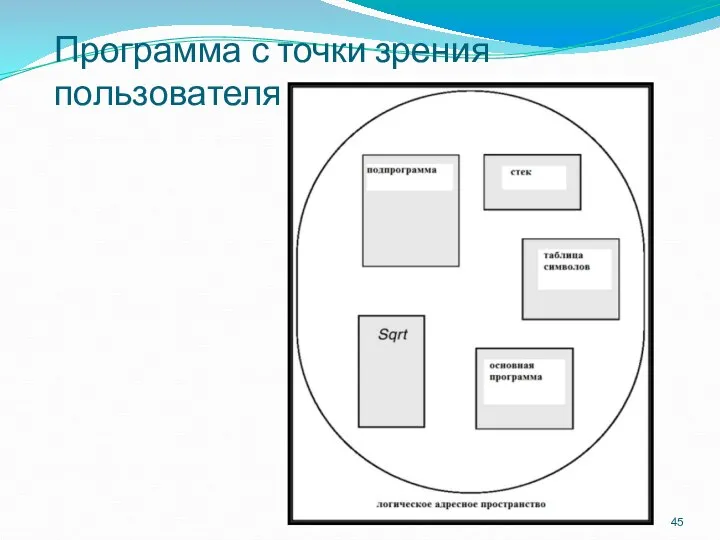

- 45. Программа с точки зрения пользователя

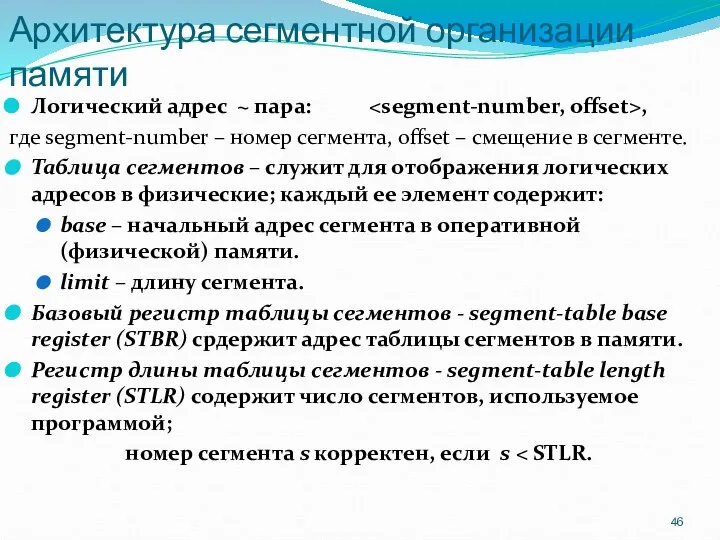

- 46. Архитектура сегментной организации памяти Логический адрес ~ пара: , где segment-number – номер сегмента, offset –

- 47. Архитектура сегментной организации (продолжение) Перемещение (Relocation). динамическое с помощью таблицы сегментов. Общий доступ (Sharing). Разделяемые сегменты

- 48. Защита. С каждым элементом таблицы сегментов связываются: validation bit = 0 ⇒ неверный сегмент read/write/execute -

- 49. Аппаратная поддержка сегментного распределения памяти

- 50. Пример сегментной организации памяти

- 52. Скачать презентацию

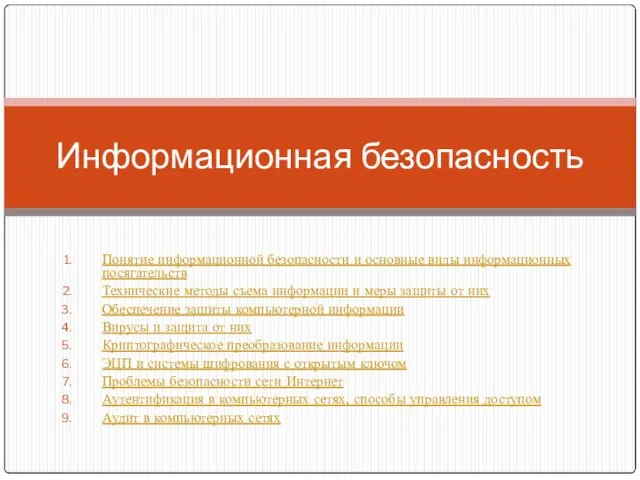

Информационная безопасность

Информационная безопасность Заместитель. Проблема&Решение

Заместитель. Проблема&Решение Создание запросов на выборку в базе данных

Создание запросов на выборку в базе данных Использование функций в С++ для АСУб и ЭВМб. Тема 3-2

Использование функций в С++ для АСУб и ЭВМб. Тема 3-2 Основы защиты информации. Лекция №10

Основы защиты информации. Лекция №10 Microcontrollers misis 2017

Microcontrollers misis 2017 Текст и текстовый редактор

Текст и текстовый редактор Редактор кода Visual Studio Code

Редактор кода Visual Studio Code Кодирование звуковой информации

Кодирование звуковой информации Алгоритм работы при подключении услуги GAZ Connect

Алгоритм работы при подключении услуги GAZ Connect Нейросети в задаче трекинга

Нейросети в задаче трекинга Представление чисел в памяти компьютера. 10 класс

Представление чисел в памяти компьютера. 10 класс Мониторинг трендов в социальных сетях в режиме реального времени (на примере Twitter)

Мониторинг трендов в социальных сетях в режиме реального времени (на примере Twitter) Введение в программирование Презентацию подготовила учитель математики и информатики МОУ Купанской СОШ Переславского МР Ми

Введение в программирование Презентацию подготовила учитель математики и информатики МОУ Купанской СОШ Переславского МР Ми Разработка опытного образца экзоскелета

Разработка опытного образца экзоскелета Естественные и искусственные источники информации. 3 класс

Естественные и искусственные источники информации. 3 класс Глобальная компьютерная сеть интернет

Глобальная компьютерная сеть интернет Базы данных

Базы данных Линейная регрессия. Корреляционный и регрессионный анализ

Линейная регрессия. Корреляционный и регрессионный анализ Информатика. Задачи информатики. Понятие об информации

Информатика. Задачи информатики. Понятие об информации Оценка количественных параметров текстовых документов

Оценка количественных параметров текстовых документов Электронные таблицы

Электронные таблицы Методический материал Техэксперт: Помощник проектировщика

Методический материал Техэксперт: Помощник проектировщика Android basic training networking

Android basic training networking Время #кодить

Время #кодить Машинное обучение

Машинное обучение Презентация "Умозаключение как форма мышления" - скачать презентации по Информатике

Презентация "Умозаключение как форма мышления" - скачать презентации по Информатике Операторы определения данных

Операторы определения данных