Содержание

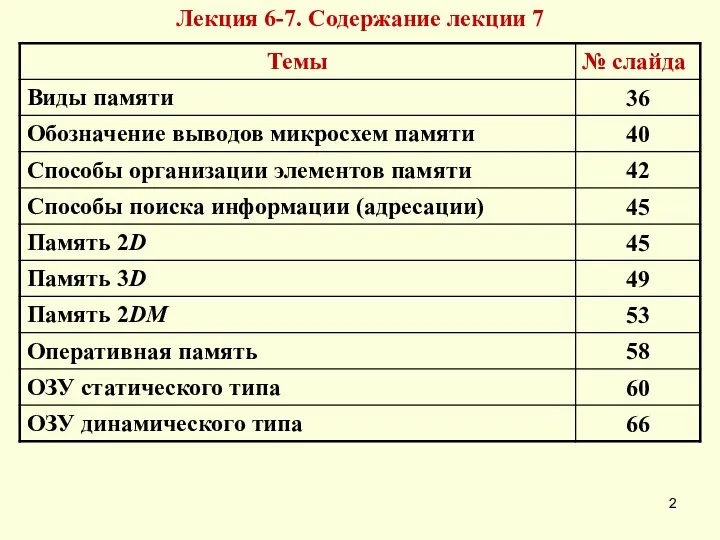

- 2. Лекция 6-7. Содержание лекции 7

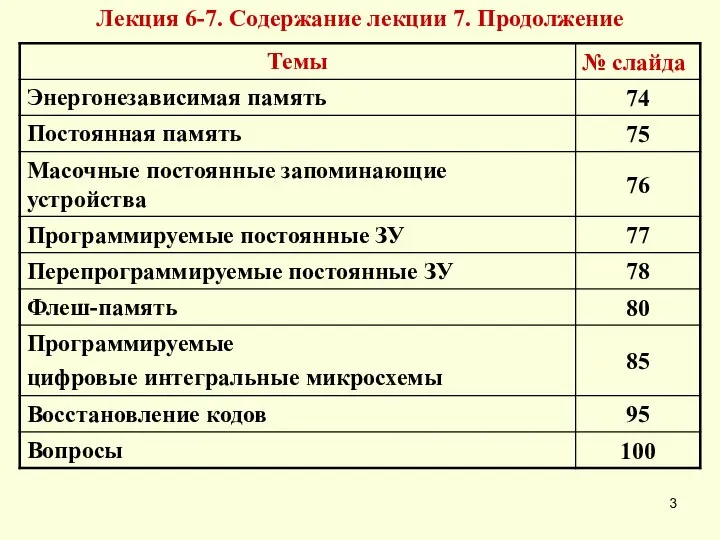

- 3. Лекция 6-7. Содержание лекции 7. Продолжение

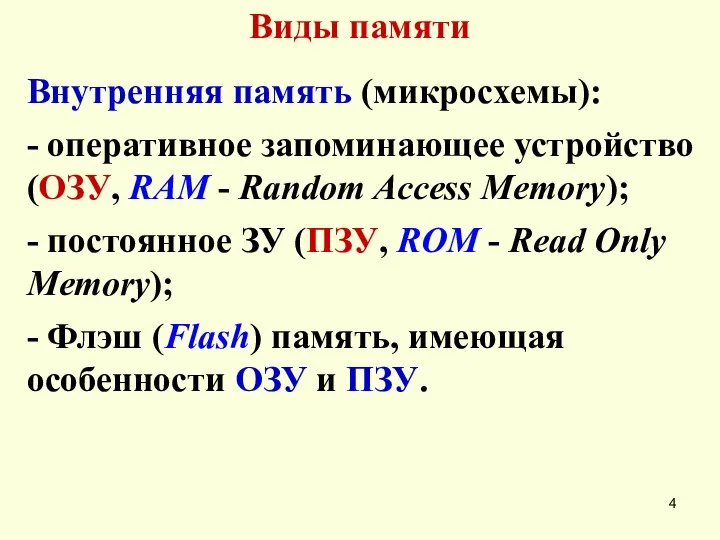

- 4. Виды памяти Внутренняя память (микросхемы): - оперативное запоминающее устройство (ОЗУ, RAM - Random Access Memory); -

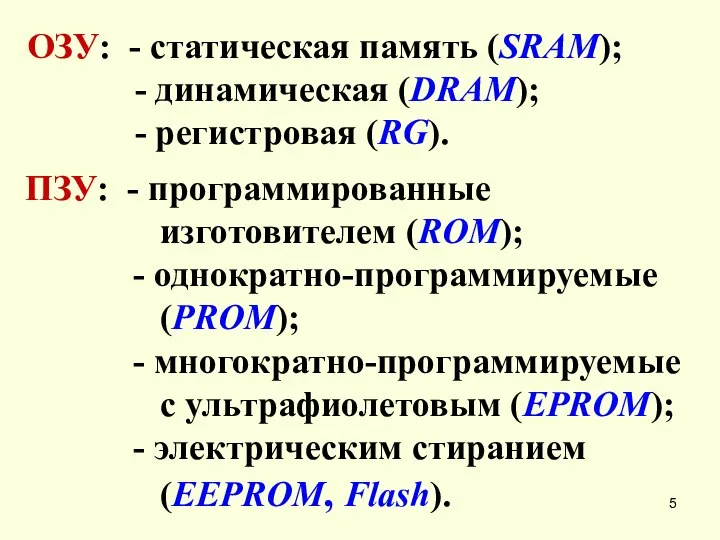

- 5. ОЗУ: - статическая память (SRAM); - динамическая (DRAM); - регистровая (RG). ПЗУ: - программированные изготовителем (ROM);

- 6. Элемент памяти (ЭП): триггер, миниатюрный конденсатор, транзистор , плавкая перемычка (или ее отсутствие). Упорядоченный набор ЭП

- 7. Емкость ЗУ - в единицах кратных числу 210 = 1024 = 1K. Для длины слова равной

- 8. Обозначение выводов микросхем памяти: A – шина адреса; D0 – шина выходных данных; W/R – операция

- 9. В правом верхнем углу указывается состояние выходных шин, например: - выход имеет три состояния: 0, 1,

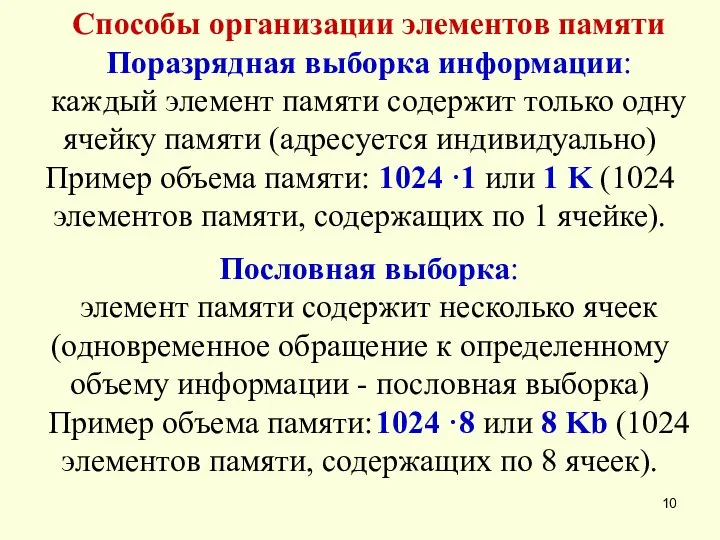

- 10. Способы организации элементов памяти Поразрядная выборка информации: каждый элемент памяти содержит только одну ячейку памяти (адресуется

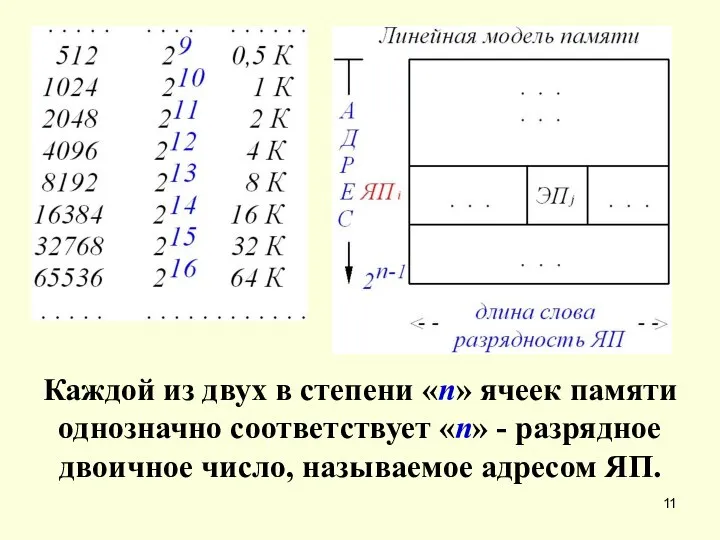

- 11. Каждой из двух в степени «n» ячеек памяти однозначно соответствует «n» - разрядное двоичное число, называемое

- 12. Например, адресом 511-ой ячейки будет число 1 1111 1111 (BIN) = 511(DEC) = 1FF(HEX). Емкость ЗУ

- 13. Способы поиска информации (адресация) Память 2D включает в себя: - матрица элементов памяти, ряд строк со

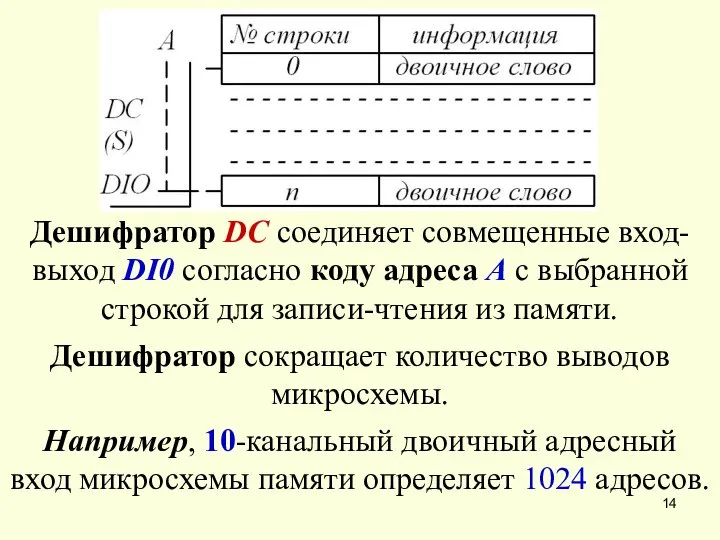

- 14. Дешифратор сокращает количество выводов микросхемы. Дешифратор DC соединяет совмещенные вход-выход DI0 согласно коду адреса A с

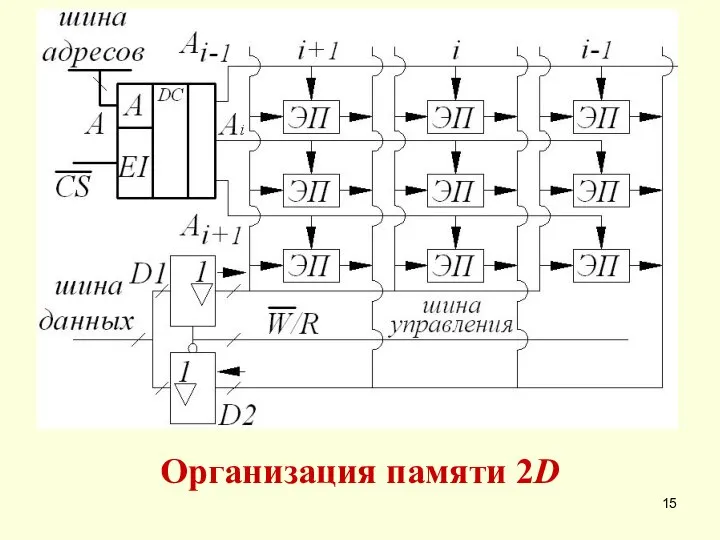

- 15. Организация памяти 2D

- 16. При записи, информация с шины данных параллельным кодом передается через буферы D1 в элементы памяти. Буферы

- 17. Память 3D включает в себя: - матрица элементов памяти из n квадратных подматриц (для записи-чтения одного

- 18. Функциональная схема подматрицы памяти 3D

- 19. При записи или считывании информации выбираются n элементов памяти, по одному из каждой подматрицы. Они находятся

- 20. При записи информационный сигнал с шины данных записывается через буферы D1 в элементы памяти. Буферы D2

- 21. Память 2DM включает в себя: - матрица элементов памяти (ряд строк с адресами (первая часть адресного

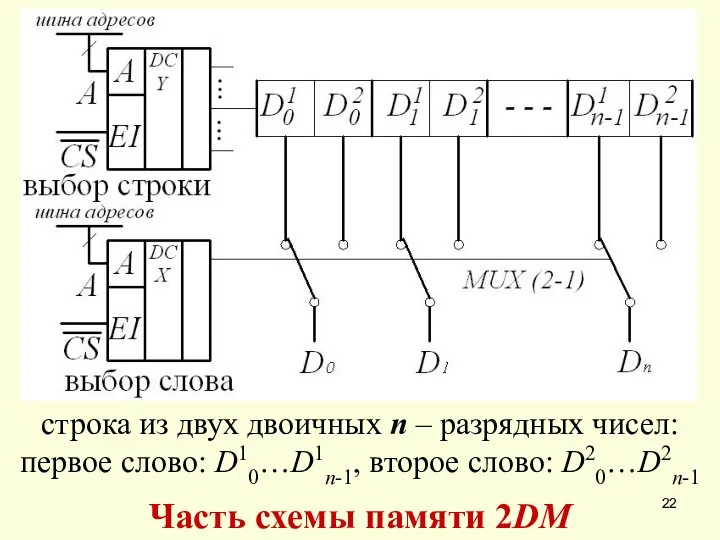

- 22. Часть схемы памяти 2DM строка из двух двоичных n – разрядных чисел: первое слово: D10…D1n-1, второе

- 23. Дешифратор X выбирает строки, каждая содержит группы элементов памяти, равные по емкости. Первая группа - для

- 24. Например, дешифратор X, в соответствии с адресом, выбирает седьмую строку. Согласно сигналу управления дешифратора Y, мультиплексоры

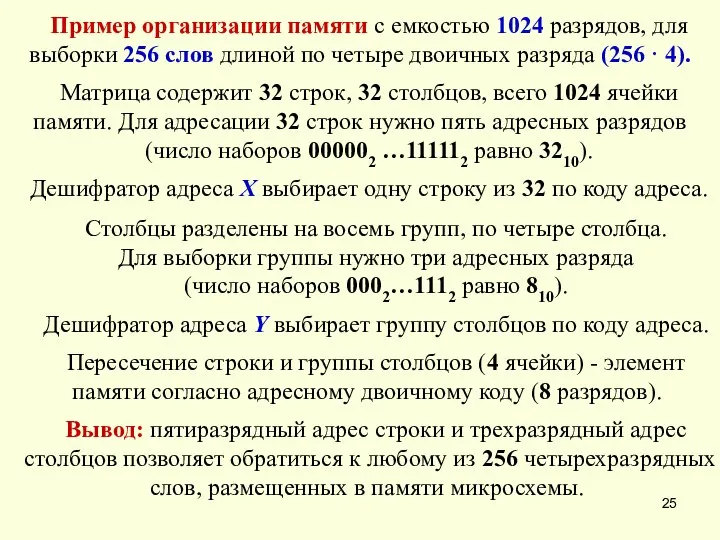

- 25. Пример организации памяти с емкостью 1024 разрядов, для выборки 256 слов длиной по четыре двоичных разряда

- 26. Оперативная память (Random Access Memory, с произвольной выборкой) статическая (SRAM) Применяется для хранения, приема и выдачи

- 27. Данная память имеет высокое быстродействие (цикл обращения 8-20 нс), относительно небольшую информационную емкость, энергетическую зависимость (при

- 28. ОЗУ статического типа

- 29. В качестве элемента памяти используется D-триггер. В микросхеме 537РУ10, например, каждая ЯП состоит из восьми триггеров

- 30. Доступ к ЯПj: Дешифратор столбцов (DCc - заводится k адресных линий); Дешифратор строк (DCr - n-k

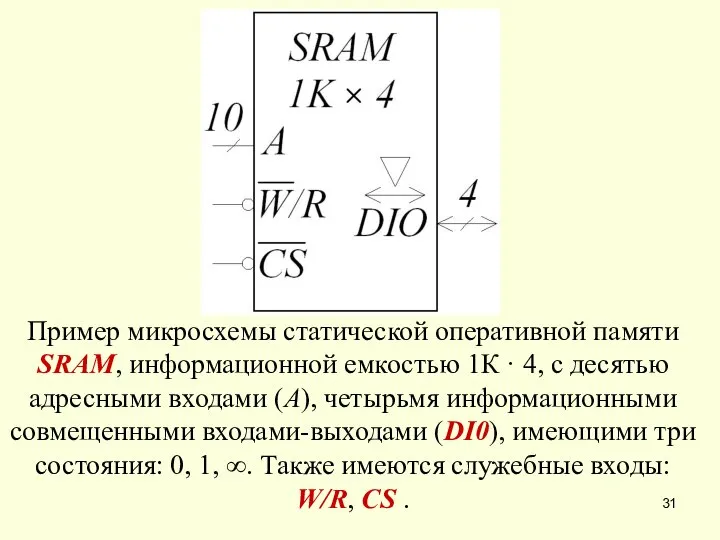

- 31. Пример микросхемы статической оперативной памяти SRAM, информационной емкостью 1К · 4, с десятью адресными входами (A),

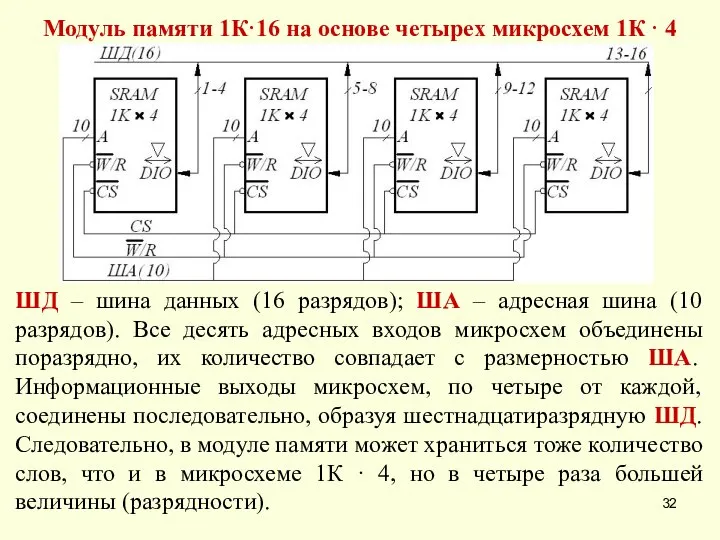

- 32. Модуль памяти 1К·16 на основе четырех микросхем 1К · 4 ШД – шина данных (16 разрядов);

- 33. Увеличение объема памяти

- 34. ОЗУ динамического типа Элемент памяти - микроконденсатор в интегральном исполнении. Две одноименные k-линии каждой группы подключаются

- 35. Динамическая память Информация хранится в виде зарядов на конденсаторах малой емкости (~0,05 пФ). Если конденсатор заряжен,

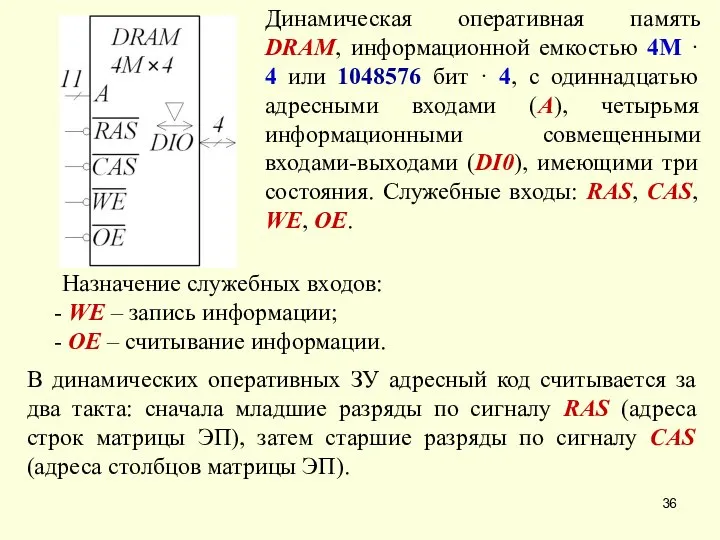

- 36. Динамическая оперативная память DRAM, информационной емкостью 4М · 4 или 1048576 бит · 4, с одиннадцатью

- 37. Для уменьшения числа выводов микросхем памяти используется адресное мультиплицирование. В динамических ЗУ адресный код считывается за

- 38. Пример подключения линий адреса входам через MUX(2-1) и DMX(1-2)

- 39. Примечание подключение 18-и линий адреса к 9-и адресным входам через 9-ть MUX(2-1)

- 40. Пример. Микросхемы динамической оперативной памяти серии К565РУ емкостью от 16 К до 1024 К. Структура элементов

- 41. Динамическая оперативная память в компьютерах (SIMM, EDO, SDRAM) имеет цикл обращения около10 нс, информационная емкость микросхемы

- 42. Энергонезависимая память (NVSRAM) Пример: Статическая оперативная память: Заряды поддерживаются встроенной в микросхему литиевой батарейкой большой емкости.

- 43. Постоянная память Постоянная память содержит неизменную информацию, которую можно только считывать, длительно хранить и многократно использовать

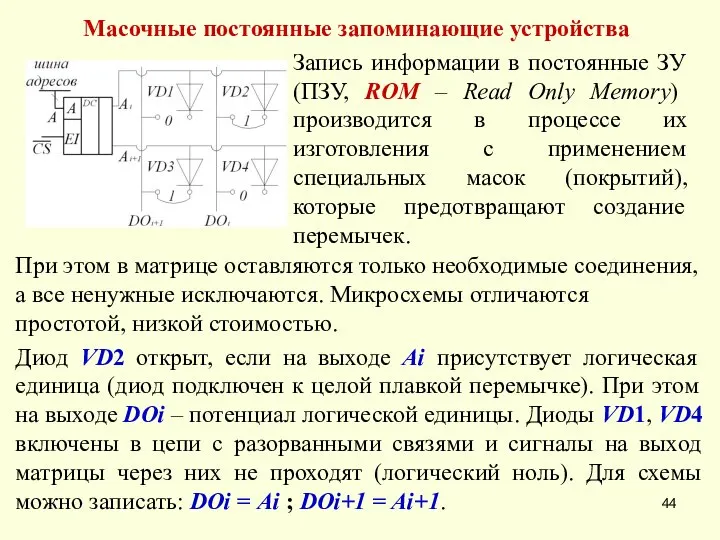

- 44. Масочные постоянные запоминающие устройства Запись информации в постоянные ЗУ (ПЗУ, ROM – Read Only Memory) производится

- 45. Программируемые постоянные ЗУ Микросхемы ППЗУ (PROM – Programmable Read Only Memory) конструктивно аналогичны масочным постоянным ЗУ

- 46. Перепрограммируемые постоянные ЗУ Для этой памяти допустимо многократное стирание и запись информации. Перепрограммируемые постоянные ЗУ (REPROM

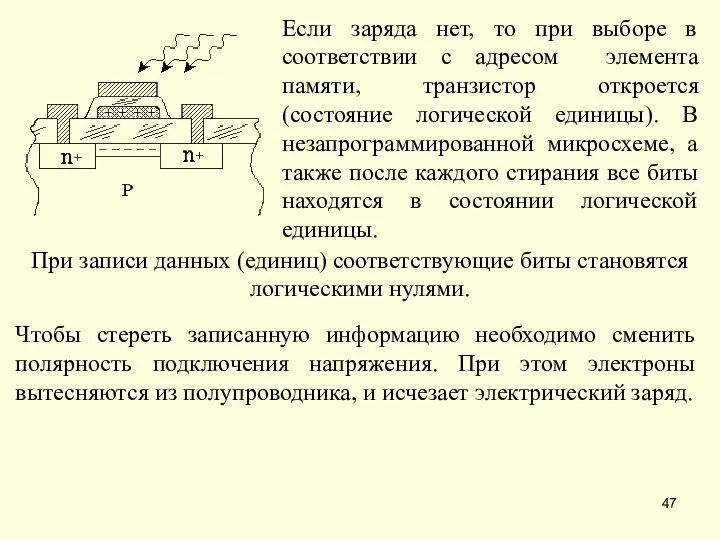

- 47. Если заряда нет, то при выборе в соответствии с адресом элемента памяти, транзистор откроется (состояние логической

- 48. Флэш-память отличается способом получения и сохранения заряда, управляющего работой транзистора. Управляющий вход полевого транзистора размещен внутри

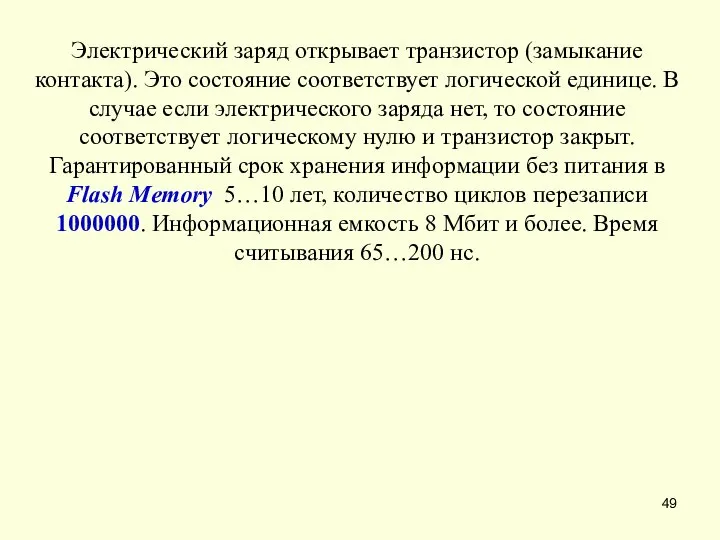

- 49. Электрический заряд открывает транзистор (замыкание контакта). Это состояние соответствует логической единице. В случае если электрического заряда

- 50. Отличие динамического ОЗУ от статического: - мультиплексирование адресных входов; - регенерация хранимой информации; - повышенная емкость

- 51. Программируемые цифровые интегральные микросхемы Основаны на реализации дизъюнктивной нормальной формы (ДНФ) с помощью элементов И, ИЛИ,

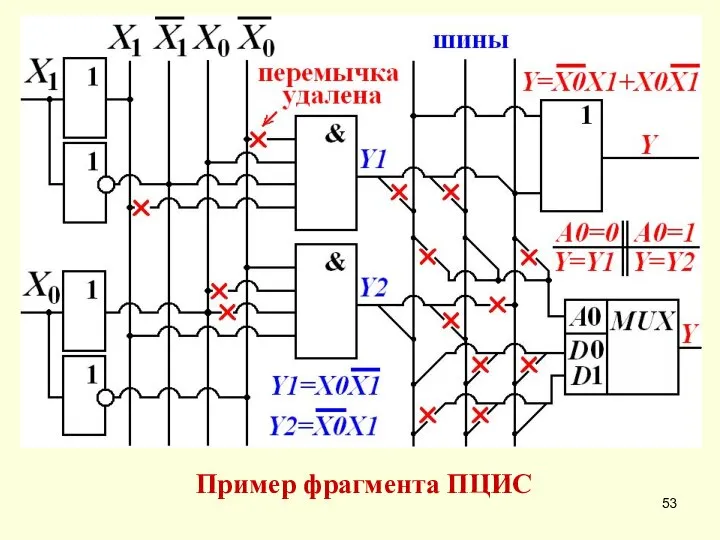

- 52. Структурная схема ПЦИС Пример фрагмента логической матрицы Логические элементы: мультиплексоры, демультиплексоры, триггеры.

- 53. Пример фрагмента ПЦИС

- 54. Преимущества перед дискретными элементами: - Уменьшение габаритов; - Увеличение быстродействия; - Повышение надежности; - Защита от

- 55. ВОПРОСЫ

- 57. Скачать презентацию

Религия. Формы и виды религии. Функции религии в обществе

Религия. Формы и виды религии. Функции религии в обществе История школы нашей - часть истории всей страны

История школы нашей - часть истории всей страны Работа по реинжинирингу на примере компании ООО Костромской завод котельного оборудования

Работа по реинжинирингу на примере компании ООО Костромской завод котельного оборудования Технология изготовления валов

Технология изготовления валов Изготовление выкройки швейного изделия, на примере прямой юбки

Изготовление выкройки швейного изделия, на примере прямой юбки Презентация к 41 параграфу

Презентация к 41 параграфу Налоги

Налоги Православие в моей семье. Фотоальбом

Православие в моей семье. Фотоальбом Продукция предприятий лесной отрасли на территории Чусовского района в период с 1941 по 1945 г.г

Продукция предприятий лесной отрасли на территории Чусовского района в период с 1941 по 1945 г.г Последний звонок

Последний звонок музыка

музыка Времена года

Времена года Презентация Деннерле

Презентация Деннерле Электронные средства досмотра

Электронные средства досмотра класс №1

класс №1 Жить – добро творить

Жить – добро творить ВТ Сервис, отчет по практике

ВТ Сервис, отчет по практике

Модели и методы исследования информационных процессов и систем

Модели и методы исследования информационных процессов и систем Комплектующие компьютера

Комплектующие компьютера История металлургии

История металлургии Презентация Кудряшовой

Презентация Кудряшовой 20160108_zhivichkova_e._i._schastlivyy_skazochnyy_sluchay

20160108_zhivichkova_e._i._schastlivyy_skazochnyy_sluchay Притирка. Качество и продуктивность притирки

Притирка. Качество и продуктивность притирки Всемирный день здоровья

Всемирный день здоровья Задание графа

Задание графа №1-4ч.Мамин праздник

№1-4ч.Мамин праздник Stainless Steel. Wire Mesh

Stainless Steel. Wire Mesh