Содержание

- 2. Информация, циркулирующая в вычислительной системе в виде двоичных слов, хранится в памяти. В зависимости от места

- 3. Микросхемы памяти (или просто память, или запоминающие устройства — ЗУ, английское "Memory") представляют собой следующий шаг

- 4. Внутренняя память Представляет собой полупроводниковые запоминающие устройства (ЗУ). Полупроводниковые ЗУ выполняются на больших интегральных схемах (БИС).

- 5. ЗУ имеет регулярную структуру, т.е. состоит из однотипных ячеек памяти (ЯП). ЯП предназначена для хранения одного

- 6. Организация памяти В памяти может храниться N n-разрядных слов.

- 7. Режимы работы памяти: Занесение информации в память – запись; Выборка информации из памяти –считывание; Хранение информации

- 8. В режиме записи необходимо: Организовать обращение по адресу ячейки, где будет размещена информация; Подать записываемую информацию;

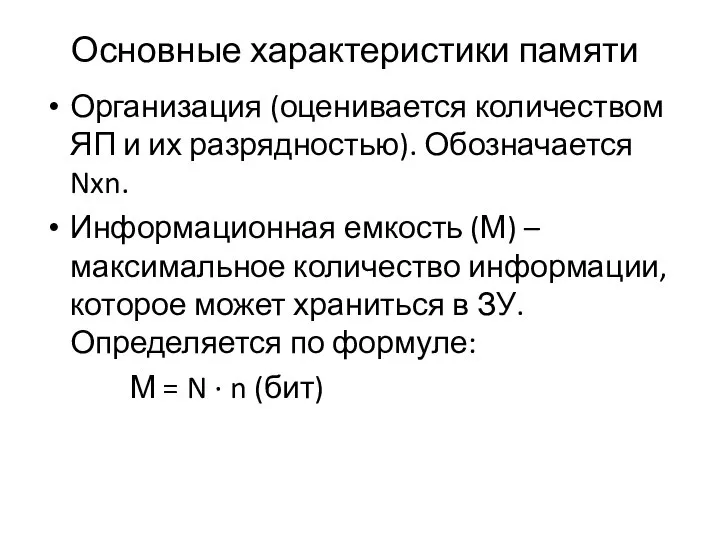

- 9. Основные характеристики памяти Организация (оценивается количеством ЯП и их разрядностью). Обозначается Nxn. Информационная емкость (М) –

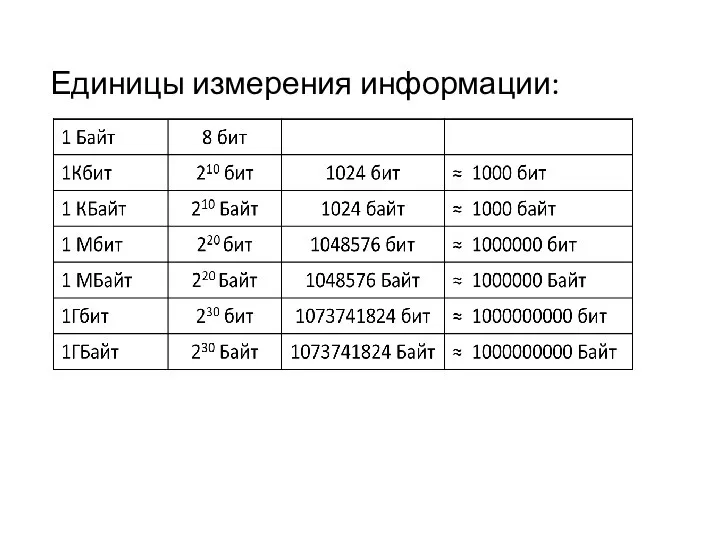

- 10. Единицы измерения информации:

- 11. Быстродействие (определяется временем обращения к ЗУ) При записи время обращения tобр. складывается из времени поиска ячейки

- 12. Классификация внутренней памяти по функциональному назначению

- 13. Классификация внутренней памяти по способу обращения

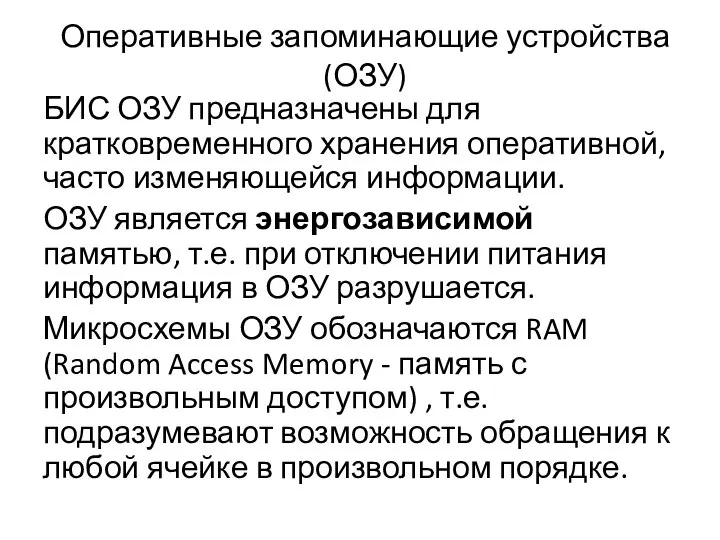

- 14. Оперативные запоминающие устройства (ОЗУ) БИС ОЗУ предназначены для кратковременного хранения оперативной, часто изменяющейся информации. ОЗУ является

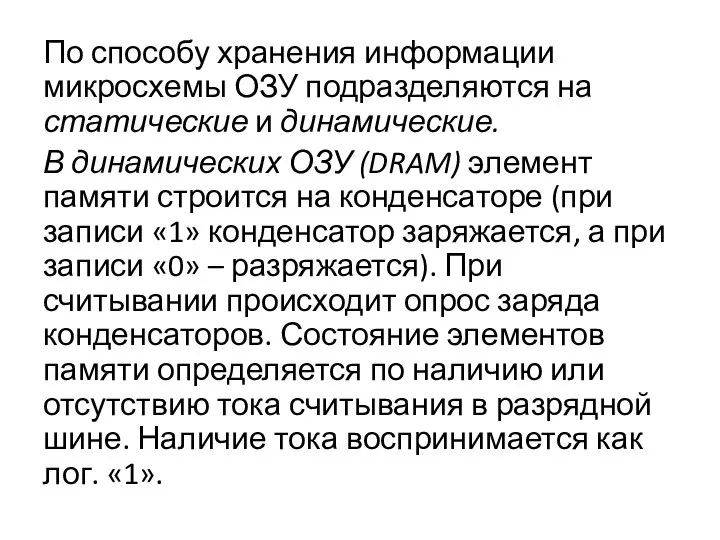

- 15. По способу хранения информации микросхемы ОЗУ подразделяются на статические и динамические. В динамических ОЗУ (DRAM) элемент

- 16. При считывании происходит разряд конденсатора (разрушающее считывание), поэтому специальные схемы снова подзаряжают конденсаторы (регенерация). Также к

- 17. В статических ОЗУ (SRAM, RAM) элемент памяти представляет собой триггер, в который может быть записана информация

- 18. Структурная схема статического ОЗУ Микросхемы ОЗУ состоят из накопителя и схем управления. Накопитель предназначен для хранения

- 19. Накопитель состоит из элементов матрицы nxN, где n – номера столбцов или разрядов хранимого слова, N

- 20. Дешифратор адресного кода Аm-1…А1А0 (mx2m) предназначен для активации одной из адресных шин при поступлении сигнала выбора

- 21. Усилители считывания реализуют режим чтения содержимого ячейки ОЗУ при подаче активного сигнала для считывания на W/R

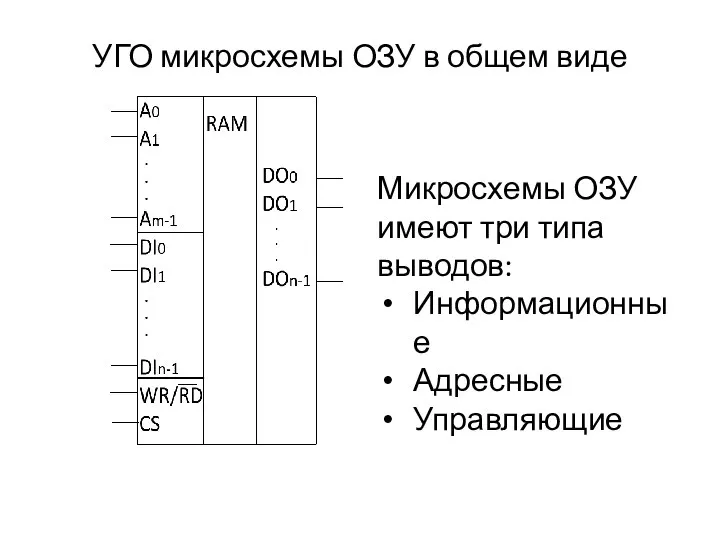

- 22. УГО микросхемы ОЗУ в общем виде Микросхемы ОЗУ имеют три типа выводов: Информационные Адресные Управляющие

- 23. На информационные входы DIn-1…DI1DI0 поступают n-разрядные входные данные, которые необходимо записать в ячейку. С информационных выходов

- 24. Микросхема ОЗУ может работать в трех режимах: хранения и режимы обращения (записи и считывания). Вход CS

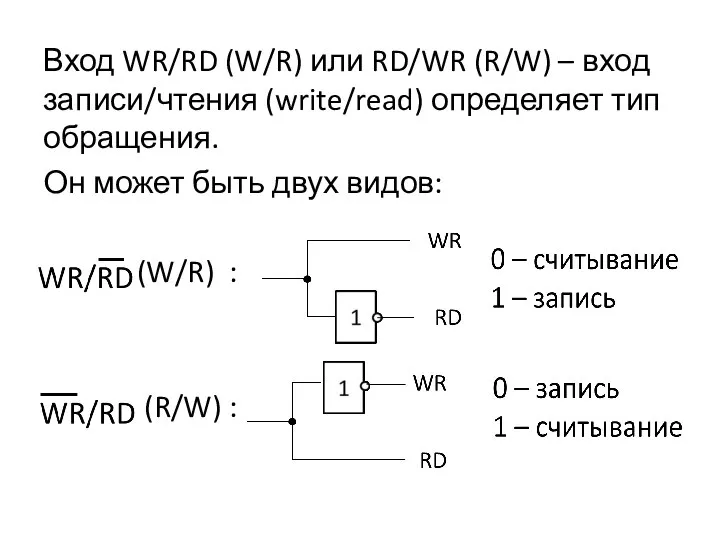

- 25. Вход WR/RD (W/R) или RD/WR (R/W) – вход записи/чтения (write/read) определяет тип обращения. Он может быть

- 26. В отечественных сериях микросхемы ОЗУ имеют буквенный код РУ. Например,

- 27. Одноразрядная оперативная память в основном бывает с раздельными шинами входных и выходных данных. Многоразрядная оперативная память

- 28. Например, Микросхемы имеют выходы 3С, что позволяет отключать их от шины, переводя в состояние Z.

- 29. Исходя из разрядности адресной шины микросхемы, можно рассчитать количество различных адресов , а следовательно можно определить

- 30. Например, определить организацию и информационную емкость микросхемы ОЗУ К565РУ2, организовать запись «1» в 109 ячейку памяти.

- 31. Организация режима записи заданного слова в указанную по номеру ячейку: 1)необходимо определить адрес ячейки и подать

- 32. Задания для самостоятельной работы: Определить организацию микросхем ОЗУ К541РУ1, К541РУ2 и рассчитать их информационную емкость. Обеспечить

- 33. Построение модуля ОЗУ заданного объема Микросхемы оперативной памяти довольно часто объединяются для увеличения разрядности данных (длины

- 34. Наращивание разрядности обрабатываемого слова Для этого микросхемы ОЗУ соединяются параллельно. Входы CS всех микросхем объединяются, также

- 35. Например, увеличение разрядности данных в два раза:

- 36. Наращивание количества ячеек памяти Для этого микросхемы соединяются последовательно. Для увеличения количества ячеек вдвое достаточно 2-х

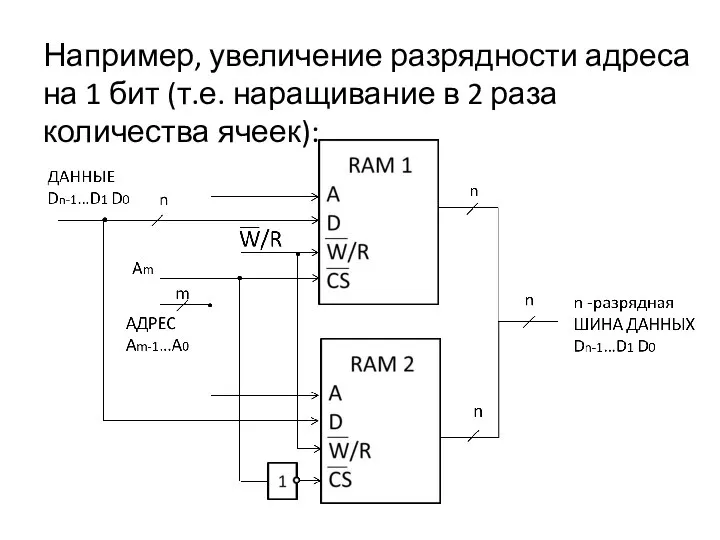

- 37. Например, увеличение разрядности адреса на 1 бит (т.е. наращивание в 2 раза количества ячеек):

- 38. Если необходимо увеличить количество ячеек более чем в 2 раза, то применяют дешифратор. Младшие разряды адреса

- 39. Например, увеличение количества ячеек в 4 раза (увеличение разрядности адреса на 2 бита):

- 40. Постоянные запоминающие устройства (ПЗУ) ПЗУ служат для длительного хранения постоянной информации, не изменяющейся в процессе работы

- 41. Основным элементом, используемым для обеспечения хранения информации, является перемычка на определенном участке электрической цепи. При наличии

- 42. В ПЗУ запись информации (программирование) производится заранее вне вычислительного устройства с применением дополнительных технологических операций, таких

- 43. Масочные ПЗУ Этому типу памяти соответствует обозначение ROM (Read Only Memory — память только для считывания).

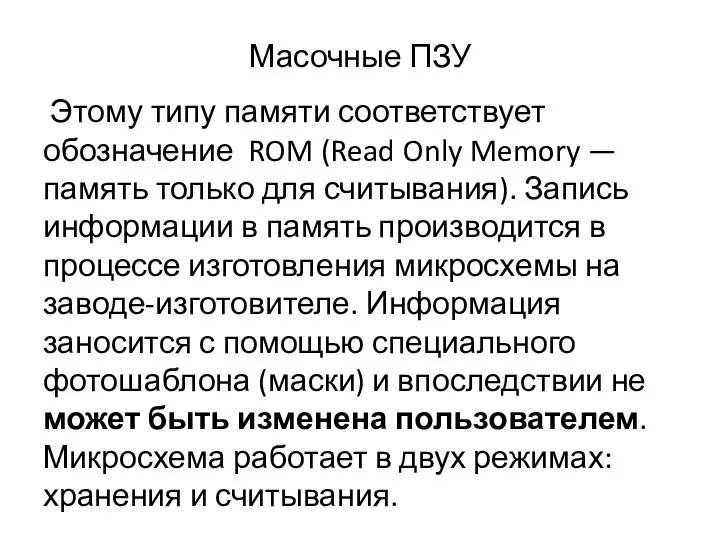

- 44. Масочные ПЗУ используются лишь при выпуске больших партий устройств с одной и той же прошивкой. Эти

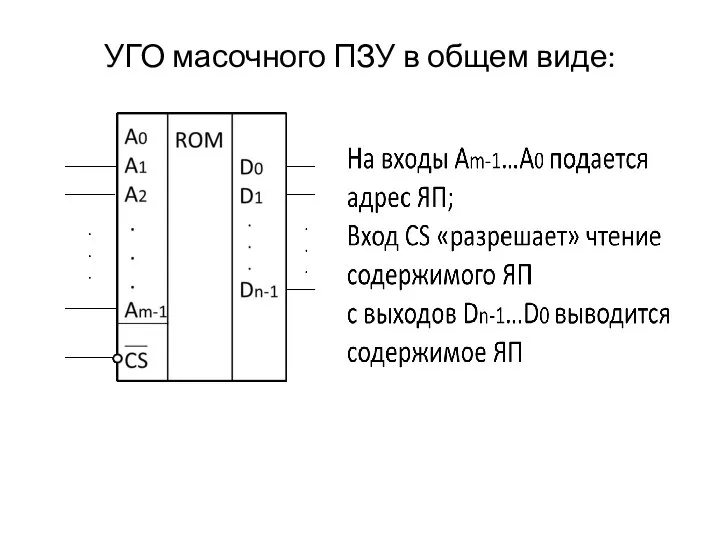

- 45. УГО масочного ПЗУ в общем виде:

- 46. Программируемые ПЗУ (ППЗУ) Этому типу ПЗУ соответствует обозначение PROM (Programmable Read Only Memory). Микросхема поступает к

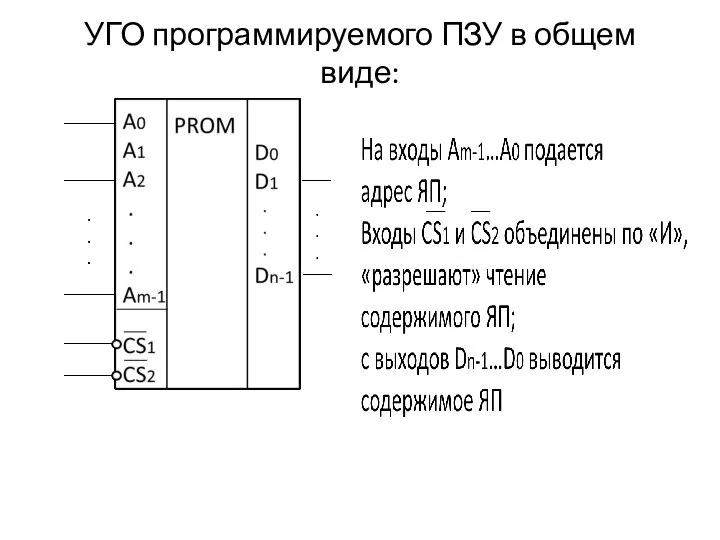

- 47. УГО программируемого ПЗУ в общем виде:

- 48. ППЗУ также имеют высокую надежность готовой микросхемы и устойчивы к электромагнитным полям и радиации. Возможность программировать

- 49. Репрограммируемые ПЗУ (РПЗУ) Этому типу ПЗУ соответствует обозначение RPROM (EPROM) или EЕPROM. Микросхема допускает многократное программирование

- 50. RPROM (EPROM) – Erasable Programmable ROM – микросхемы, информация в которых стирается ультрафиолетовым излучением через специальное

- 51. Для прошивки РПЗУ используется программатор. Некоторые РПЗУ можно программировать прямо в целевом устройстве, подключая внешний программатор.

- 52. Элементарная ячейка хранения данных flash-памяти представляет из себя транзистор с плавающим затвором. Особенность такого транзистора в

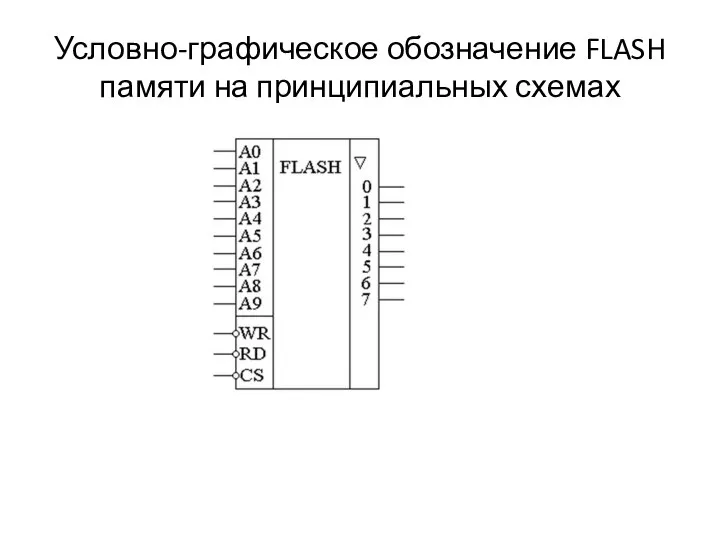

- 53. Условно-графическое обозначение FLASH памяти на принципиальных схемах

- 55. Скачать презентацию

Религия. Формы и виды религии. Функции религии в обществе

Религия. Формы и виды религии. Функции религии в обществе История школы нашей - часть истории всей страны

История школы нашей - часть истории всей страны Работа по реинжинирингу на примере компании ООО Костромской завод котельного оборудования

Работа по реинжинирингу на примере компании ООО Костромской завод котельного оборудования Технология изготовления валов

Технология изготовления валов Изготовление выкройки швейного изделия, на примере прямой юбки

Изготовление выкройки швейного изделия, на примере прямой юбки Презентация к 41 параграфу

Презентация к 41 параграфу Налоги

Налоги Православие в моей семье. Фотоальбом

Православие в моей семье. Фотоальбом Продукция предприятий лесной отрасли на территории Чусовского района в период с 1941 по 1945 г.г

Продукция предприятий лесной отрасли на территории Чусовского района в период с 1941 по 1945 г.г Последний звонок

Последний звонок музыка

музыка Времена года

Времена года Презентация Деннерле

Презентация Деннерле Электронные средства досмотра

Электронные средства досмотра класс №1

класс №1 Жить – добро творить

Жить – добро творить ВТ Сервис, отчет по практике

ВТ Сервис, отчет по практике

Модели и методы исследования информационных процессов и систем

Модели и методы исследования информационных процессов и систем Комплектующие компьютера

Комплектующие компьютера История металлургии

История металлургии Презентация Кудряшовой

Презентация Кудряшовой 20160108_zhivichkova_e._i._schastlivyy_skazochnyy_sluchay

20160108_zhivichkova_e._i._schastlivyy_skazochnyy_sluchay Притирка. Качество и продуктивность притирки

Притирка. Качество и продуктивность притирки Всемирный день здоровья

Всемирный день здоровья Задание графа

Задание графа №1-4ч.Мамин праздник

№1-4ч.Мамин праздник Stainless Steel. Wire Mesh

Stainless Steel. Wire Mesh