Содержание

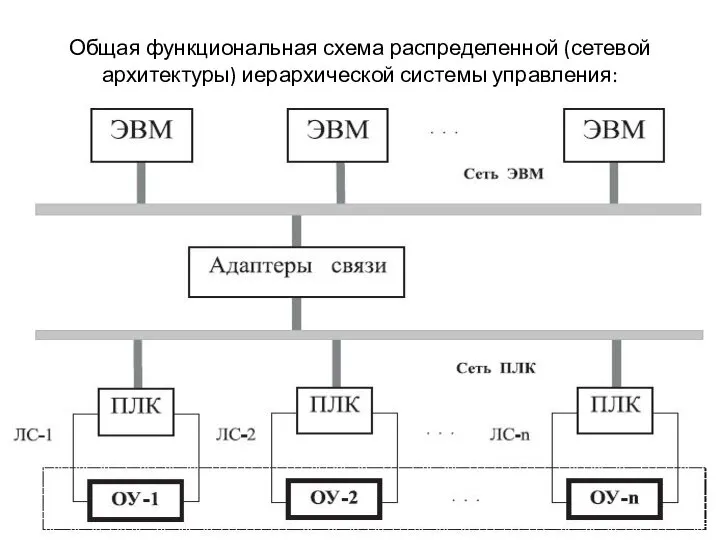

- 2. Общая функциональная схема распределенной (сетевой архитектуры) иерархической системы управления:

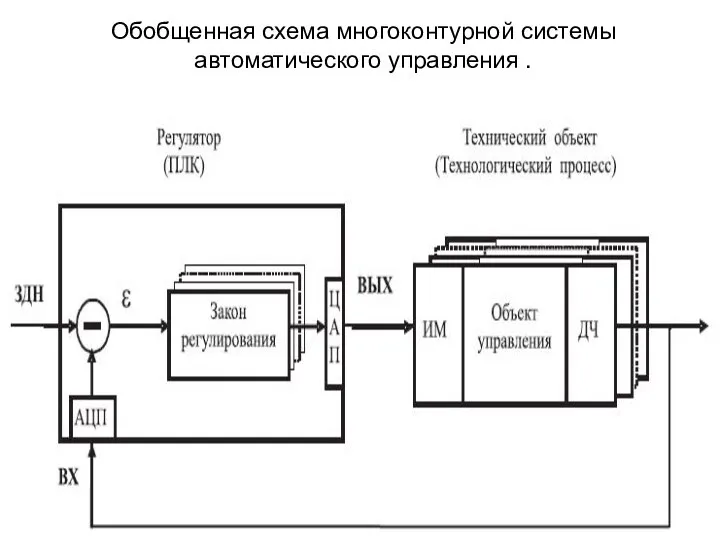

- 3. Обобщенная схема многоконтурной системы автоматического управления .

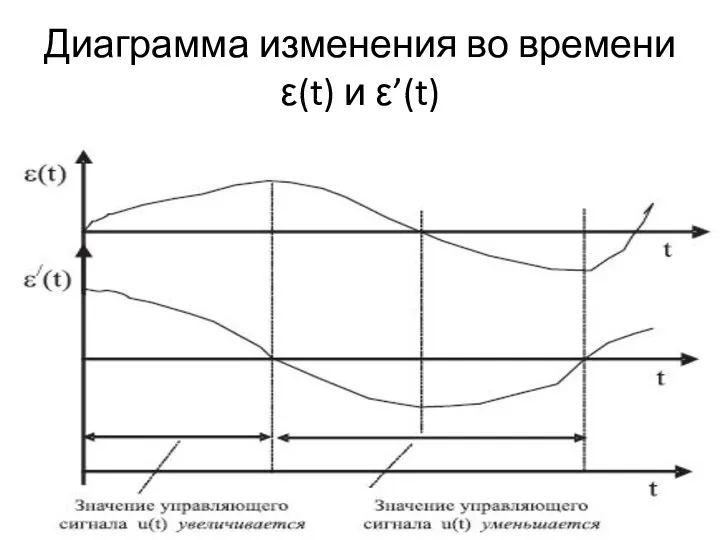

- 5. Диаграмма изменения во времени ε(t) и ε’(t)

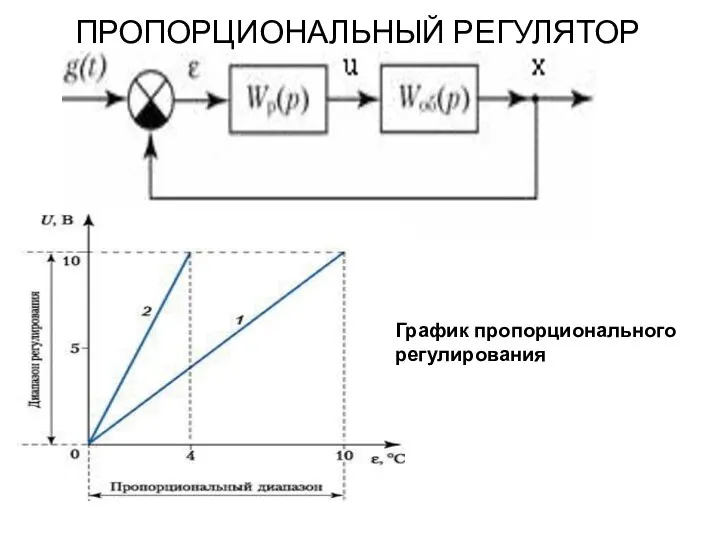

- 6. ПРОПОРЦИОНАЛЬНЫЙ РЕГУЛЯТОР График пропорционального регулирования

- 7. Переходный процесс при пропорциональном регулировании

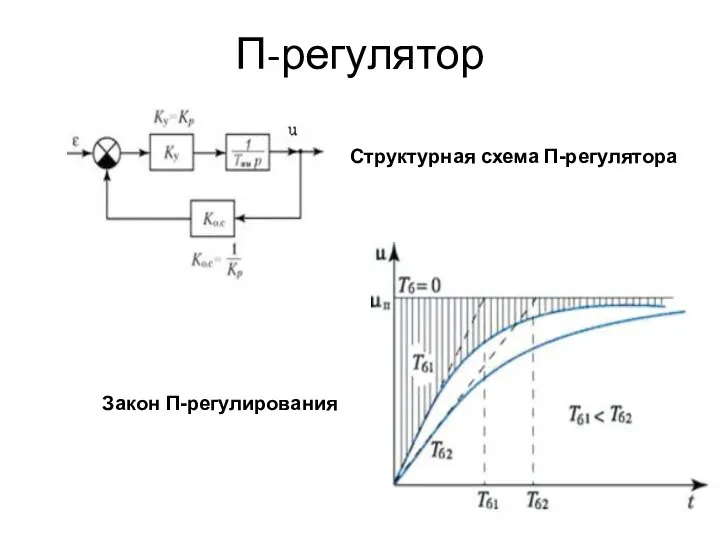

- 8. П-регулятор Структурная схема П-регулятора Закон П-регулирования

- 9. Структурная схема идеальных ПИ-регуляторов

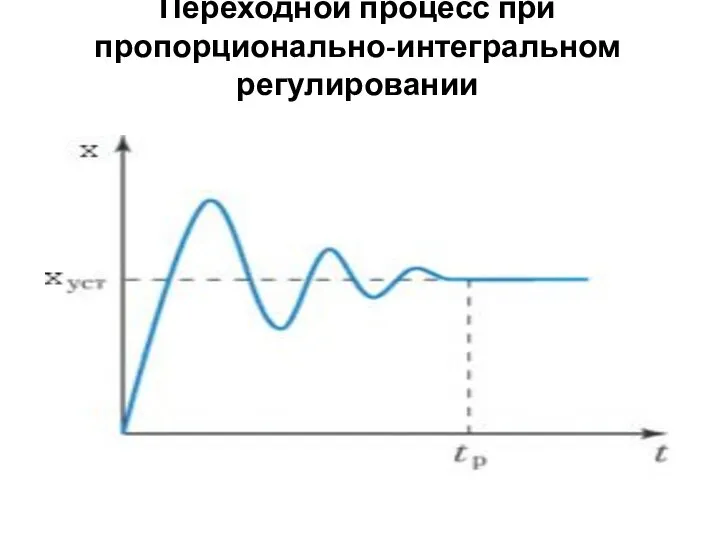

- 10. Переходной процесс при пропорционально-интегральном регулировании

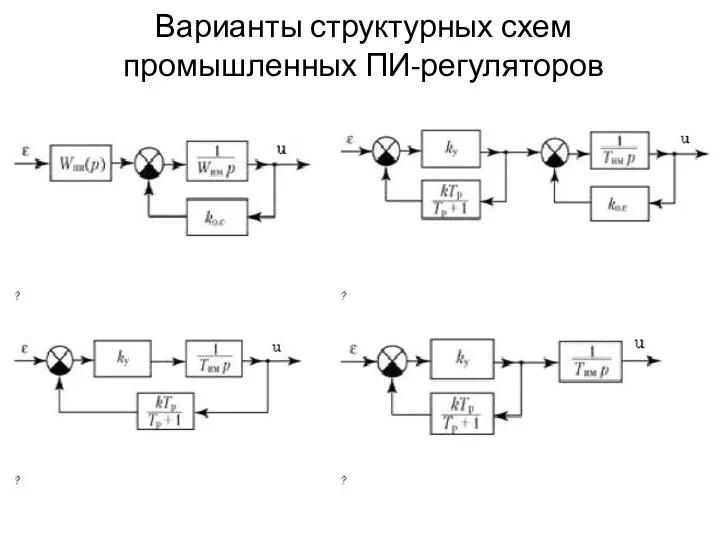

- 11. Варианты структурных схем промышленных ПИ-регуляторов

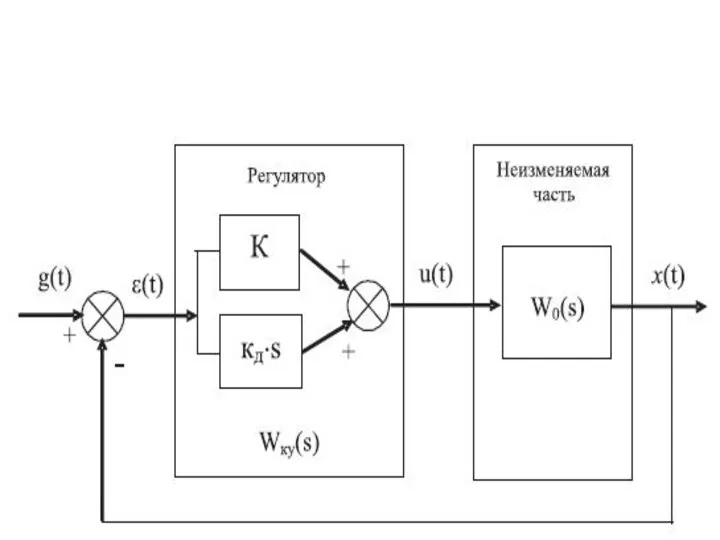

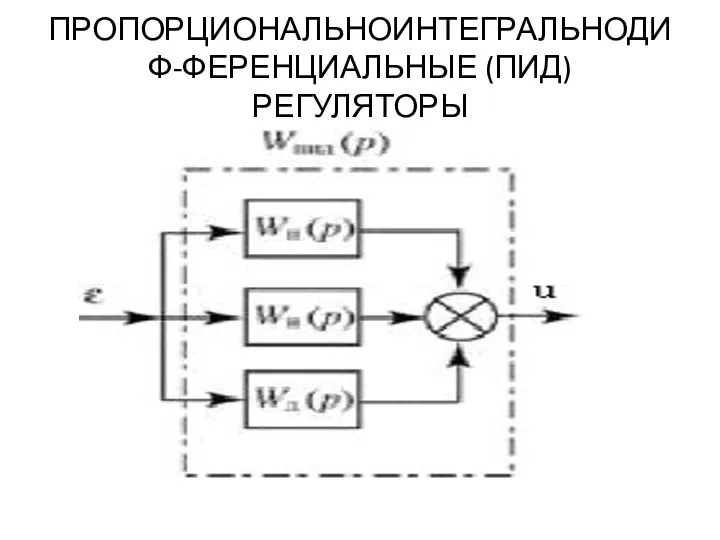

- 12. ПРОПОРЦИОНАЛЬНОИНТЕГРАЛЬНОДИФ-ФЕРЕНЦИАЛЬНЫЕ (ПИД) РЕГУЛЯТОРЫ

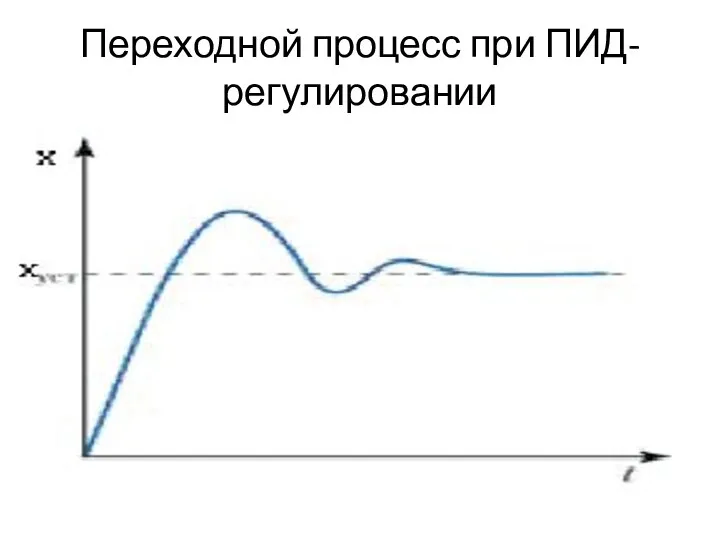

- 13. Переходной процесс при ПИД- регулировании

- 14. БИБЛИОТЕКА АЛГОРИТМОВ РЕГУЛИРОВАНИЯ В ПАКЕТЕ UNITY PRO

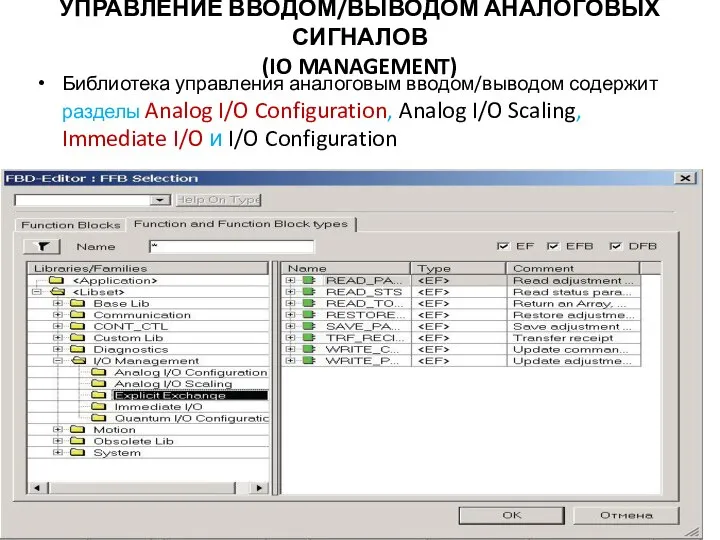

- 15. УПРАВЛЕНИЕ ВВОДОМ/ВЫВОДОМ АНАЛОГОВЫХ СИГНАЛОВ (IO MANAGEMENT) Библиотека управления аналоговым вводом/выводом содержит разделы Analog I/O Configuration, Analog

- 16. УСТРОЙСТВА ОБРАБОТКИ ДАННЫХ (CONDITIONING) Здесь представлены алгоритмы динамических преобразований: фильтр 1-го порядка, вычислитель производной со сглаживанием,

- 17. Функциональные блоки контура регулирования DTIME (Dead Time) – задержка. Этот блок реализует функцию чистого запаздывания в

- 18. Функциональные блоки контура регулирования (продолжение) LEAD (Differentiator with Delay) – дифференцирование с задержкой, вычисление производной со

- 19. Функциональные блоки контура регулирования (продолжение) TOTALIZER (Totalling Unit) – сумматор (накопитель), суммирующая функция, предназначенная для представления

- 20. РЕГУЛЯТОРЫ (CONTROLLER) С помощью блоков FFB, входящих в раздел «Controller», могут осуществляться следующие алгоритмы регулирования и

- 21. РЕГУЛЯТОРЫ (продолжение) PI_B (Basic PI Controller) – базовый ПИ-регулятор; этот блок рекомендуется использовать в случае грубой

- 22. РЕГУЛЯТОРЫ (продолжение) SAMPLETM (Sample time) – шаблон времени; этот блок используется для управления блоками после холодного

- 23. РЕГУЛЯТОРЫ (продолжение) STEP3 (3-Position On/Off Controller) – трех позиционный регулятор, трехпозиционное реле с зоной нечувствительности и

- 24. Структурная схема САР с ПИД-регулятором FGEN-функциональный блок является генератором задающего воздействия g; а блок PID –

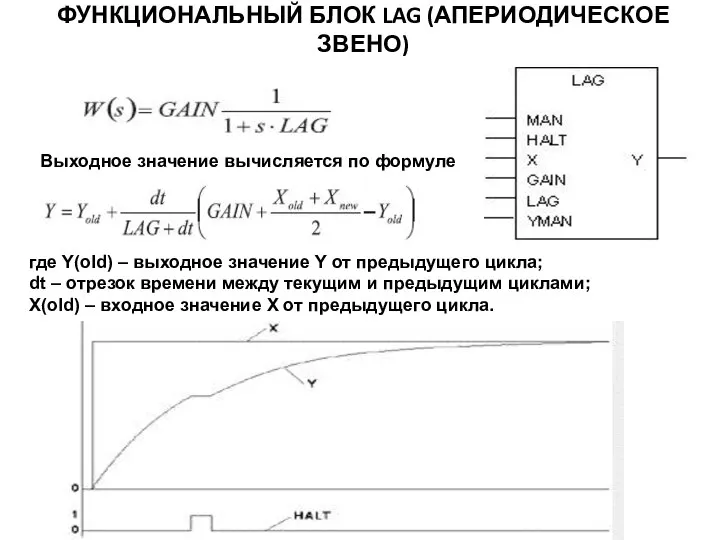

- 25. ФУНКЦИОНАЛЬНЫЙ БЛОК LAG (АПЕРИОДИЧЕСКОЕ ЗВЕНО) Выходное значение вычисляется по формуле где Y(old) – выходное значение Y

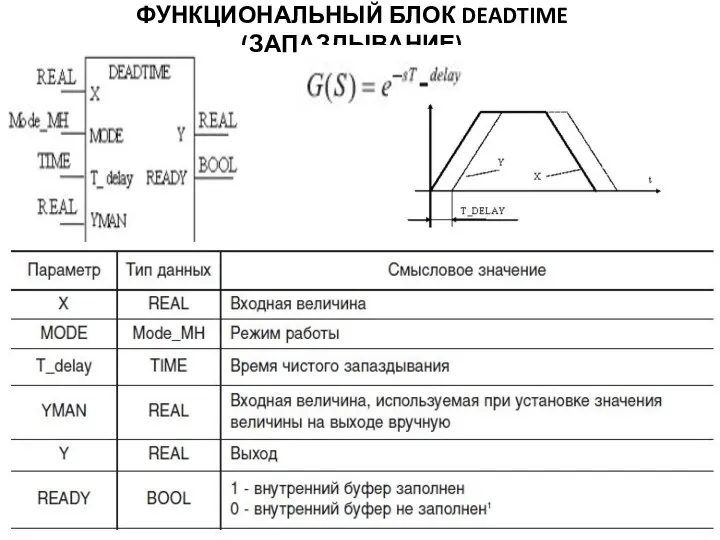

- 26. ФУНКЦИОНАЛЬНЫЙ БЛОК DEADTIME (ЗАПАЗДЫВАНИЕ)

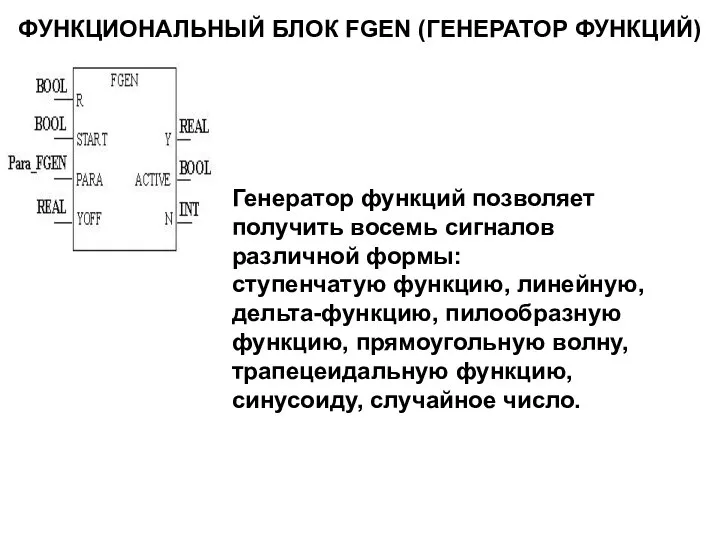

- 27. ФУНКЦИОНАЛЬНЫЙ БЛОК FGEN (ГЕНЕРАТОР ФУНКЦИЙ) Генератор функций позволяет получить восемь сигналов различной формы: ступенчатую функцию, линейную,

- 29. PID-регулятор

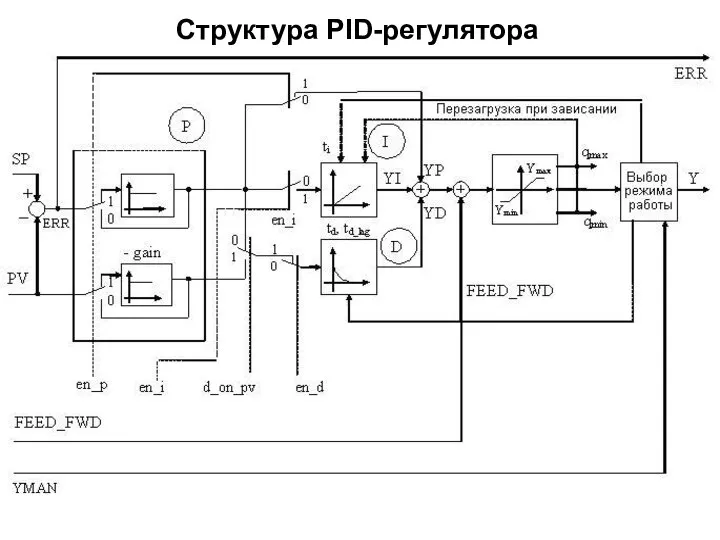

- 30. Структура PID-регулятора

- 32. Скачать презентацию

Комплект интерактивных плакатов "ФОНЕТИКА" - презентация для начальной школы

Комплект интерактивных плакатов "ФОНЕТИКА" - презентация для начальной школы PsychedelicWaves из моих OneNote Google. Документы

PsychedelicWaves из моих OneNote Google. Документы Агния Барто - творчество

Агния Барто - творчество Заправка воздушного судна ТУ-134А топливом

Заправка воздушного судна ТУ-134А топливом Силурийский период 443 млн.л.н. – 416 млн.л.н.

Силурийский период 443 млн.л.н. – 416 млн.л.н. Конденсатори

Конденсатори Химия элементов s-элементы

Химия элементов s-элементы  Титаны эпохи Ренессанса

Титаны эпохи Ренессанса Презентация ПУШНО-МЕХОВЫЕ ИЗДЕЛИЯ

Презентация ПУШНО-МЕХОВЫЕ ИЗДЕЛИЯ Электронный репетитор

Электронный репетитор Презентация Удачи

Презентация Удачи Капітальний та поточний ремонт об'єктів благоустрою зеленого господарства

Капітальний та поточний ремонт об'єктів благоустрою зеленого господарства Клеточный цикл жизни, деление клетки

Клеточный цикл жизни, деление клетки А.С.Пушкин. Поэт-Романтик

А.С.Пушкин. Поэт-Романтик Класифікація держав за їхньою формою

Класифікація держав за їхньою формою Спортивный досуг девятиклассника. Спорт в нашей жизни

Спортивный досуг девятиклассника. Спорт в нашей жизни Предмет и задачи судебной экспертизы

Предмет и задачи судебной экспертизы Строки. Массивы символов в C++. Обзор. (Занятие 8)

Строки. Массивы символов в C++. Обзор. (Занятие 8) Мир вокруг нас Кто такие насекомые

Мир вокруг нас Кто такие насекомые Евгений Чарушин - художник и писатель (1901 – 1965)

Евгений Чарушин - художник и писатель (1901 – 1965) Технология JSF (Java Server Faces)

Технология JSF (Java Server Faces) Мова програмування Python

Мова програмування Python Шедевры архитектуры

Шедевры архитектуры Способы подготовки различных поверхностей под оклейку различными видами обоев

Способы подготовки различных поверхностей под оклейку различными видами обоев Школа – дом родной МОУ «Средняя общеобразовательная школа д. Македоновка»

Школа – дом родной МОУ «Средняя общеобразовательная школа д. Македоновка» Розбирання ноудбука Asus S500CA-RSI5T02

Розбирання ноудбука Asus S500CA-RSI5T02 Введение в дисциплину «Государственная экономическая политика»

Введение в дисциплину «Государственная экономическая политика» Рабочие чертежи деталей

Рабочие чертежи деталей