Содержание

- 2. Інформаційно-методичне забезпечення: Лекція. Робочий зошит студента. Презентація УБЗ 2.1. Устрій та бойове застосування КЗА 86Ж6. Частина

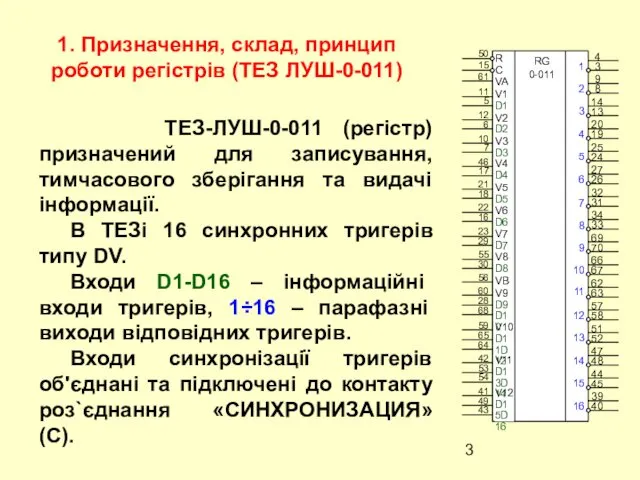

- 3. 1. Призначення, склад, принцип роботи регістрів (ТЕЗ ЛУШ-0-011) ТЕЗ-ЛУШ-0-011 (регістр) призначений для записування, тимчасового зберігання та

- 4. Для керування синхронізацією служать входи «ГРУППОВОЕ РАЗРЕШЕНИЕ» (Va,Vb) і «РАЗРЕШЕНИЕ» (V1-V8, V9-V12).

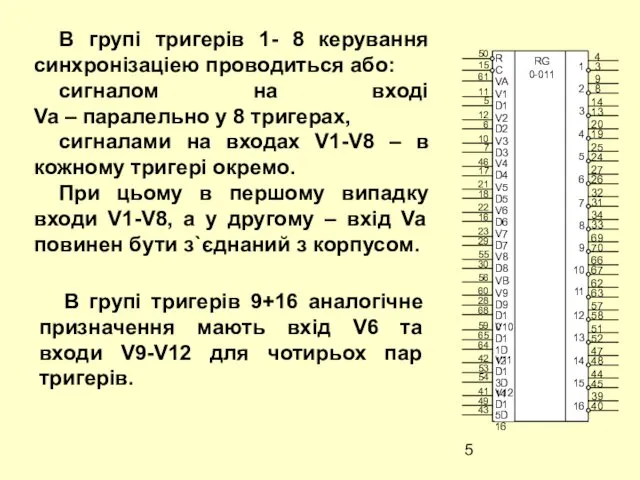

- 5. В групі тригерів 1- 8 керування синхронізаціею проводиться або: сигналом на вході Va – паралельно у

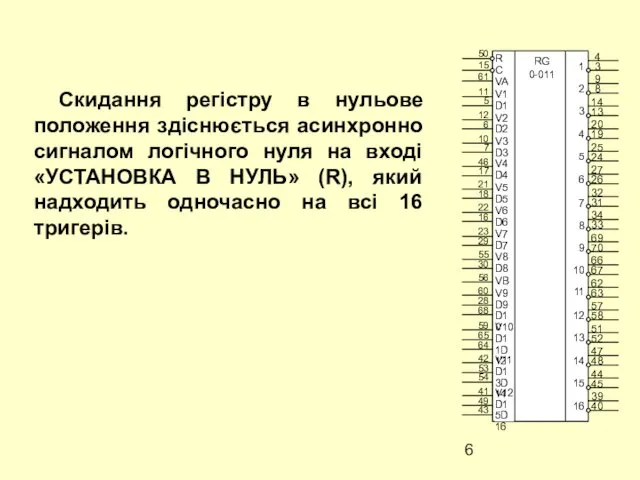

- 6. Скидання регістру в нульове положення здіснюється асинхронно сигналом логічного нуля на вході «УСТАНОВКА В НУЛЬ» (R),

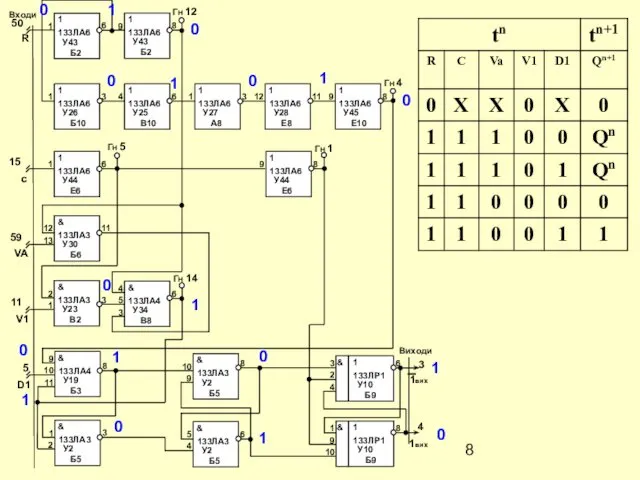

- 7. Представлена таблиця істинності DV тригера при керуванні синхронізацією сигналом на входи Vа (паралельно у 8 тригерах)

- 8. 0 0 0 0 1 0 0 1 1 0 1 0 1 1 0 1

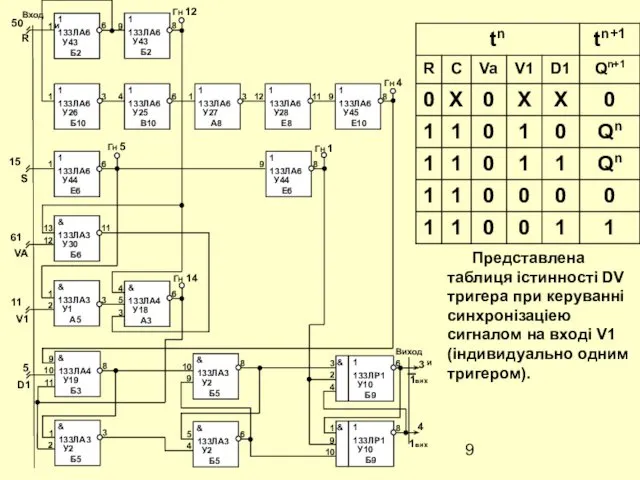

- 9. Представлена таблиця істинності DV тригера при керуванні синхронізаціею сигналом на вході V1 (індивидуально одним тригером).

- 10. 2. Призначення, склад, принцип роботи. Лічильник (ТЕЗ-ЛУШ-0-022), суматор (ТЕЗ ЛУШ-0-009), шифратор (ТЕЗ ЛУШ-1-016), дешифратор ( ТЕЗ

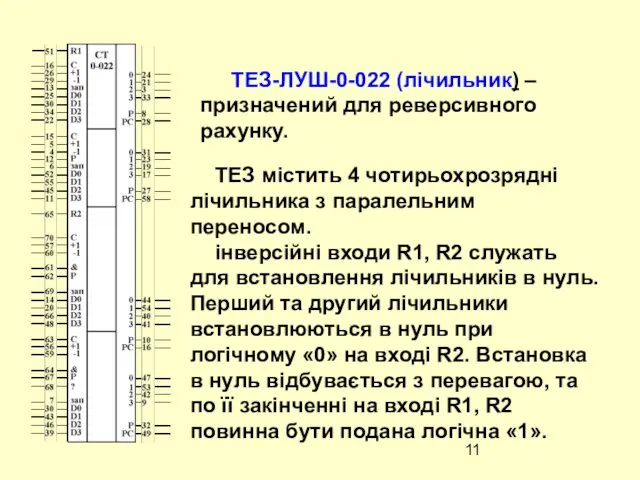

- 11. ТЕЗ-ЛУШ-0-022 (лічильник) – призначений для реверсивного рахунку. ТЕЗ містить 4 чотирьохрозрядні лічильника з паралельним переносом. інверсійні

- 12. Лічильники побудовані на JК-тригерах. Записування розрядів початкового числа (входи D0-D3) виконується паралельно та асинхронно, попереднє встановлення

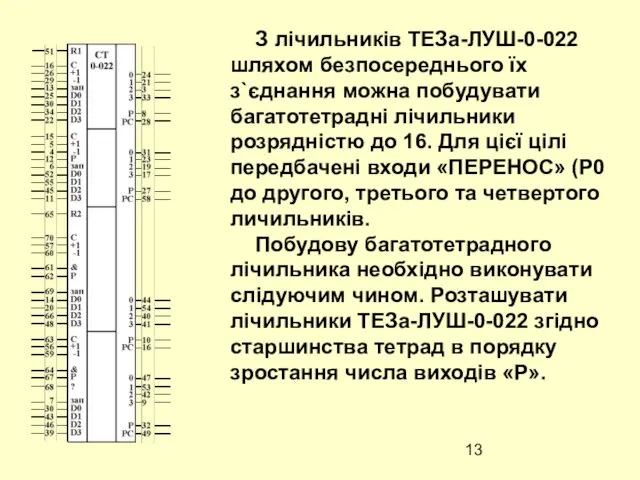

- 13. З лічильників ТЕЗа-ЛУШ-0-022 шляхом безпосереднього їх з`єднання можна побудувати багатотетрадні лічильники розрядністю до 16. Для цієї

- 14. Підключити до входів Р кожної тетради виходи Р попередніх тетрад. Використати в якості молодшої тетради перший

- 15. ТЕЗ-ЛУШ-0-009 (суматор) являє собою комбінаційну схему, передбачену для алгебраїчного додавання (А + Б) двох чисел, а

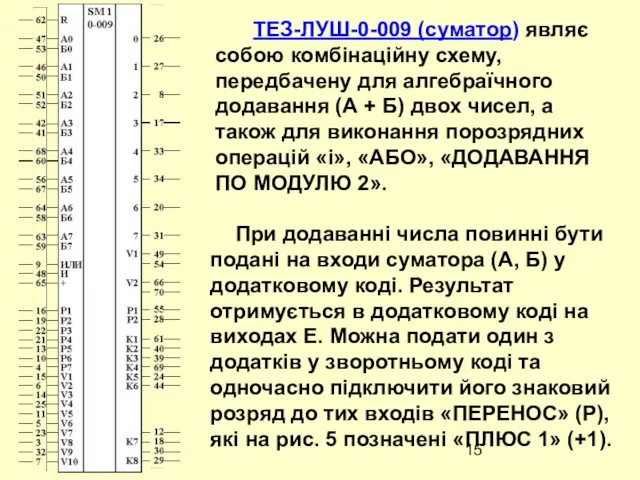

- 16. Дія А-Б реалізується як складання А + (-Б). Якщо виходити з додаткових кодів чисел А, Б

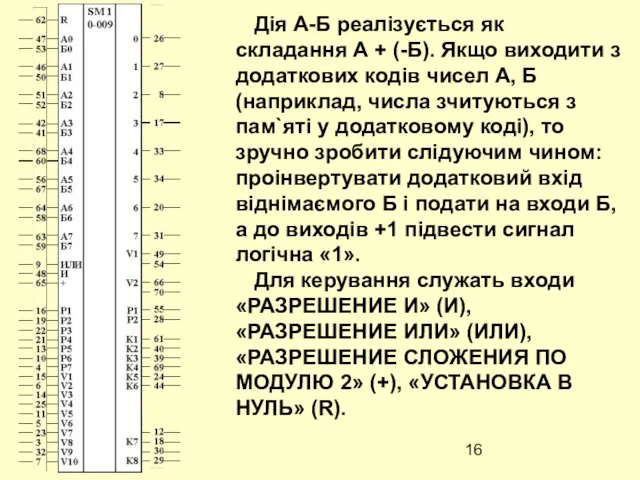

- 17. З метою побудови з ТЕЗ-ЛУШ-0-009 багатотетрадних суматорів надпаралельного типу на роз`єднання ТЕЗу виведені сигнали «ПЕРЕНОС СТАРШЕЙ

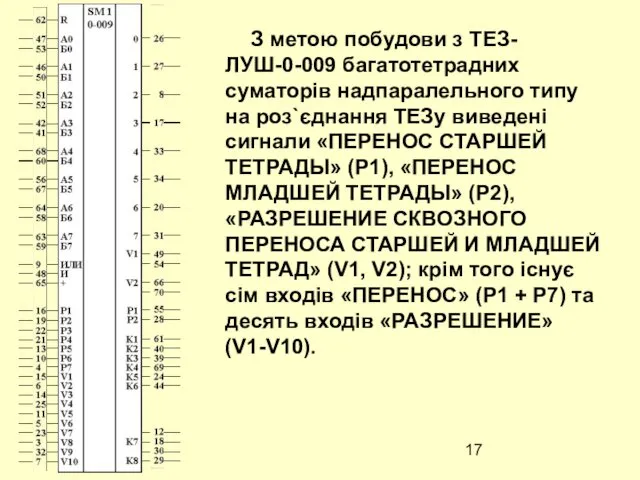

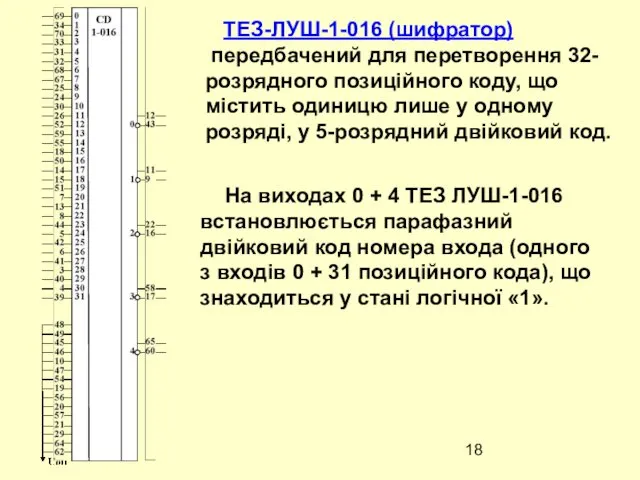

- 18. ТЕЗ-ЛУШ-1-016 (шифратор) передбачений для перетворення 32-розрядного позиційного коду, що містить одиницю лише у одному розряді, у

- 19. Безпосередні входи позиційного коду повинні бути підключені до корпусу. З 2, 3, 4 ТЕЗів ЛУШ-1-016 можна

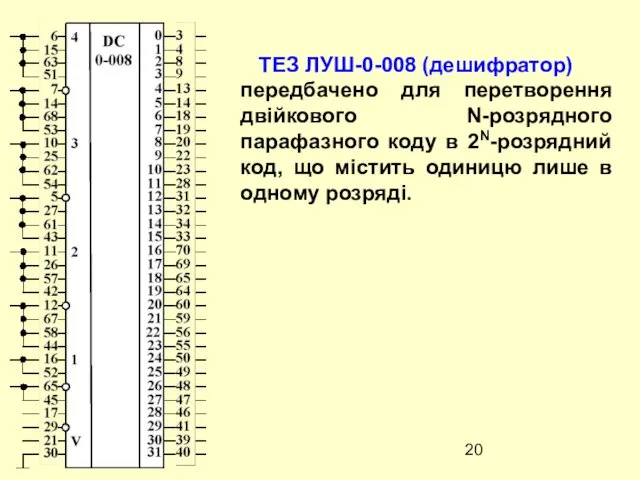

- 20. ТЕЗ ЛУШ-0-008 (дешифратор) передбачено для перетворення двійкового N-розрядного парафазного коду в 2N-розрядний код, що містить одиницю

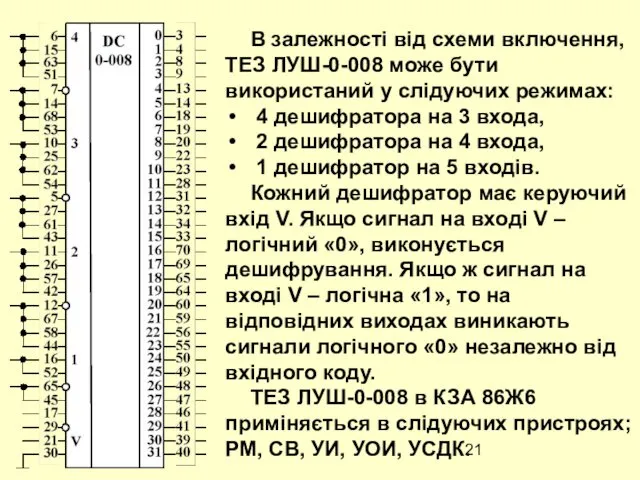

- 21. В залежності від схеми включення, ТЕЗ ЛУШ-0-008 може бути використаний у слідуючих режимах: 4 дешифратора на

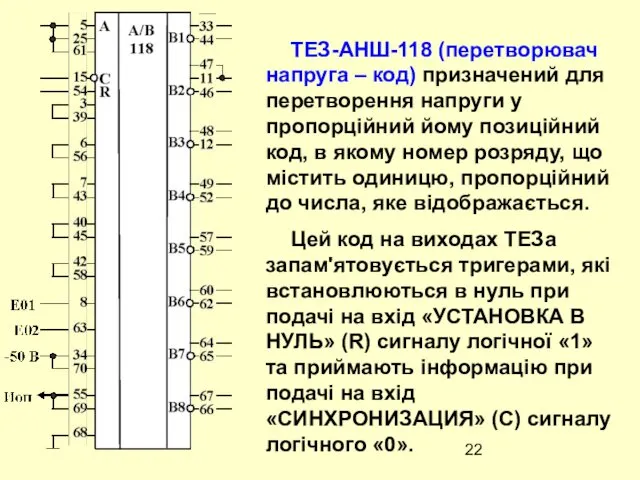

- 22. ТЕЗ-АНШ-118 (перетворювач напруга – код) призначений для перетворення напруги у пропорційний йому позиційний код, в якому

- 23. При прийомі інформації на вході R повинен бути присутнім сигнал логічного «0». Один ТЕЗ-АНШ-118 дозволяє отримати

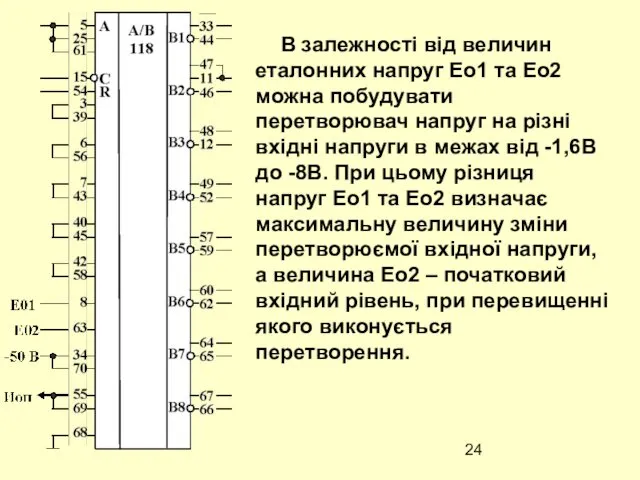

- 24. В залежності від величин еталонних напруг Ео1 та Ео2 можна побудувати перетворювач напруг на різні вхідні

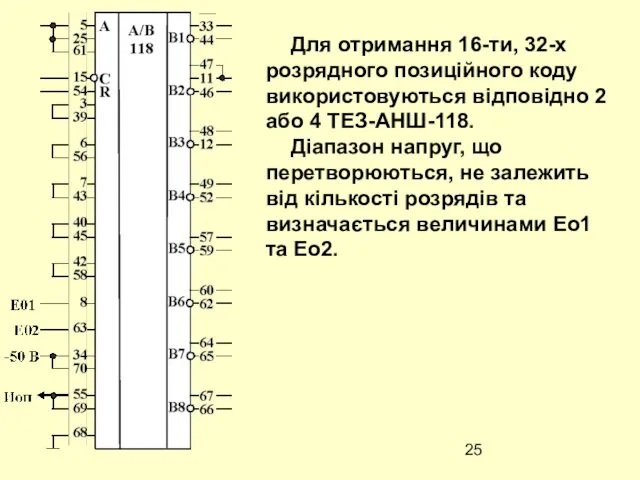

- 25. Для отримання 16-ти, 32-х розрядного позиційного коду використовуються відповідно 2 або 4 ТЕЗ-АНШ-118. Діапазон напруг, що

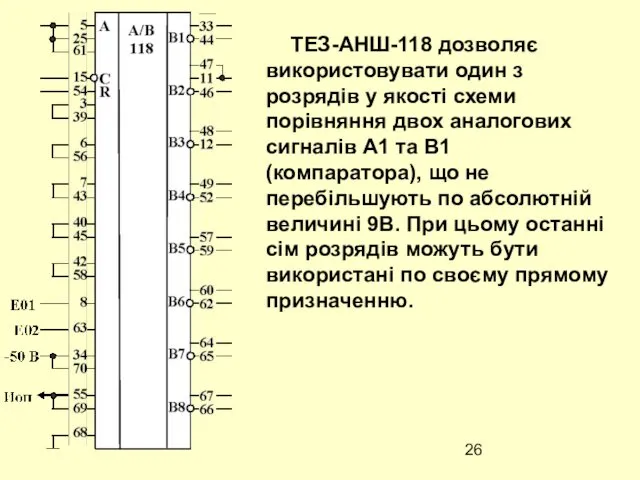

- 26. ТЕЗ-АНШ-118 дозволяє використовувати один з розрядів у якості схеми порівняння двох аналогових сигналів А1 та В1

- 28. Скачать презентацию

Межведомственное взаимодействие по развитию юнармейского движения в Кемеровской области

Межведомственное взаимодействие по развитию юнармейского движения в Кемеровской области Эксплуатация и ремонт вооружения и средств радиационной, химической и биологической защиты (Занятие № 4)

Эксплуатация и ремонт вооружения и средств радиационной, химической и биологической защиты (Занятие № 4) Основи бойового застосування артилерійської батареї в обороні та наступі

Основи бойового застосування артилерійської батареї в обороні та наступі Вооруженные Силы Российской Федерации: структура, предназначение, вооружение видов и родов войск

Вооруженные Силы Российской Федерации: структура, предназначение, вооружение видов и родов войск Войсковой прибор химической разведки ВПХР

Войсковой прибор химической разведки ВПХР ИЛ-2 (штурмовик)

ИЛ-2 (штурмовик) Меры безопасности при обращении с оружием, имитационными средствами и боеприпасами

Меры безопасности при обращении с оружием, имитационными средствами и боеприпасами Национальная безопасность России

Национальная безопасность России АСДНР. Содержание и организация мероприятий по локализации и ликвидации последствий чрезвычайных ситуаций

АСДНР. Содержание и организация мероприятий по локализации и ликвидации последствий чрезвычайных ситуаций Подготовка Стрельбы и управления огнем

Подготовка Стрельбы и управления огнем Боеприпасы наземной артиллерии

Боеприпасы наземной артиллерии Отечеству служить не по приказу…

Отечеству служить не по приказу… Рабочая тетрадь по профессиональной служебной подготовке и занятий в ШПОМ

Рабочая тетрадь по профессиональной служебной подготовке и занятий в ШПОМ Топографические карты. (Тема 2.1)

Топографические карты. (Тема 2.1) Правила стрельбы. Огневая подготовка

Правила стрельбы. Огневая подготовка Ядерное оружие

Ядерное оружие Порядок неполной разборки и сборки АК

Порядок неполной разборки и сборки АК Военно-Воздушные Силы РФ

Военно-Воздушные Силы РФ Союз десантников России

Союз десантников России Ядерное оружие

Ядерное оружие Теоретичні основи метрології. Похибки засобів вимірювань. Метрологічна надійність засобів вимірювань

Теоретичні основи метрології. Похибки засобів вимірювань. Метрологічна надійність засобів вимірювань Будова і дія частин та механізмів автомата АК74 (Заняття 1.6)

Будова і дія частин та механізмів автомата АК74 (Заняття 1.6) Складові морально-психологічного забезпечення підготовки та застосування Збройних Сил України та їх характеристика

Складові морально-психологічного забезпечення підготовки та застосування Збройних Сил України та їх характеристика Приёмы рукопашного боя с оружием

Приёмы рукопашного боя с оружием Воинские звания

Воинские звания Письмо солдату

Письмо солдату Технические средства воспитания, классификация и методика их использования

Технические средства воспитания, классификация и методика их использования