Содержание

- 2. Общие принципы управления виртуальной памятью в Win32 Менеджер виртуальной памяти и архитектура Win32 API

- 3. Менеджер виртуальной памяти Менеджер виртуальной памяти (VMM) является составной частью ядра ОС. Приложения не могут получить

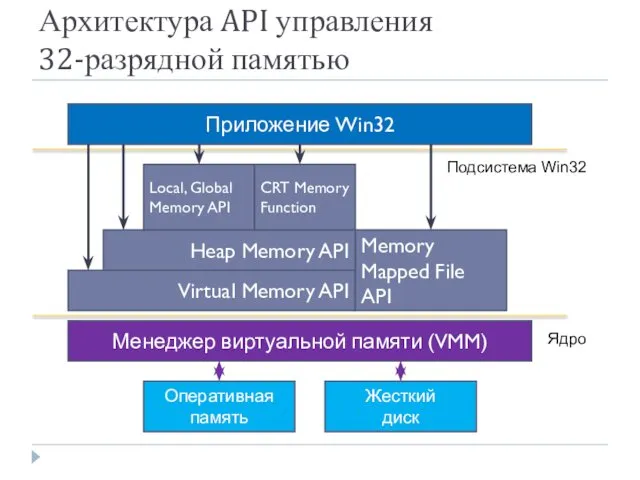

- 4. Архитектура API управления 32-разрядной памятью

- 5. Интерфейсы управления памятью Virtual Memory API – набор функций, позволяющих приложению работать с виртуальным адресным пространством:

- 6. Виртуальное адресное пространство процесса 2 Гб для пользовательского пространства 2 Гб для нужд ОС 3 Гб

- 7. Расширенное пользовательское пространство Чтобы включить в Windows Server 2003 и Windows 2000 расширенное пользовательское пространство, необходимо

- 8. Страничное преобразование Виртуальная память в Windows 2000+ имеет страничную организацию. Каждому процессу Windows назначается свой каталог

- 9. Размер страницы

- 10. Средства защиты памяти Объектно-ориентированная защита памяти. Каждый раз, когда процесс открывает указатель на блок адресов, монитор

- 11. Общие принципы управления виртуальной памятью в Win32 Управлению памятью на архитектуре IA-32

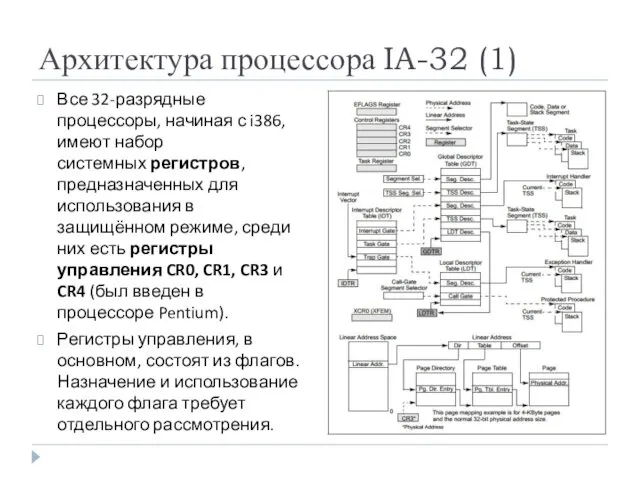

- 12. Архитектура процессора IA-32 (1) Все 32-разрядные процессоры, начиная с i386, имеют набор системных регистров, предназначенных для

- 13. Архитектура процессора IA-32 (2) Например, младший бит из регистра CR0 называется PE (Protection Enable). Если установить

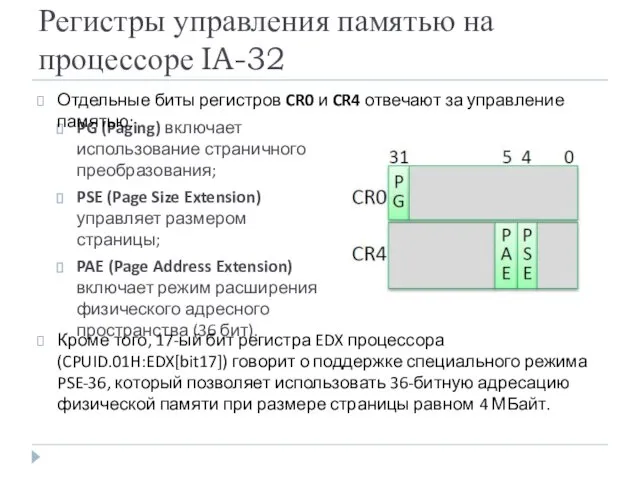

- 14. Регистры управления памятью на процессоре IA-32 PG (Paging) включает использование страничного преобразования; PSE (Page Size Extension)

- 15. Режим PAE Расширение физических адресов (Physical Address Extension – РАЕ) – режим работы встроенного блока управления

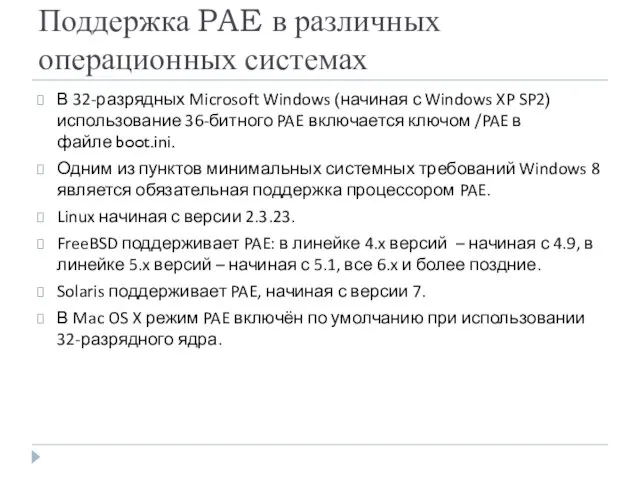

- 16. Поддержка PAE в различных операционных системах В 32-разрядных Microsoft Windows (начиная с Windows XP SP2) использование

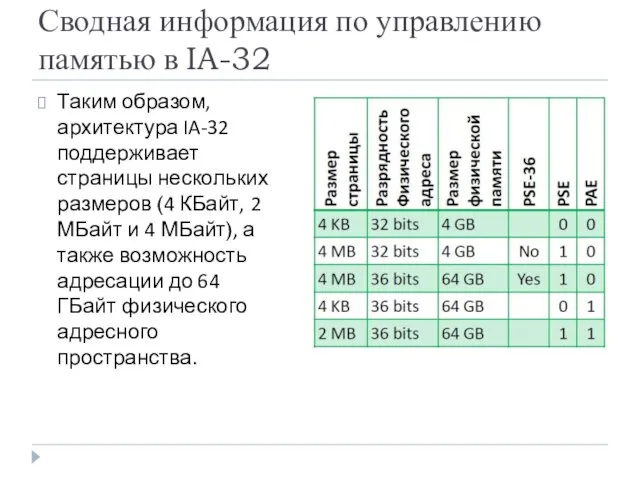

- 17. Сводная информация по управлению памятью в IA-32 Таким образом, архитектура IA-32 поддерживает страницы нескольких размеров (4

- 18. Общие принципы управления виртуальной памятью в Win32 Реализация страничного преобразования

- 19. Формат 32-разрядного виртуального адреса в системах x86 (страница 4 КБайт) Старшие 10 разрядов адреса определяют номер

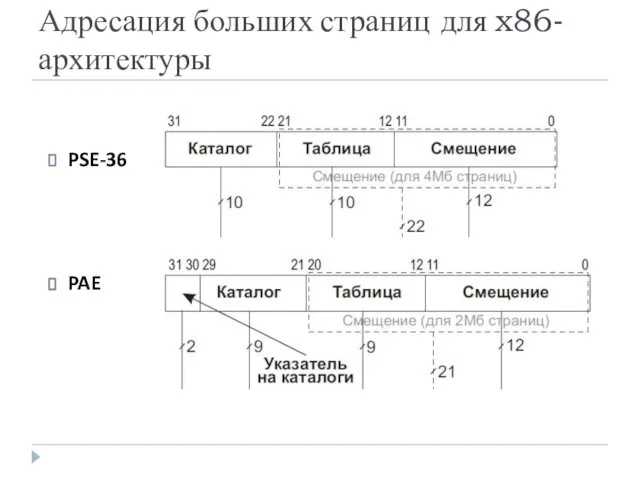

- 20. Адресация больших страниц для x86-архитектуры PSE-36 PAE

- 21. Вопрос Какие проблемы Вы видите при использовании драйверами операционной системы «больших» страниц?

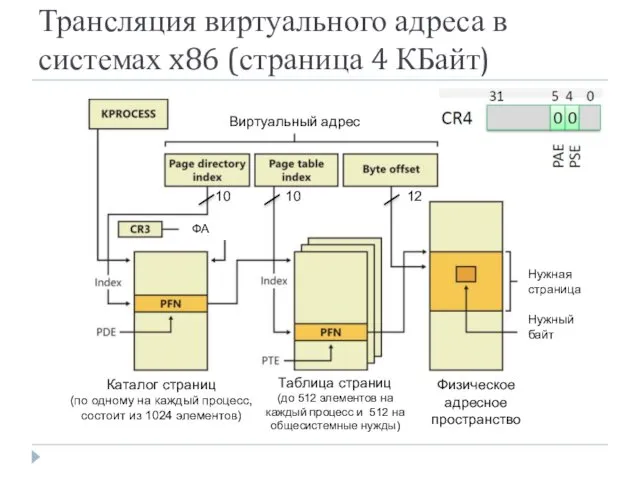

- 22. Трансляция виртуального адреса в системах x86 (страница 4 КБайт) Виртуальный адрес ФА 10 10 12

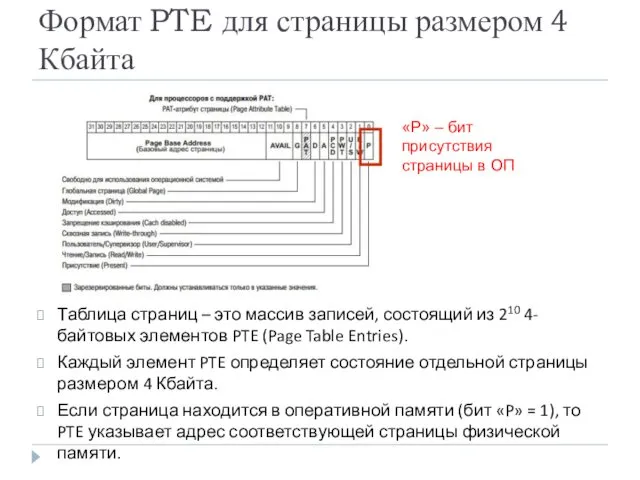

- 23. Формат PTE для страницы размером 4 Кбайта Таблица страниц – это массив записей, состоящий из 210

- 24. Биты PTE Global (G) – страница относится ко всем процессам Page Table Attribute Index (PAT) –

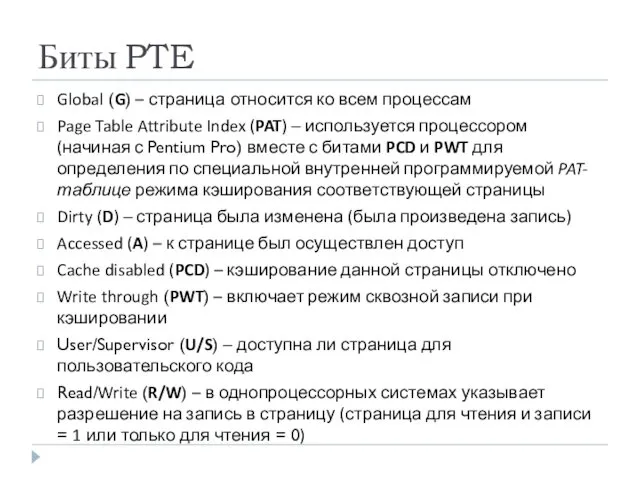

- 25. Каталог страниц и формат PDE для страниц размером 4 Кбайта Каталог страниц – это массив, состоящий

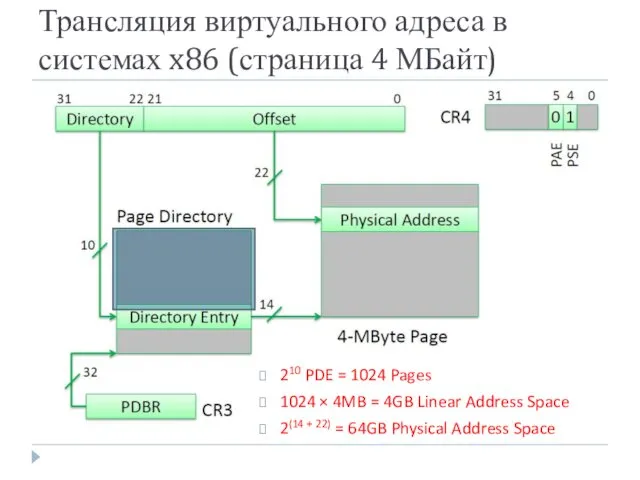

- 26. Трансляция виртуального адреса в системах x86 (страница 4 МБайт) 210 PDE = 1024 Pages 1024 ×

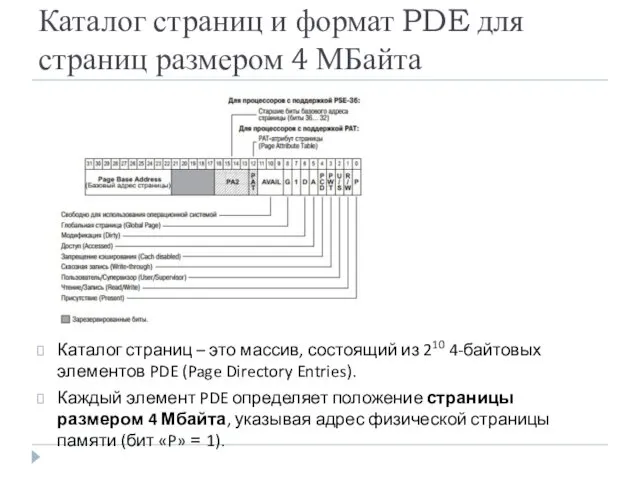

- 27. Каталог страниц и формат PDE для страниц размером 4 МБайта Каталог страниц – это массив, состоящий

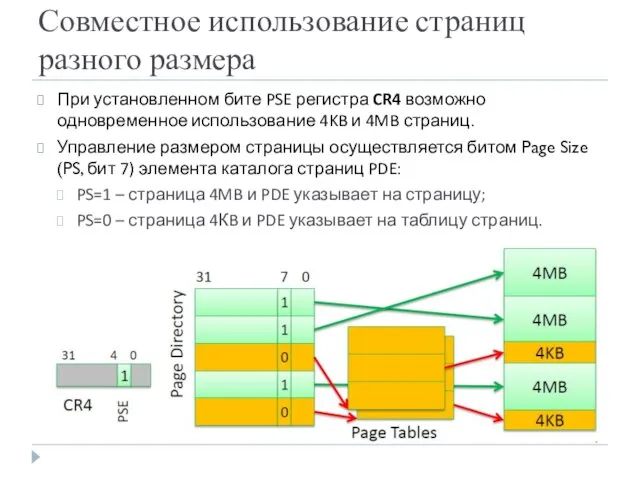

- 28. Совместное использование страниц разного размера При установленном бите PSE регистра CR4 возможно одновременное использование 4KB и

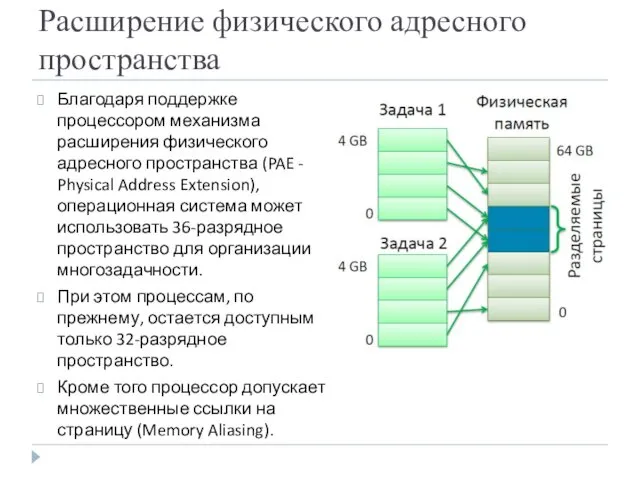

- 29. Расширение физического адресного пространства Благодаря поддержке процессором механизма расширения физического адресного пространства (PAE - Physical Address

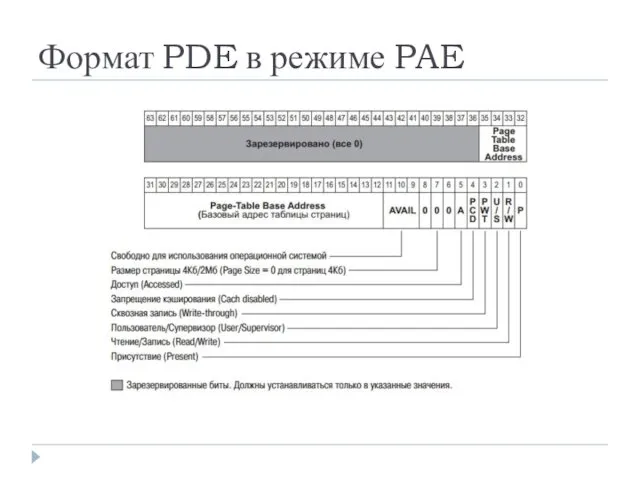

- 30. Формат PDE в режиме PAE

- 31. Реализация механизма PAE для страниц размером 4 Кбайта Записи PDE и PTE – 64 бита !

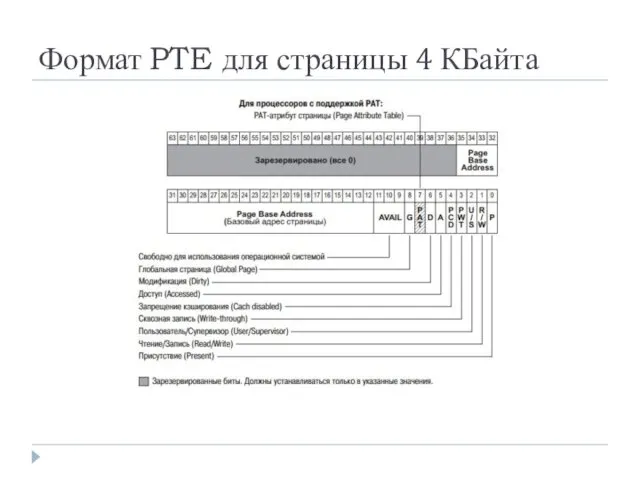

- 32. Формат PTE для страницы 4 КБайта

- 33. Формат PDE для страницы 2 МБайта

- 34. Практическое использование «больших» страниц Для пользовательского приложения – выделение виртуальной памяти с помощью вызова функции VirtualAlloc

- 35. Общие принципы управления виртуальной памятью в Win32 Ускорение страничных преобразований

- 36. Реализация TLB-кэша в Windows Часто используемым страницам (точнее их PTE) соответствуют элементы в TLB (Translation Lookside

- 37. Схема реализации TLB

- 38. Эффективность использования больших страниц для TLB-кэша Недостатком «маленьких» страниц является неэффективное использование TLB, так для страниц

- 39. Проблемы использования TLB При переключении процессов нужно добиться того, чтобы новый процесс не видел в ассоциативной

- 40. Общие принципы управления виртуальной памятью в Win32 Стратегия управления виртуальной памятью и свопинг

- 41. Стратегия управления виртуальной памятью Стратегия выборки (fetch policy) Стратегия размещения (placement policy) Стратегия замещения (replacement policy)

- 42. Стратегия выборки Стратегия выборки (fetch policy): Выборка определяет, в какой момент необходимо переписать страницу с диска

- 43. Стратегия размещения Стратегия выборки (fetch policy) Стратегия размещения (placement policy): Размещение определяет, в какое место оперативной

- 44. Стратегия замещения Стратегия выборки (fetch policy) Стратегия размещения (placement policy) Стратегия замещения (replacement policy): Замещение начинает

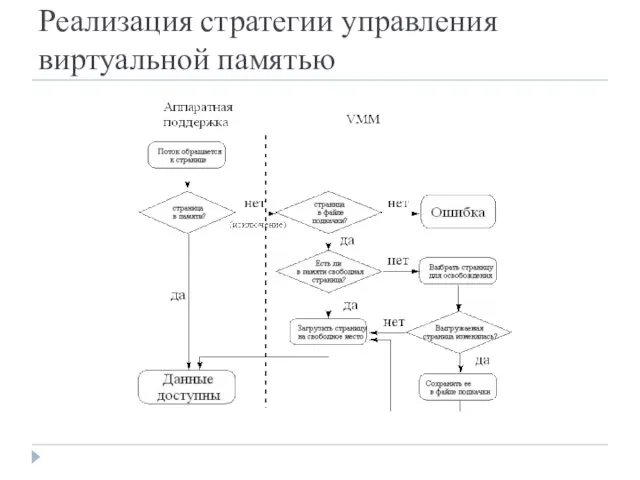

- 45. Реализация стратегии управления виртуальной памятью

- 46. Свопинг Для того, чтобы обеспечить все линейное адресное пространство процесса физическими ячейками памяти, Windows применяет свопинг

- 47. Состояния страниц Valid или Active – страница используется процессом. Она реально существует в ОП и помечена

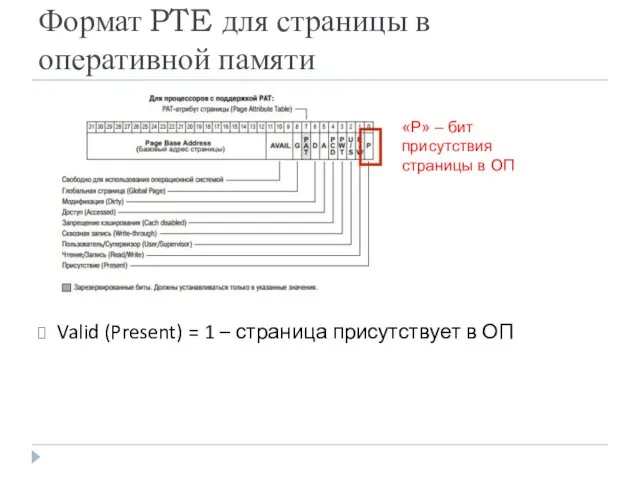

- 48. Формат PTE для страницы в оперативной памяти Valid (Present) = 1 – страница присутствует в ОП

- 49. Формат PTE для страницы в файле подкачки Valid (Present) = 0 – страница отсутствует в ОП

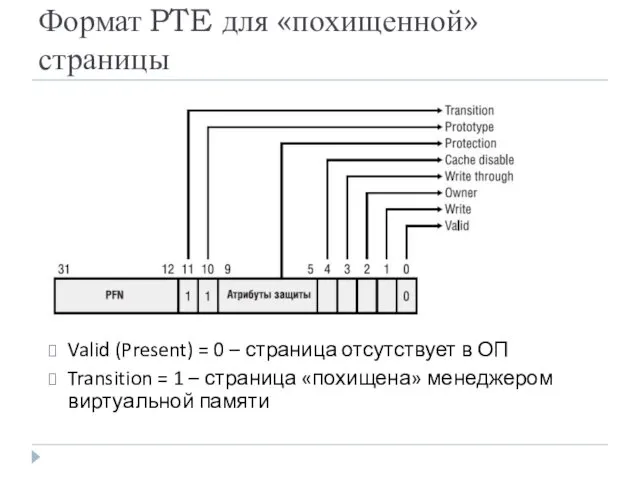

- 50. Формат PTE для «похищенной» страницы Valid (Present) = 0 – страница отсутствует в ОП Transition =

- 51. Таблица состояний страниц

- 52. Windows-реализация алгоритма замещения LRU VMM периодически просматривает список страниц с установленным флагом Present (Valid) и пытается

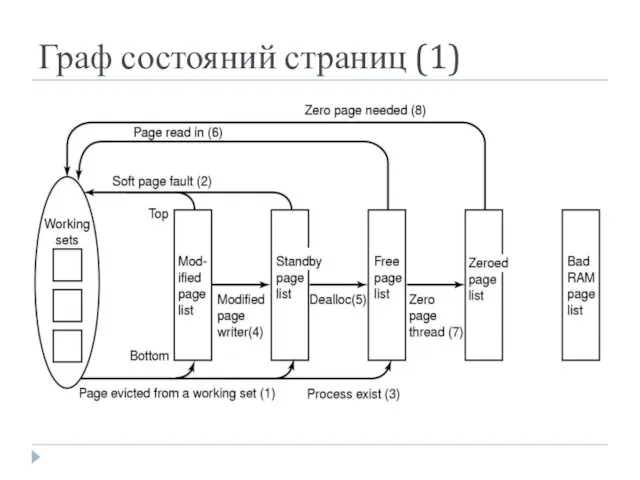

- 53. Граф состояний страниц (1)

- 55. Скачать презентацию

Урок 28_3кл_ДОТ_Добавление текста к рисунку

Урок 28_3кл_ДОТ_Добавление текста к рисунку Учебный курс Введение в цифровую электронику Лекция 6 Программирование микропроцессорной системы кандидат технических н

Учебный курс Введение в цифровую электронику Лекция 6 Программирование микропроцессорной системы кандидат технических н УФНС России по Самарской области

УФНС России по Самарской области MSI afterburner

MSI afterburner Определение количества информации. Решение задач

Определение количества информации. Решение задач Ячейка и диапазон

Ячейка и диапазон Компьютерные объекты. Информатика, 6 класс

Компьютерные объекты. Информатика, 6 класс Задачи на логические рассуждения

Задачи на логические рассуждения Pravidla užívání počítačů a počítačové sítě pro studenty na veterinární a farmaceutické univerzitě

Pravidla užívání počítačů a počítačové sítě pro studenty na veterinární a farmaceutické univerzitě Скоринг моделирование физических лиц: анализ содержания страниц в социальных сетях, поведенческий анализ

Скоринг моделирование физических лиц: анализ содержания страниц в социальных сетях, поведенческий анализ Глобальна інформаційна мережа Інтернет

Глобальна інформаційна мережа Інтернет Назначение и устройство компьютера (7 класс)

Назначение и устройство компьютера (7 класс) Циклические алгоритмы

Циклические алгоритмы Периферийные устройства персонального компьютера

Периферийные устройства персонального компьютера Технологія створення і ведення БД

Технологія створення і ведення БД Программаның физикалық жобалануы.физикалық жобалау процедурасы - тәртібі, аспабы, ресурсы, құжаттары. (Дәріс 8)

Программаның физикалық жобалануы.физикалық жобалау процедурасы - тәртібі, аспабы, ресурсы, құжаттары. (Дәріс 8) Курс HTML и CSS (5 занятие)

Курс HTML и CSS (5 занятие) Краткий обзор Семейство ОС Linux Дистрибутив Ubuntu

Краткий обзор Семейство ОС Linux Дистрибутив Ubuntu Методы научных исследований

Методы научных исследований HTML- формы. Практика

HTML- формы. Практика Информационные системы предприятий

Информационные системы предприятий Основы автоматизации проектирования РЭА. Вычисления в MATLAB. Числовые массивы. (Лекция 2)

Основы автоматизации проектирования РЭА. Вычисления в MATLAB. Числовые массивы. (Лекция 2) Устройство компьютера. Знакомство с компьютером

Устройство компьютера. Знакомство с компьютером О котах

О котах Представление информации. Кроссворды, ребусы, сканворды

Представление информации. Кроссворды, ребусы, сканворды Сохранение документа в различных текстовых форматах. Печать документа. 9 класс

Сохранение документа в различных текстовых форматах. Печать документа. 9 класс Базы данных. Access 2007

Базы данных. Access 2007 AWP инструкция

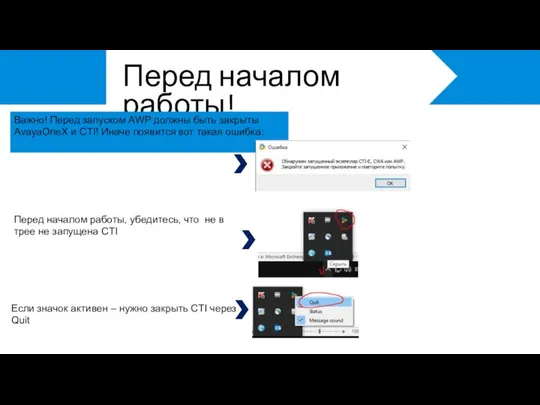

AWP инструкция