- Главная

- Информатика

- System buses (lecture 5)

Содержание

- 2. In what topology are combined bi-directional data transmission channels of PCIe? The PCI Express system bus

- 3. The PCI Express bus is controlled by a controller called the Host Bridge.

- 4. System bus organization based on PCI-E standard.

- 6. PCIe links from the chipset may attach to the following kinds of devices that implement PCIe:

- 7. What types of Layers does the PCIe protocol architecture encompass?

- 8. Physical: Consists of the actual wires carrying the signals, as well as circuitry and logic to

- 10. Скачать презентацию

In what topology are combined bi-directional data transmission channels of PCIe?

The

In what topology are combined bi-directional data transmission channels of PCIe?

The

Each of the devices participating in the exchange is connected to the opposite end of the channel. Thus, a point-to-point connection is established between each device and the switch. Thanks to this scheme, any device through a switch can be connected to any other, which is required from the system bus.

Can the PCIe connection be said to meet the system bus requirements?

How is information transmitted in PCIe?

Information in PCI Express is transmitted in packets, which can contain data, addresses, service requests, etc., and all types of packets are transmitted over the same lines as data packets. Information exchange is carried out simultaneously (but not synchronously) on all available lines.

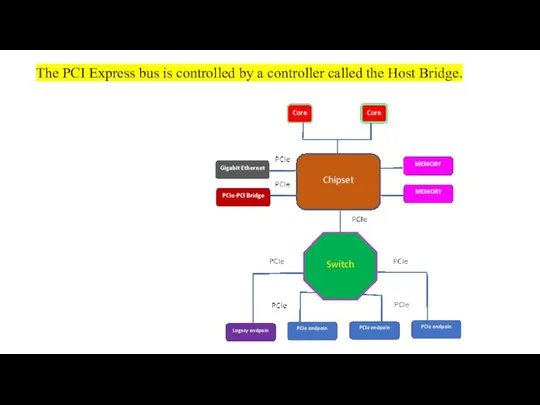

The PCI Express bus is controlled by a controller called the

The PCI Express bus is controlled by a controller called the

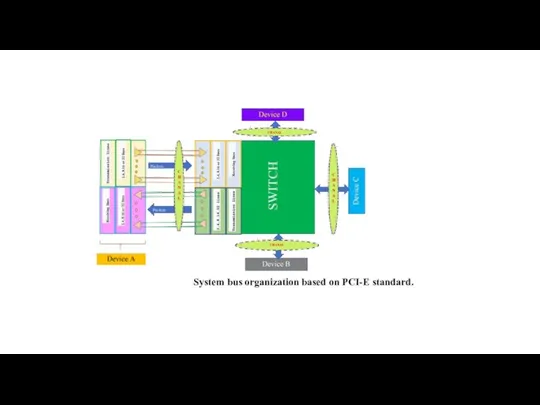

System bus organization based on PCI-E standard.

System bus organization based on PCI-E standard.

PCIe links from the chipset may attach to the following kinds

PCIe links from the chipset may attach to the following kinds

Switch: The switch manages multiple PCIe streams.

PCIe endpoint: An I/O device or controller that implements PCIe, such as a Gigabit Ethernet switch, a graphics or video controller, disk interface, or a communications controller.

Legacy endpoint: Legacy endpoint category is intended for existing designs that have been migrated to PCI Express, and it allows legacy behaviors such as use of I/O space and locked transactions. PCI Express endpoints are not permitted to require the use of I/O space at runtime and must not use locked transactions. By distinguishing these categories, it is possible for a system designer to restrict or eliminate legacy behaviors that have negative impacts on system performance and robustness.

PCIe/PCI bridge: Allows older PCI devices to be connected to PCIe-based systems.

What kind of devices that implement PCIe may attach to PCIe links from the chipset?

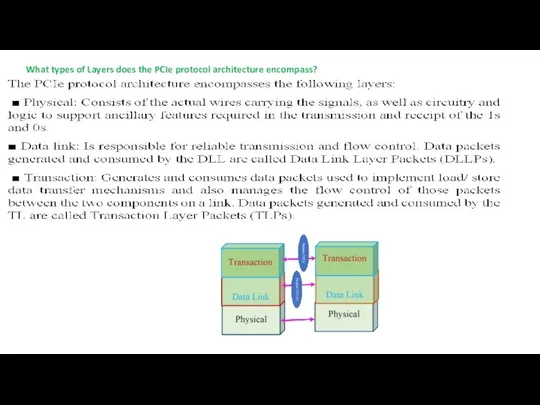

What types of Layers does the PCIe protocol architecture encompass?

What types of Layers does the PCIe protocol architecture encompass?

Physical: Consists of the actual wires carrying the signals, as

Physical: Consists of the actual wires carrying the signals, as

Data link: Is responsible for reliable transmission and flow control. Data packets generated and consumed by the DLL are called Data Link Layer Packets (DLLPs).

Transaction: Generates and consumes data packets used to implement load/ store data transfer mechanisms and also manages the flow control of those packets between the two components on a link. Data packets generated and consumed by the TL are called Transaction Layer Packets (TLPs).

Above the TL are software layers that generate read and write requests that are transported by the transaction layer to the I/O devices using a packet-based transaction protocol.

Mathcad 2000 Professional

Mathcad 2000 Professional Электронно-библиотечная система(ЭБС)

Электронно-библиотечная система(ЭБС) Структура наборн элем

Структура наборн элем АЗЫ КОМПЬЮТЕРНОЙ ГРАМОТНОСТИ. Методический комплект 2 класс

АЗЫ КОМПЬЮТЕРНОЙ ГРАМОТНОСТИ. Методический комплект 2 класс Требования к решению инженерного кейса

Требования к решению инженерного кейса Безопасный Интернет

Безопасный Интернет Понятие «Информация» Информация — фундаментальная научная абстракция Информация — фундаментальная философская категория. И

Понятие «Информация» Информация — фундаментальная научная абстракция Информация — фундаментальная философская категория. И Анализ требований и определение спецификаций при объектном подходе

Анализ требований и определение спецификаций при объектном подходе Взаимосвязи в моделях

Взаимосвязи в моделях Объекты защиты и угрозы безопасности в автоматизированных системах

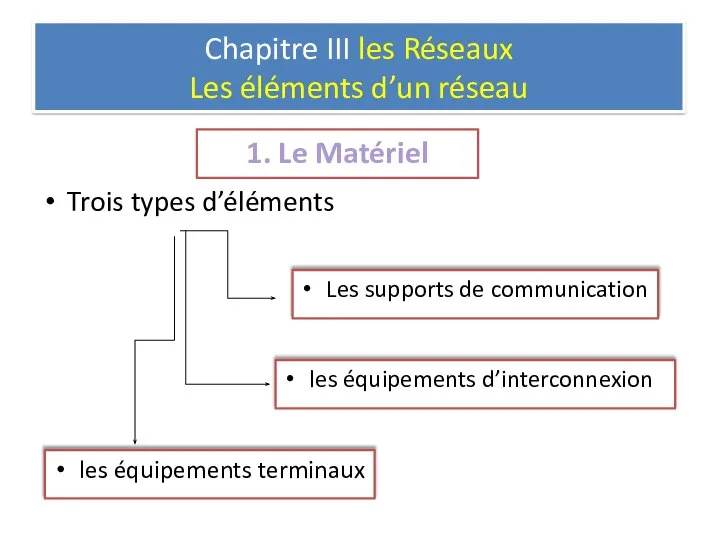

Объекты защиты и угрозы безопасности в автоматизированных системах Les Reseaux Suite

Les Reseaux Suite AR-тур по Калининграду

AR-тур по Калининграду Особенности средств разработки информационной системы

Особенности средств разработки информационной системы Критерии оценки Интернет–ресурсов Презентационный семинар

Критерии оценки Интернет–ресурсов Презентационный семинар Презентация Интернет

Презентация Интернет Инновационные стратегии

Инновационные стратегии Моделирование геометрических объектов в программе QCAD

Моделирование геометрических объектов в программе QCAD Исполнитель Робот

Исполнитель Робот База данных

База данных Презентация "Криптографические основы безопасности" - скачать презентации по Информатике

Презентация "Криптографические основы безопасности" - скачать презентации по Информатике Отношение входит в состав. Повторяем возможности графического редактора — инструмента создания графических

Отношение входит в состав. Повторяем возможности графического редактора — инструмента создания графических Электронные презентации PowerPoint

Электронные презентации PowerPoint Тема урока: «Язык разметки гипертекста HTML»

Тема урока: «Язык разметки гипертекста HTML» Регистрация в ИС Маркировка

Регистрация в ИС Маркировка Спам и защита от него

Спам и защита от него Игра Fortnite

Игра Fortnite История возникновения систем счисления

История возникновения систем счисления Современные SCADA-системы. Уровни управления

Современные SCADA-системы. Уровни управления