Содержание

- 2. ТРЕБОВАНИЯ К КОМПАКТНЫМ МОДЕЛЯМ 1. Общие требования 1.1. Возможность настройки модели на широкий спектр геометрических форм

- 3. ТРЕБОВАНИЯ К КОМПАКТНЫМ МОДЕЛЯМ 4. Требования к параметрам 4.1. Общее количество параметров должно быть минимальным. 4.2.

- 4. Модель уровней 1 - 3 Модель первого уровня (Level=1) основана на модели Шихмана-Ходжеса, которая представляет модифицированную

- 5. Полевой транзистор с управляющим p-n переходом Конструкция интегрального транзистора с управляющим p-n переходом Эквивалентная схема транзистора

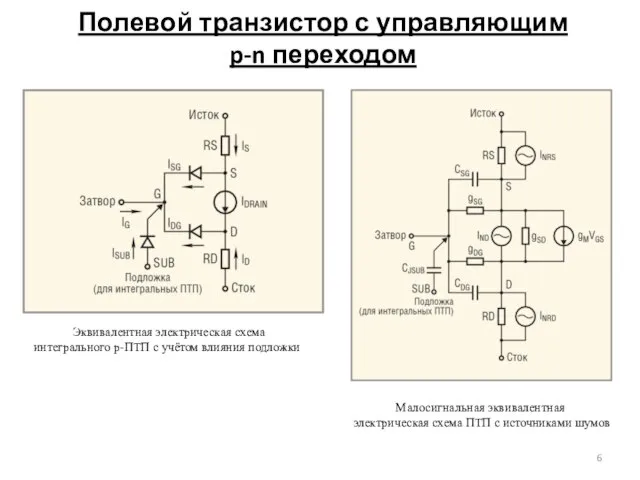

- 6. Полевой транзистор с управляющим p-n переходом Эквивалентная электрическая схема интегрального p-ПТП с учётом влияния подложки Малосигнальная

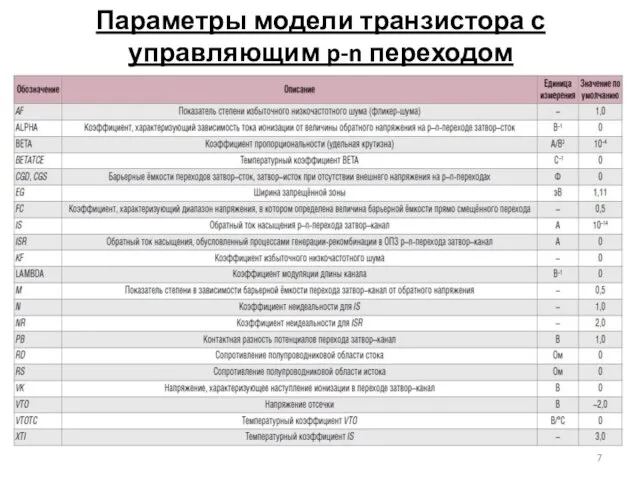

- 7. Параметры модели транзистора с управляющим p-n переходом

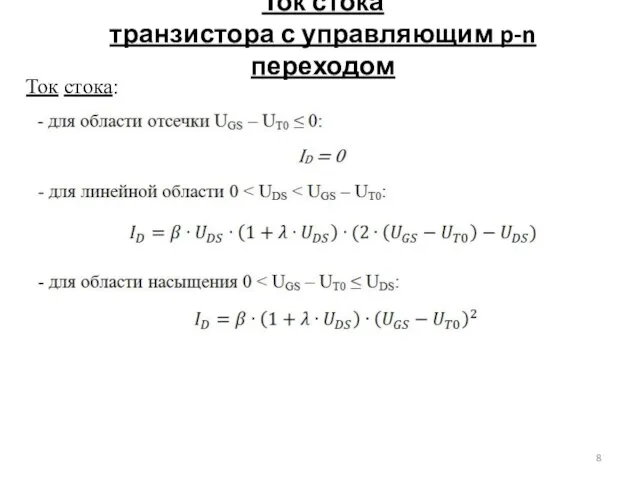

- 8. Ток стока транзистора с управляющим p-n переходом Ток стока:

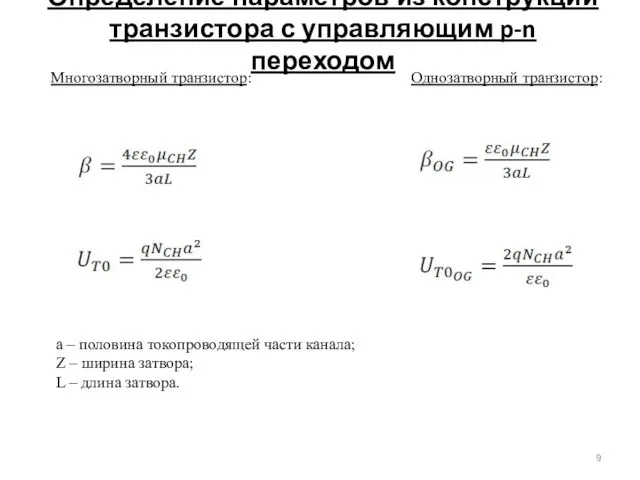

- 9. Определение параметров из конструкции транзистора с управляющим p-n переходом Однозатворный транзистор: Многозатворный транзистор: a – половина

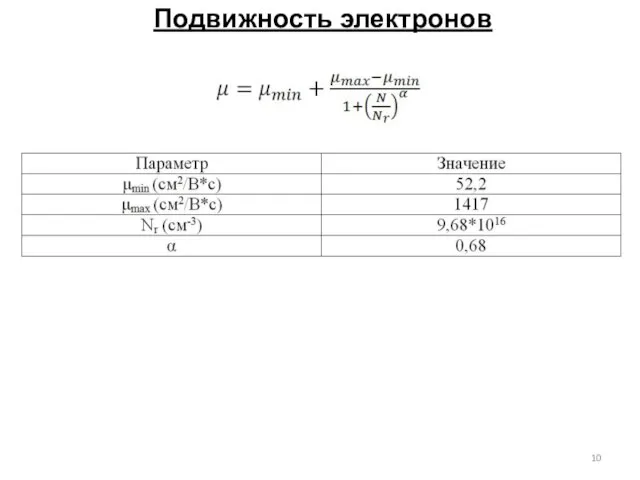

- 10. Подвижность электронов

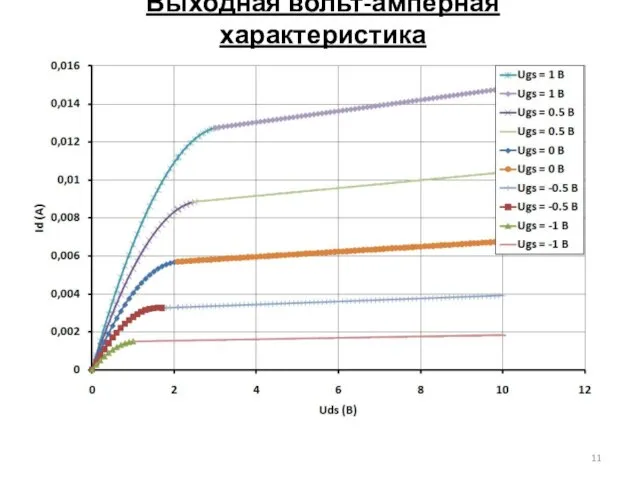

- 11. Выходная вольт-амперная характеристика

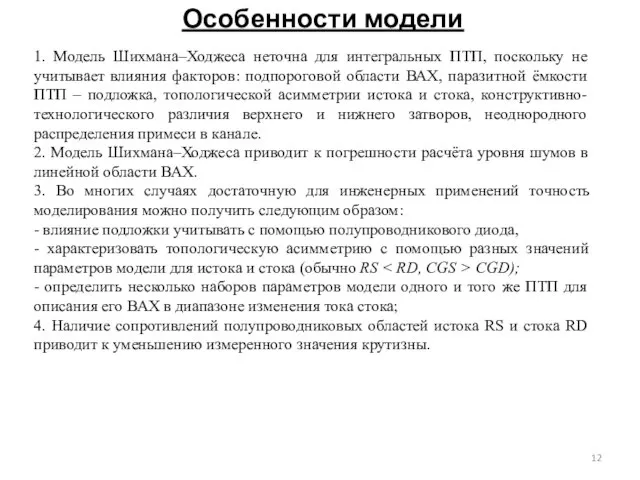

- 12. Особенности модели 1. Модель Шихмана–Ходжеса неточна для интегральных ПТП, поскольку не учитывает влияния факторов: подпороговой области

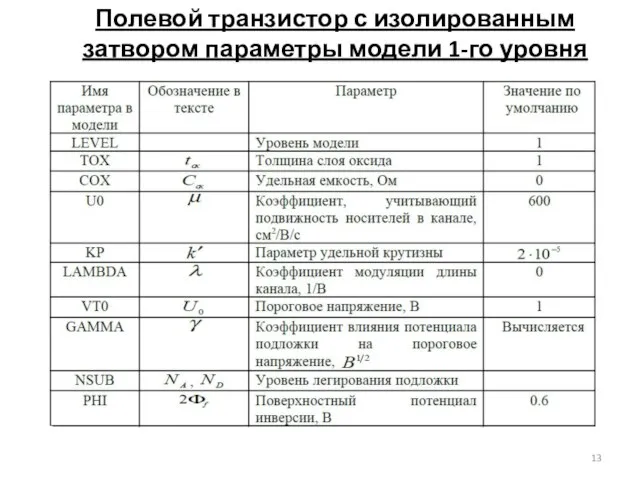

- 13. Полевой транзистор с изолированным затвором параметры модели 1-го уровня

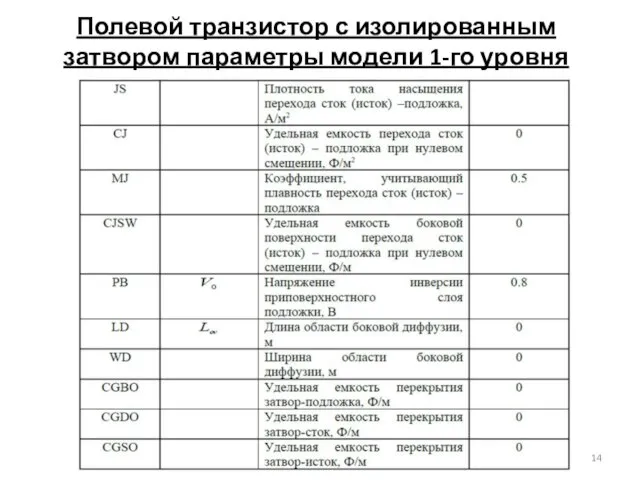

- 14. Полевой транзистор с изолированным затвором параметры модели 1-го уровня

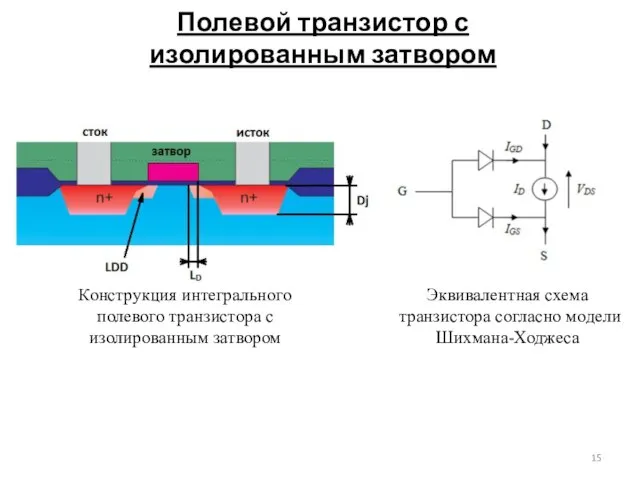

- 15. Полевой транзистор с изолированным затвором Конструкция интегрального полевого транзистора с изолированным затвором Эквивалентная схема транзистора согласно

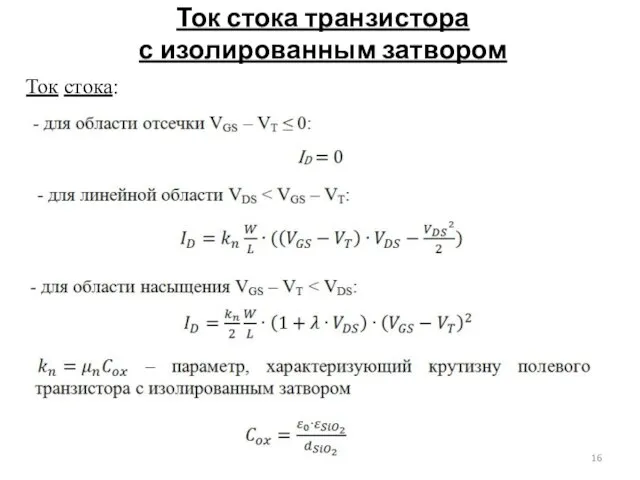

- 16. Ток стока транзистора с изолированным затвором Ток стока:

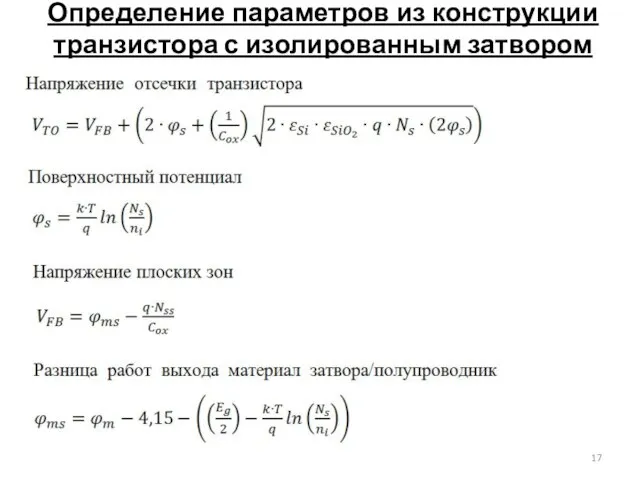

- 17. Определение параметров из конструкции транзистора с изолированным затвором

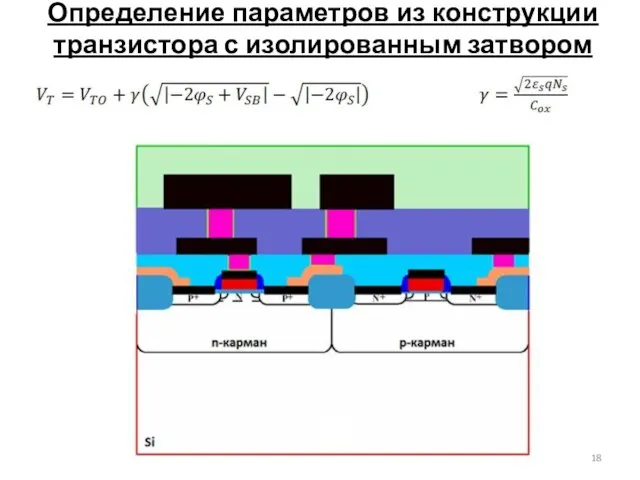

- 18. Определение параметров из конструкции транзистора с изолированным затвором

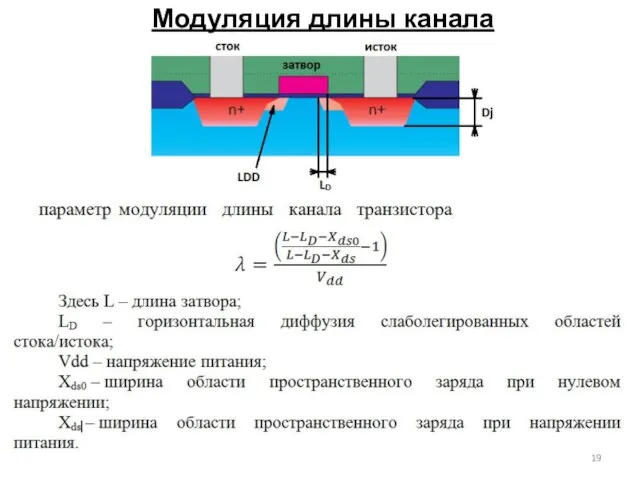

- 19. Модуляция длины канала

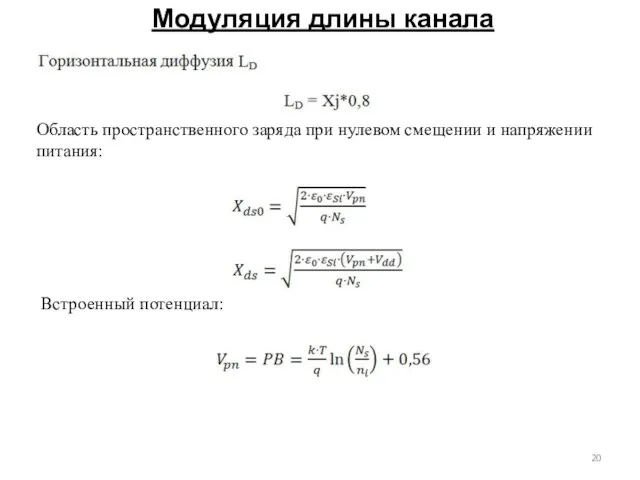

- 20. Модуляция длины канала Область пространственного заряда при нулевом смещении и напряжении питания: Встроенный потенциал:

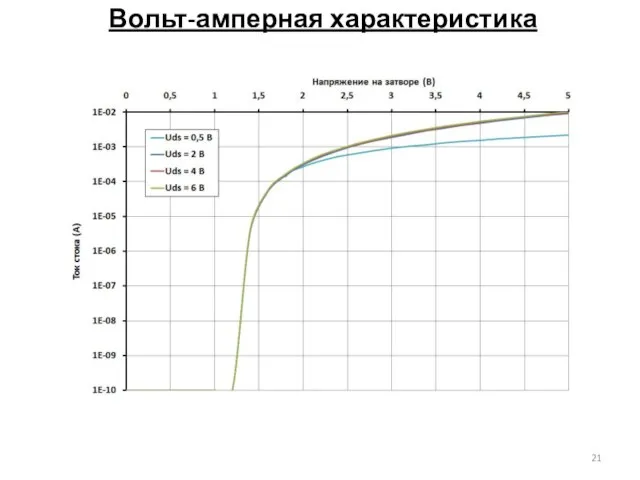

- 21. Вольт-амперная характеристика

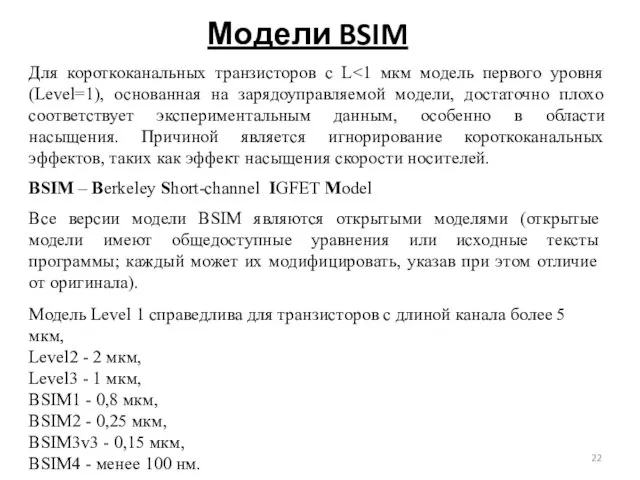

- 22. Модели BSIM BSIM – Berkeley Short-channel IGFET Model Все версии модели BSIM являются открытыми моделями (открытые

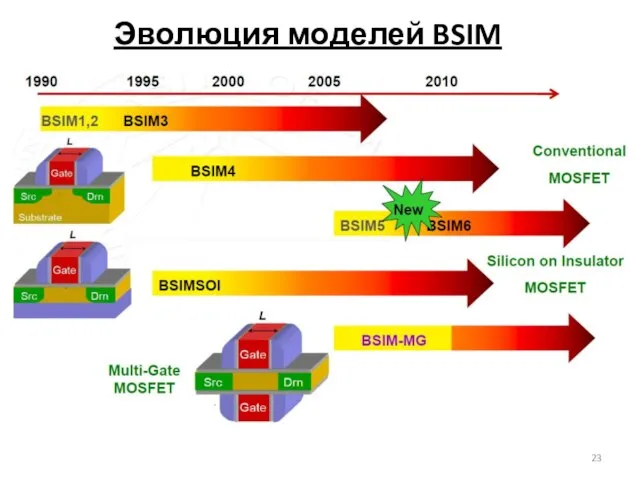

- 23. Эволюция моделей BSIM

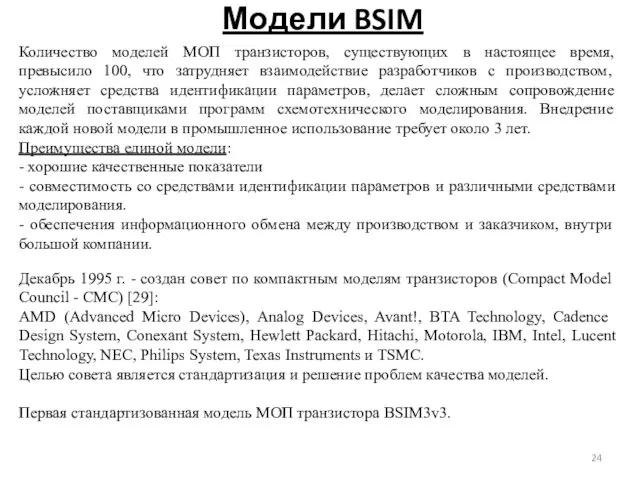

- 24. Модели BSIM Количество моделей МОП транзисторов, существующих в настоящее время, превысило 100, что затрудняет взаимодействие разработчиков

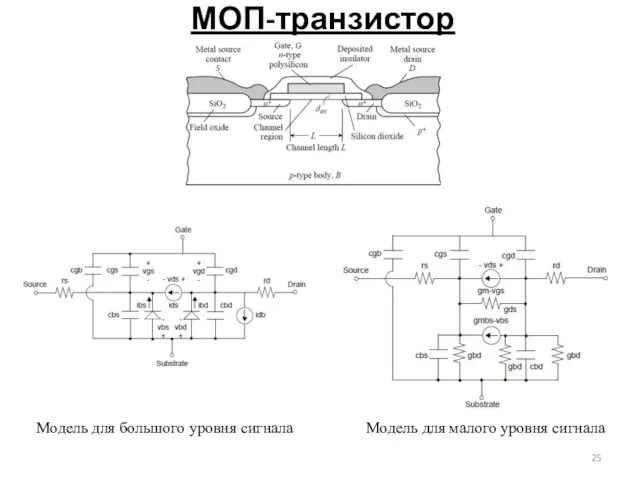

- 25. МОП-транзистор Модель для большого уровня сигнала Модель для малого уровня сигнала

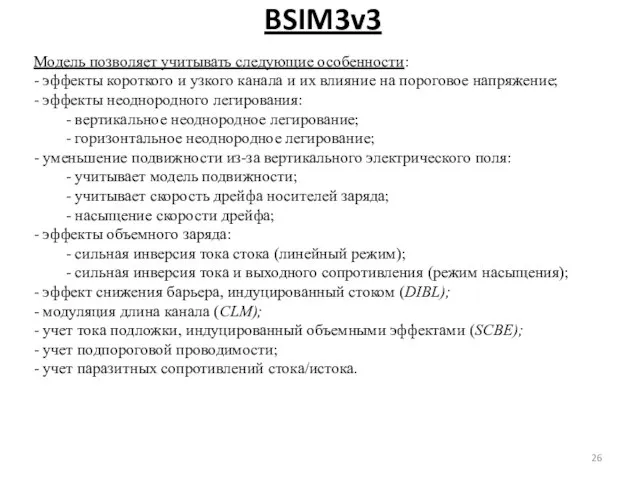

- 26. BSIM3v3 Модель позволяет учитывать следующие особенности: - эффекты короткого и узкого канала и их влияние на

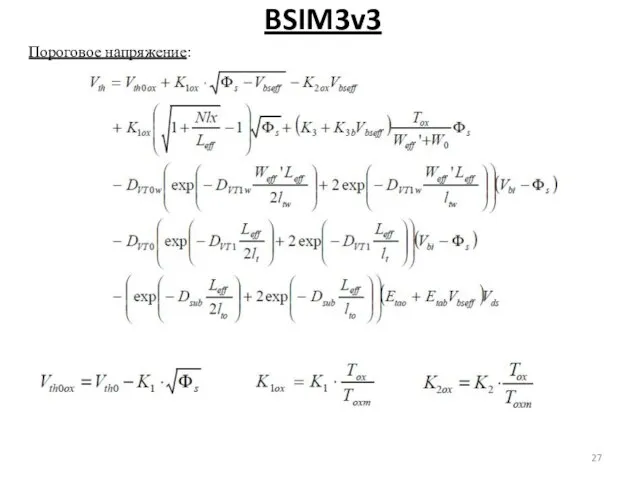

- 27. BSIM3v3 Пороговое напряжение:

- 28. BSIM3v3 Ток стока:

- 29. BSIM3v3 Особенности моделирования емкостей: - в модели емкостей используется отдельно эффективная длина и ширина канала; для

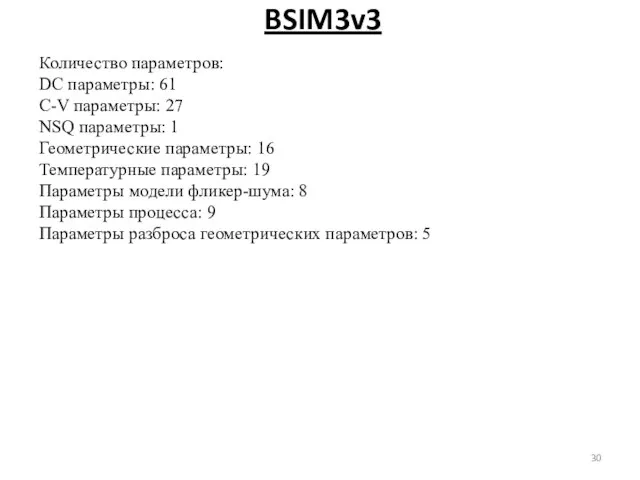

- 30. BSIM3v3 Количество параметров: DC параметры: 61 C-V параметры: 27 NSQ параметры: 1 Геометрические параметры: 16 Температурные

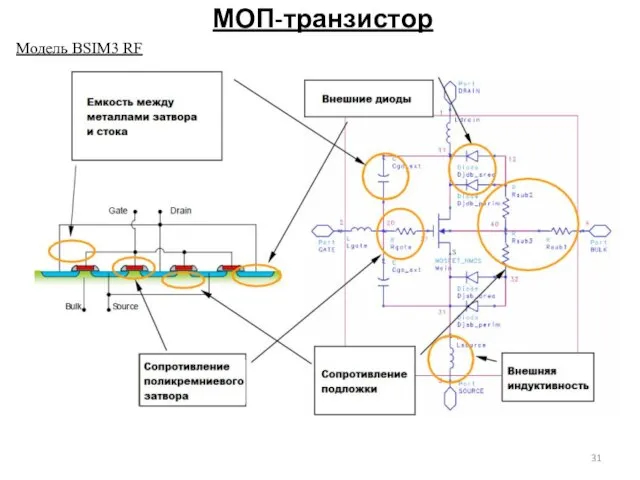

- 31. МОП-транзистор Модель BSIM3 RF

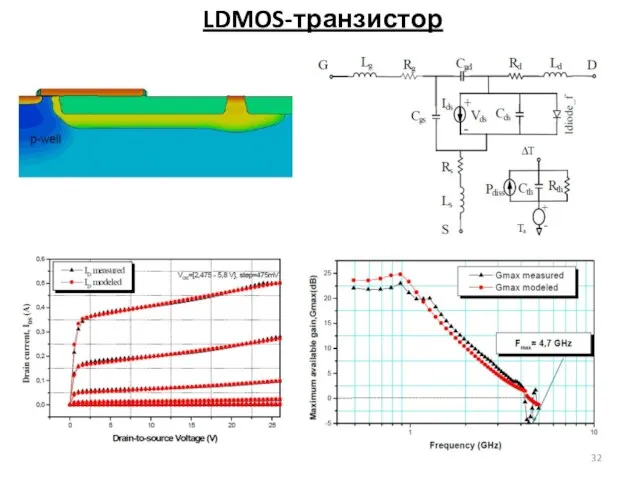

- 32. LDMOS-транзистор

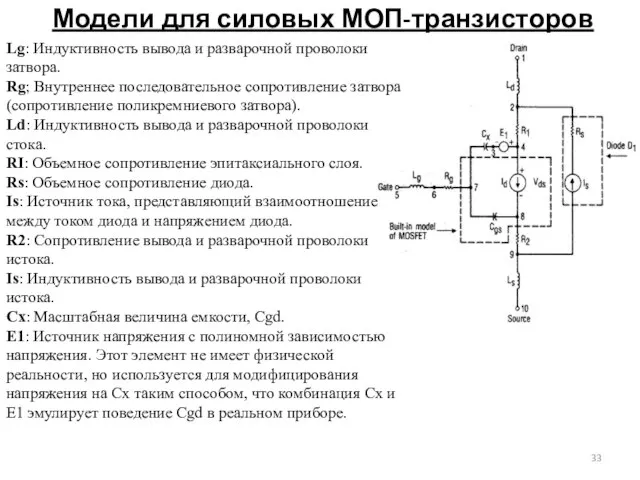

- 33. Модели для силовых МОП-транзисторов Lg: Индуктивность вывода и разварочной проволоки затвора. Rg; Внутреннее последовательное сопротивление затвора

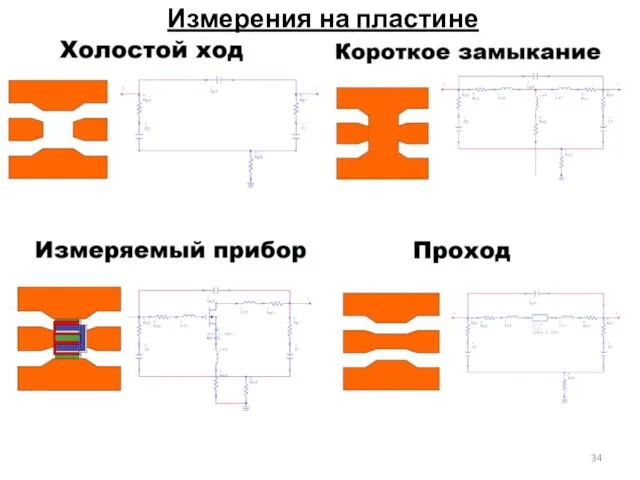

- 34. Измерения на пластине

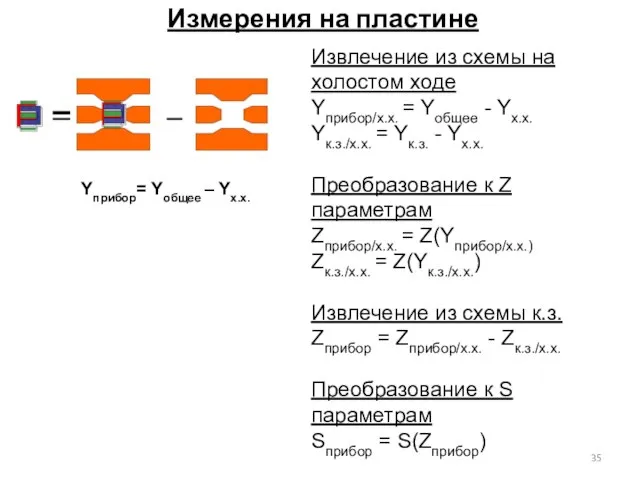

- 35. Измерения на пластине Yприбор= Yобщее – Yх.х. Извлечение из схемы на холостом ходе Yприбор/х.х. = Yобщее

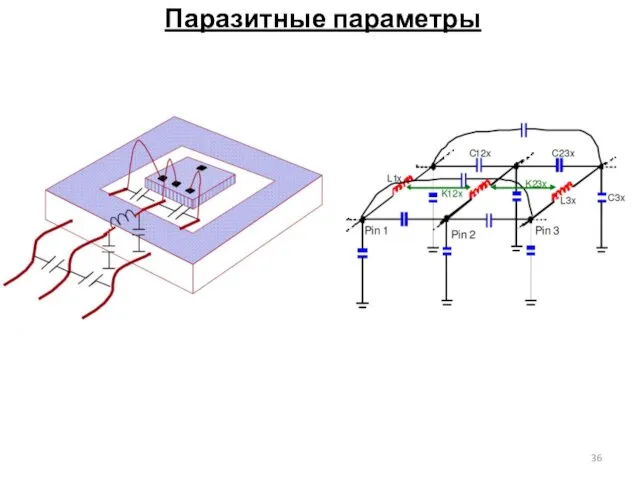

- 36. Паразитные параметры

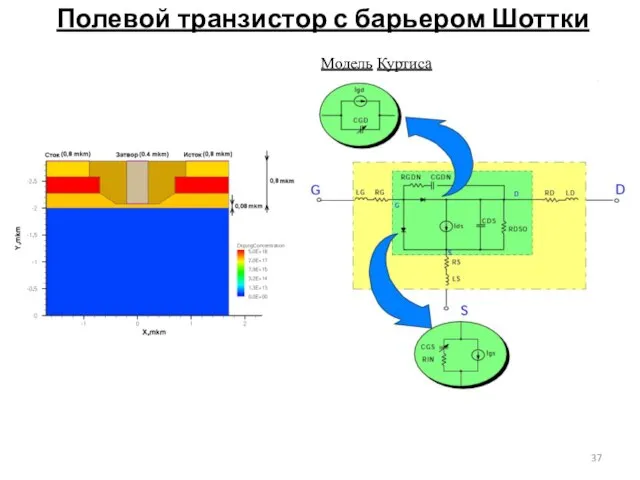

- 37. Полевой транзистор с барьером Шоттки Модель Куртиса

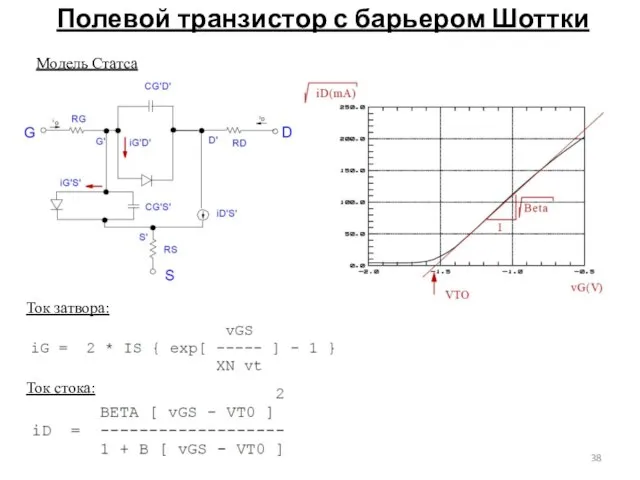

- 38. Полевой транзистор с барьером Шоттки Модель Статса Ток затвора: Ток стока:

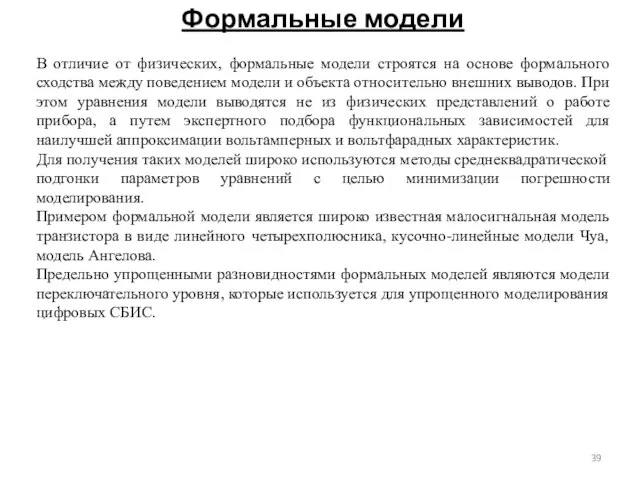

- 39. Формальные модели В отличие от физических, формальные модели строятся на основе формального сходства между поведением модели

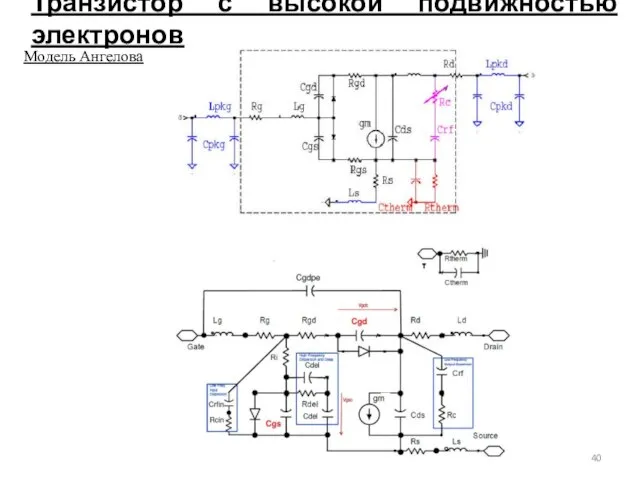

- 40. Модель Ангелова Транзистор с высокой подвижностью электронов

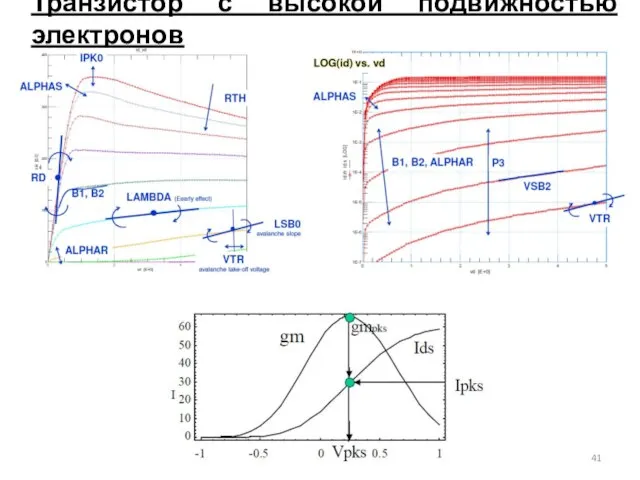

- 41. Транзистор с высокой подвижностью электронов

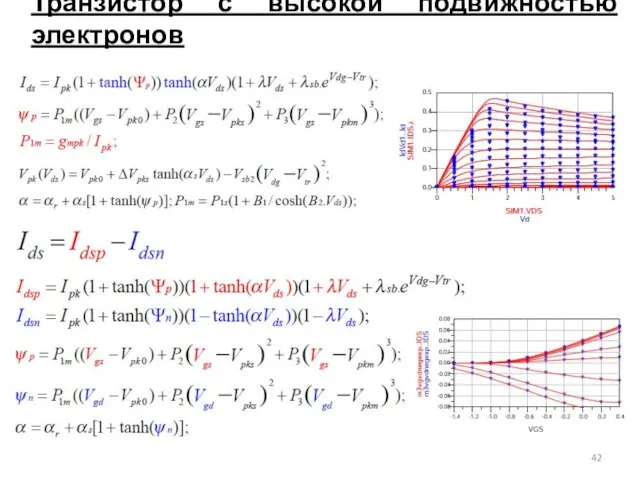

- 42. Транзистор с высокой подвижностью электронов

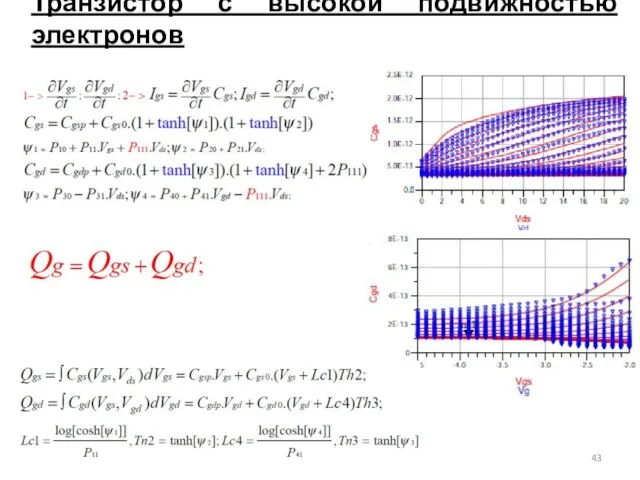

- 43. Транзистор с высокой подвижностью электронов

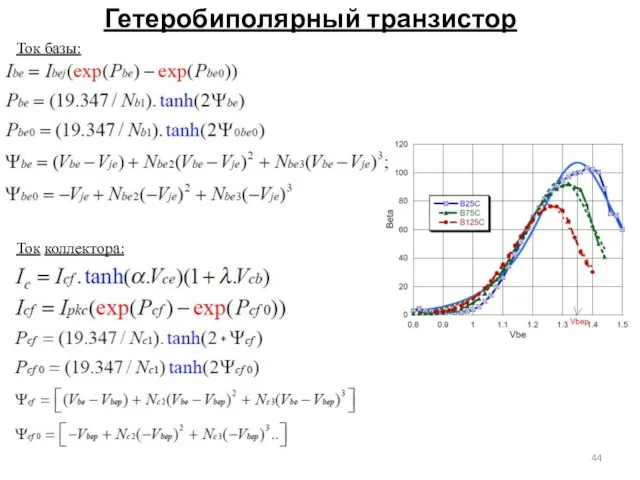

- 44. Гетеробиполярный транзистор Ток базы: Ток коллектора:

- 46. Скачать презентацию

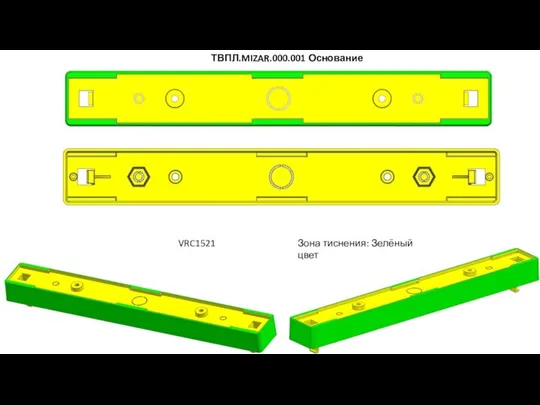

Зоны тиснения

Зоны тиснения Пейзаж родного края

Пейзаж родного края Образец клейма 2 (1)

Образец клейма 2 (1) 20161031_vologodskoe_maslodelanie

20161031_vologodskoe_maslodelanie za-hl-375-degrees-of-comparison-powerpoint_ver_2

za-hl-375-degrees-of-comparison-powerpoint_ver_2 Аддитивные технологии

Аддитивные технологии Железобетон в условиях высоких температур

Железобетон в условиях высоких температур Реконструкция прочностных свойств породы в процессе бурения

Реконструкция прочностных свойств породы в процессе бурения Отчет по производственной практике

Отчет по производственной практике Фото-кастинги. Summer program

Фото-кастинги. Summer program Организация предприятия по возделыванию люпина

Организация предприятия по возделыванию люпина Энергетическое обеспечение нашего дома

Энергетическое обеспечение нашего дома Термография в полиграфии

Термография в полиграфии 20141218_prezentatsiya_k_uroku

20141218_prezentatsiya_k_uroku Uczynki miłosierne względem ciała

Uczynki miłosierne względem ciała Заправка и обнуление картриджа Xerox WC 3119

Заправка и обнуление картриджа Xerox WC 3119 комикс

комикс 20150215_krupin_-_prezentatsiya_finalnaya_chast_2ya

20150215_krupin_-_prezentatsiya_finalnaya_chast_2ya Местоимение

Местоимение Кафедра специального (коррекционного) и инклюзивного образования

Кафедра специального (коррекционного) и инклюзивного образования Презентация август 2022

Презентация август 2022 Планирование, прогнозирование. Организация работ

Планирование, прогнозирование. Организация работ Санаторно-курортный центр ваш курорт

Санаторно-курортный центр ваш курорт Чарльз Дарвин

Чарльз Дарвин Современные методы повышения технических характеристик бетонов

Современные методы повышения технических характеристик бетонов Маршрут №20. Полюстрово

Маршрут №20. Полюстрово 20171114_5

20171114_5 Транспортно-планировочная организация города

Транспортно-планировочная организация города