Разработка схемной реализации цифрового устройства с временным разделением сигналов с входными параметрами

Содержание

- 2. Техническое задание Разработать схемную реализацию цифрового устройства с временным разделением сигналов с входными параметрами F1 =

- 3. Схемная реализация оптимальных логических функций

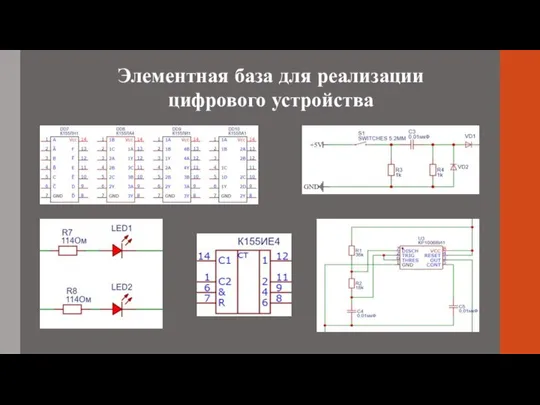

- 4. Элементная база для реализации цифрового устройства

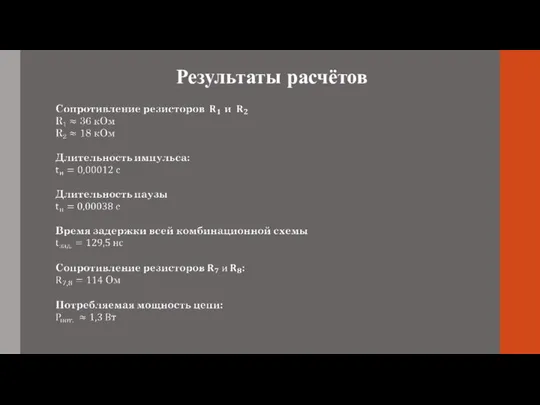

- 5. Результаты расчётов

- 6. Структурная электрическая схема цифрового устройства

- 7. Функциональная электрическая схема цифрового устройства

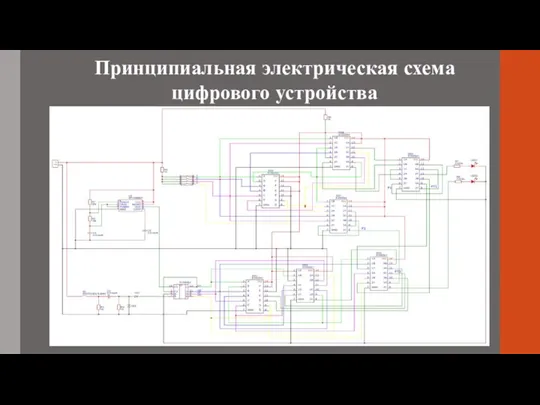

- 8. Принципиальная электрическая схема цифрового устройства

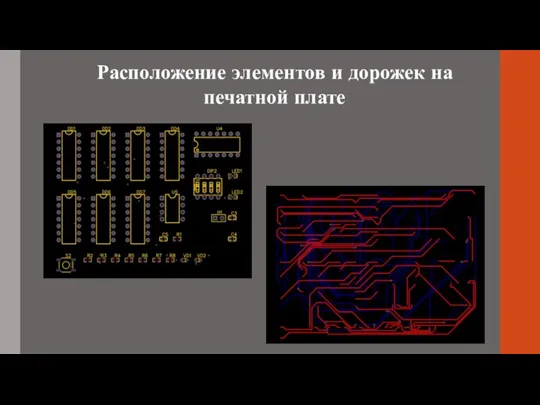

- 9. Расположение элементов и дорожек на печатной плате

- 11. Скачать презентацию

irregular2

irregular2 Susol RMU_Wiring 20220823

Susol RMU_Wiring 20220823 prezentatsiya1_na_otkrytyy_urok (1)

prezentatsiya1_na_otkrytyy_urok (1) 20220816_прототип лендинга_ лид магнит 10 воронок для бизнеса в онлайн

20220816_прототип лендинга_ лид магнит 10 воронок для бизнеса в онлайн азбука 27.01

азбука 27.01 Протестантский мир

Протестантский мир Дизайн-проект Горемыкинский парк

Дизайн-проект Горемыкинский парк Домики, которые построила природа

Домики, которые построила природа 20170627_proekt_gigiena

20170627_proekt_gigiena Рисование с детьми второй группы раннего возраста Колосок

Рисование с детьми второй группы раннего возраста Колосок Математика. Переместительное свойство умножения

Математика. Переместительное свойство умножения Кейсы

Кейсы Заручьем

Заручьем Парогазовые установки зарубежных производителей

Парогазовые установки зарубежных производителей 20150405_professii

20150405_professii МК Мокапы

МК Мокапы Оценка риска производственных объектов

Оценка риска производственных объектов Достижения системы образования

Достижения системы образования Системы сетевого и системного мониторинга

Системы сетевого и системного мониторинга Новые книги (орловские писатели для детей)

Новые книги (орловские писатели для детей) Разработка программного обеспечения автоматизированной информационной системы - Отдел кадров предприятия

Разработка программного обеспечения автоматизированной информационной системы - Отдел кадров предприятия Использование компетентностно – ориентированных заданий в преподавании биологии

Использование компетентностно – ориентированных заданий в преподавании биологии Субъекты государственной кадровой политики

Субъекты государственной кадровой политики берегите себя

берегите себя Отчет_SamAuto (1)

Отчет_SamAuto (1) Шиповые столярные соединения. Тест

Шиповые столярные соединения. Тест Турбаза в п.Култук Иркутской области

Турбаза в п.Култук Иркутской области Красота мира

Красота мира