Содержание

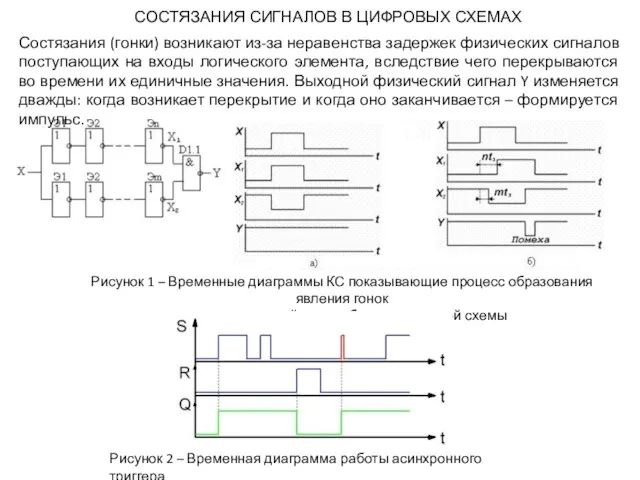

- 2. Состязания (гонки) возникают из-за неравенства задержек физических сигналов поступающих на входы логического элемента, вследствие чего перекрываются

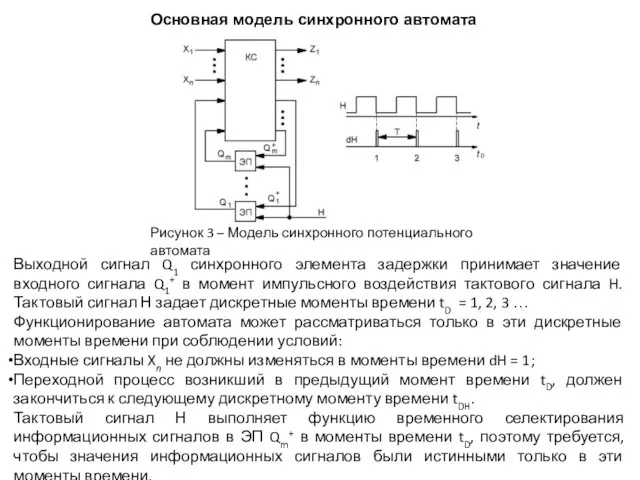

- 3. Рисунок 3 – Модель синхронного потенциального автомата Основная модель синхронного автомата Выходной сигнал Q1 синхронного элемента

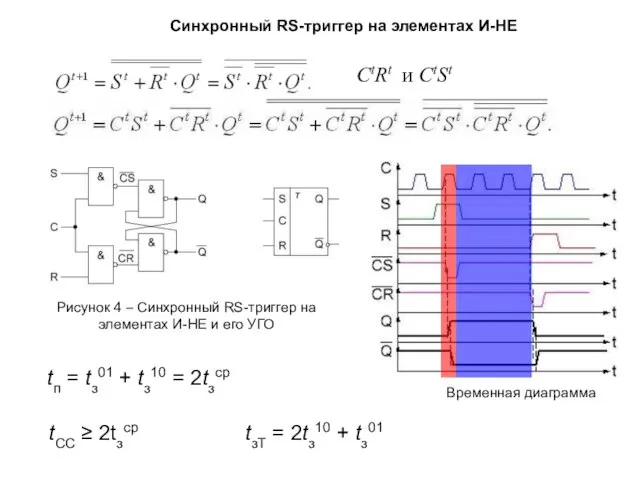

- 4. Синхронный RS-триггер на элементах И-НЕ Рисунок 4 – Синхронный RS-триггер на элементах И-НЕ и его УГО

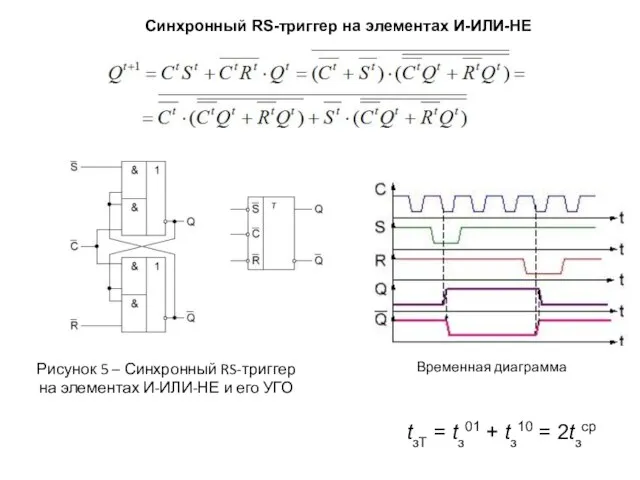

- 5. Рисунок 5 – Синхронный RS-триггер на элементах И-ИЛИ-НЕ и его УГО Временная диаграмма tзТ = tз01

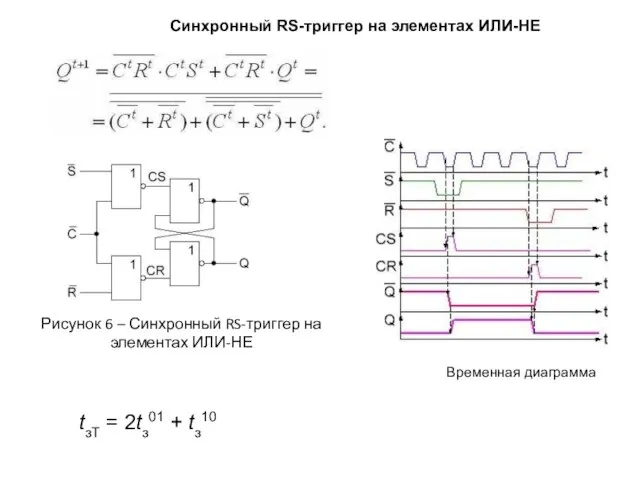

- 6. tзТ = 2tз01 + tз10 Синхронный RS-триггер на элементах ИЛИ-НЕ Рисунок 6 – Синхронный RS-триггер на

- 7. tп = tзТ = 2tзср Синхронный RS-триггер на элементах И-ИЛИ-НЕ Рисунок 7 – Синхронный RS-триггер на

- 8. Преобразование RS-триггера в D-триггер Рисунок 8 – Синхронный RS-триггер на элементах И-НЕ и его УГО

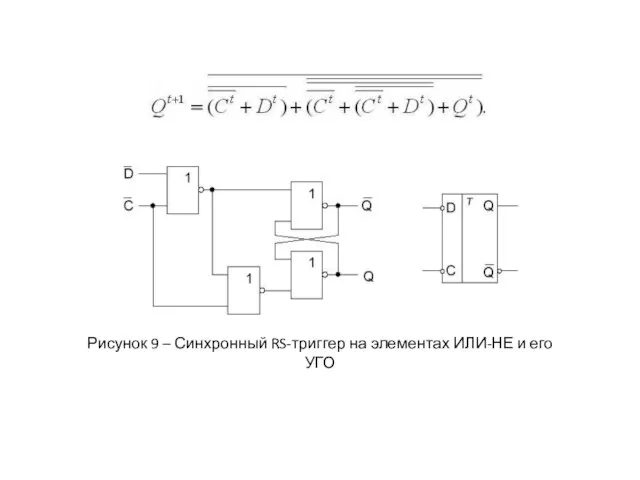

- 9. Рисунок 9 – Синхронный RS-триггер на элементах ИЛИ-НЕ и его УГО

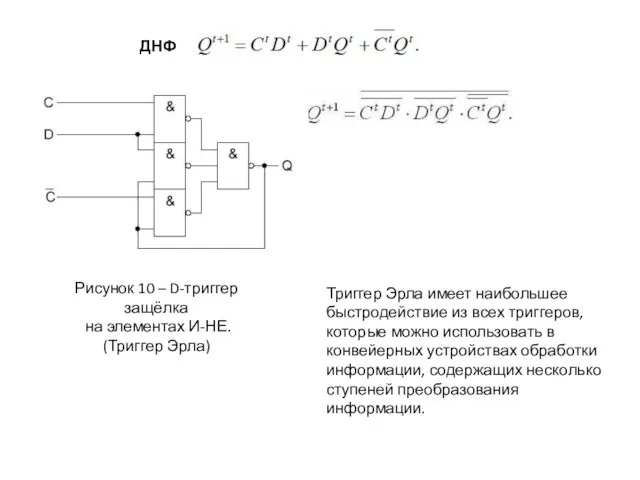

- 10. Рисунок 10 – D-триггер защёлка на элементах И-НЕ. (Триггер Эрла) ДНФ Триггер Эрла имеет наибольшее быстродействие

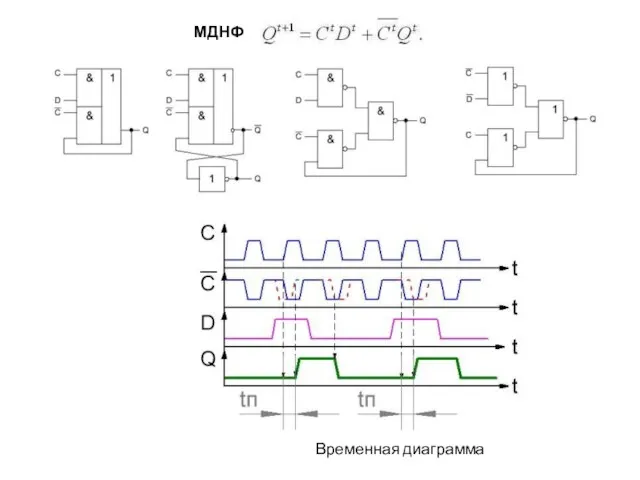

- 11. Временная диаграмма МДНФ

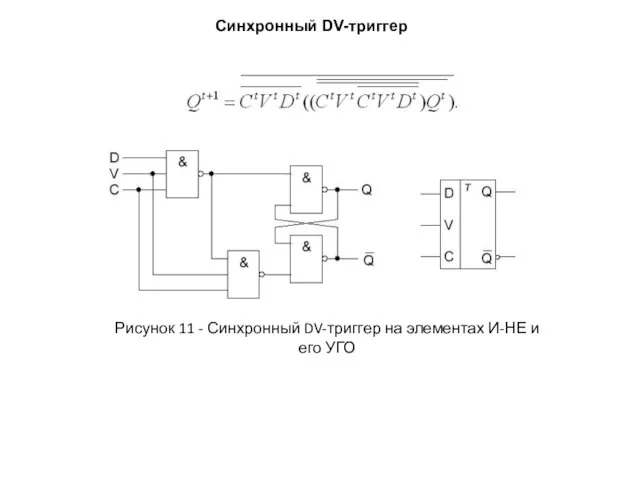

- 12. Рисунок 11 - Синхронный DV-триггер на элементах И-НЕ и его УГО Синхронный DV-триггер

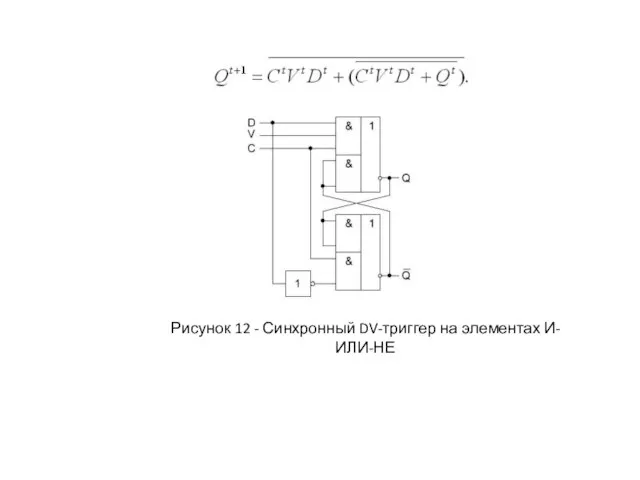

- 13. Рисунок 12 - Синхронный DV-триггер на элементах И-ИЛИ-НЕ

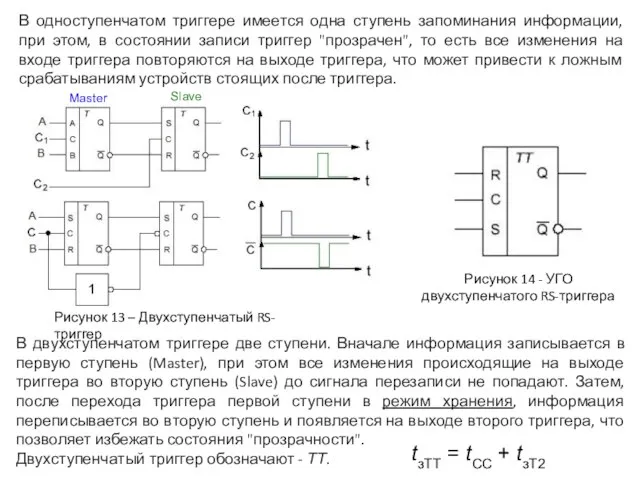

- 14. Рисунок 13 – Двухступенчатый RS-триггер Рисунок 14 - УГО двухступенчатого RS-триггера Master Slave В двухступенчатом триггере

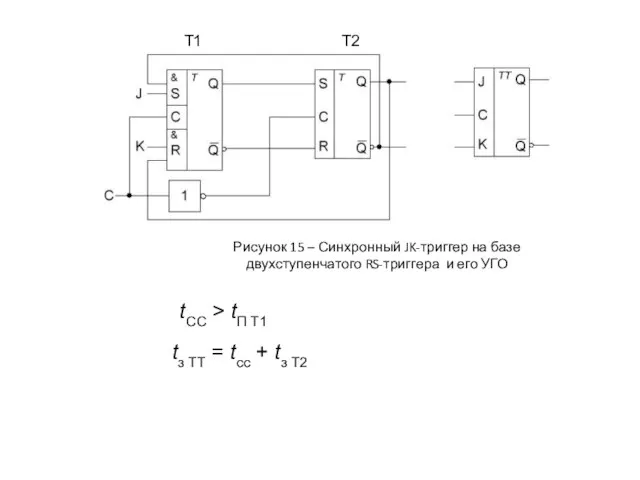

- 15. tз ТТ = tсс + tз Т2 T1 T2 tCC > tП Т1 Рисунок 15 –

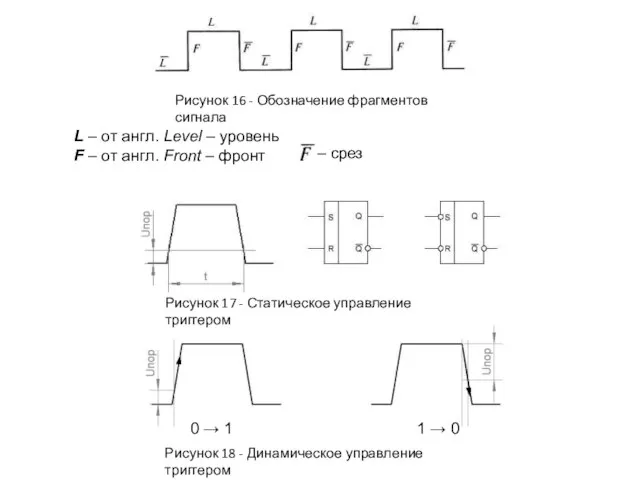

- 16. В ряду классификационных признаков способ управления записью информации в триггер следует считать важнейшим, так как он

- 17. Рисунок 17 - Статическое управление триггером Рисунок 18 - Динамическое управление триггером 0 → 1 1

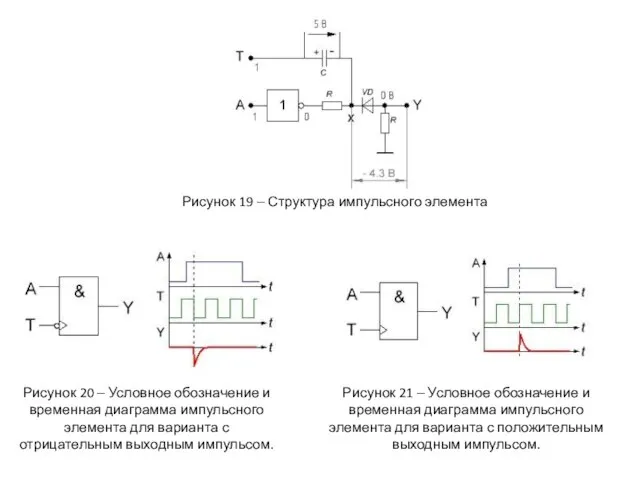

- 18. Рисунок 19 ‒ Структура импульсного элемента Рисунок 21 ‒ Условное обозначение и временная диаграмма импульсного элемента

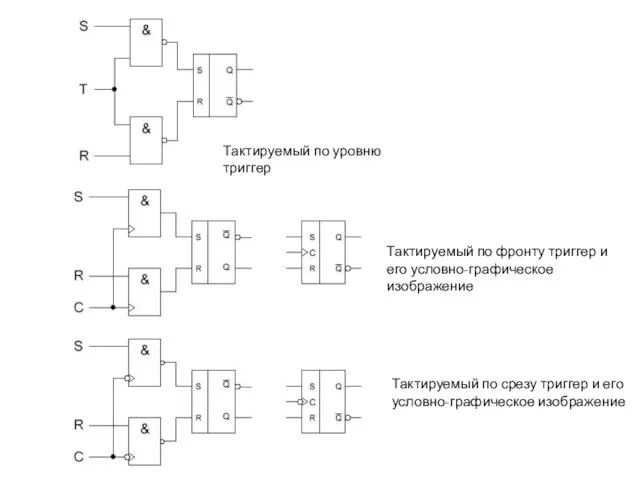

- 19. Тактируемый по уровню триггер Тактируемый по фронту триггер и его условно-графическое изображение Тактируемый по срезу триггер

- 20. Логическое отрицание Прямой динамический вход Инверсный динамический вход Асинхронные входы изображаются отдельно от синхронных и отделяются

- 22. Скачать презентацию

20140118_pervaya_duma

20140118_pervaya_duma Итоги международного форума Российская энергетическая неделя: энергия для глобального роста

Итоги международного форума Российская энергетическая неделя: энергия для глобального роста Воздушные холодильники и холодильники-конденсаторы

Воздушные холодильники и холодильники-конденсаторы Презентация к 41 параграфу

Презентация к 41 параграфу Система прерываний ЭВМ

Система прерываний ЭВМ Никель. История происхождения

Никель. История происхождения Местоположение РЦ Богородск

Местоположение РЦ Богородск Влияние лидерства на организационное управление

Влияние лидерства на организационное управление Russian dachas

Russian dachas Домашний ПК для учебы и игр.( Стоимость до 45 000 руб)

Домашний ПК для учебы и игр.( Стоимость до 45 000 руб) 20120125_pervaya_mirovaya_voyna_chast1

20120125_pervaya_mirovaya_voyna_chast1 Афганистан - живая память

Афганистан - живая память ПриложениеВ Все об Автом

ПриложениеВ Все об Автом Ассистивные технологии Assistive technology – AT

Ассистивные технологии Assistive technology – AT Презентация

Презентация راهنمای انتخاب فرایندهای تصفیه آب

راهنمای انتخاب فرایندهای تصفیه آب mustaqillik

mustaqillik Сооружения на газопроводах. Компенсаторы, конденсатосборники

Сооружения на газопроводах. Компенсаторы, конденсатосборники Мои домашние питомцы

Мои домашние питомцы Технология производства мягкого творога

Технология производства мягкого творога Трансформаторы. Электрические машины постоянного и переменного тока

Трансформаторы. Электрические машины постоянного и переменного тока Подъёмно-транспортное оборудование. Классификация и разновидности

Подъёмно-транспортное оборудование. Классификация и разновидности Религия древних египтян

Религия древних египтян

Рассуждение

Рассуждение 20171106_1_urok_literatura

20171106_1_urok_literatura Виды работы с пластилином. Рисуем мазками

Виды работы с пластилином. Рисуем мазками 20131127_matematicheskiy_turnir

20131127_matematicheskiy_turnir