Содержание

- 2. Дешифраторы Дешифратором называется комбинационная схема с несколькими входами и выходами, преобразующая код, подаваемый на входы, в

- 3. Дешифраторы Число входов и выходов в так называемом полном дешифраторе связано соотношением m=2n, где n —

- 4. Дешифраторы На выходах дешифратора вырабатываются значения булевых функций соответственно: F0=!Xn * !Xn-1*…………* !X3 * !X2 *!X1

- 5. Составление комбинационной схемы дешифратора

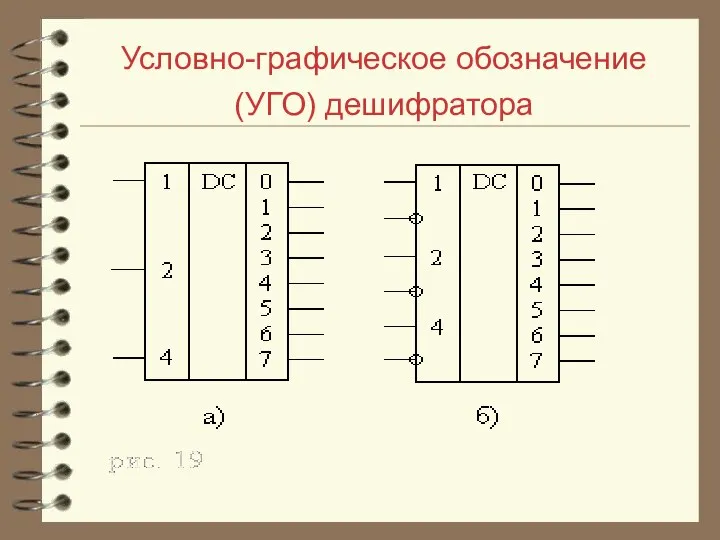

- 6. Условно-графическое обозначение (УГО) дешифратора

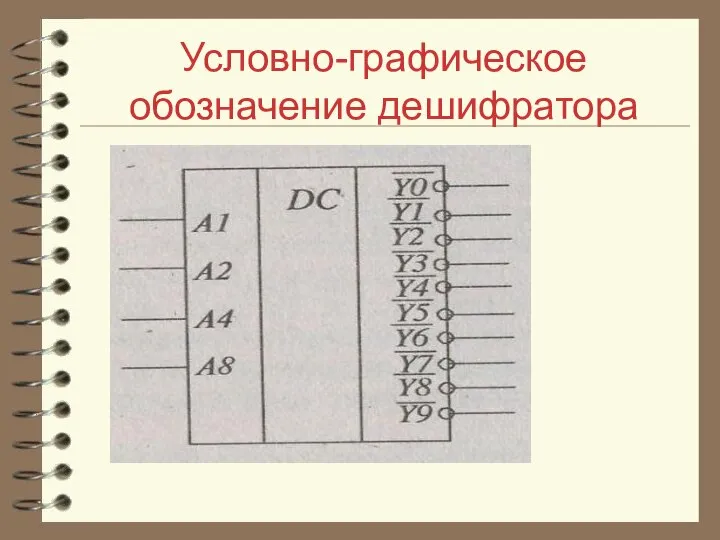

- 7. Условно-графическое обозначение дешифратора

- 8. Вход разрешения в схеме дешифратора В схеме дешифратора может быть организован дополнительный вход для сигнала разрешения

- 9. Каскадное включение дешифраторов Из логических элементов, являющихся дешифраторами, можно строить дешифраторы на большее число входов, при

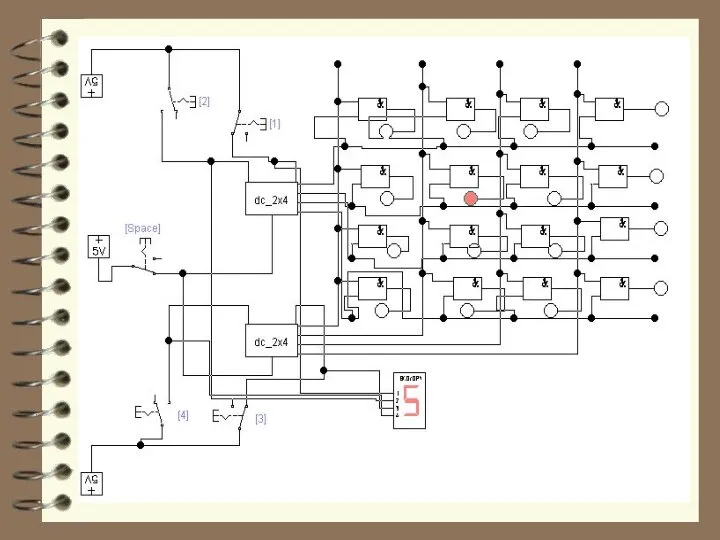

- 10. Матричная схема включения дешифраторов Другим способом реализации дешифратора на количество выходов, превышающее количество выходов в имеющихся

- 11. Матричная схема включения дешифраторов В матричной схеме используются два идентичных по размерности дешифратора, выходы одного образуют

- 12. Матричная схема включения дешифраторов В ячейках этой сетки матрицы устанавливаются логические элементы «И» или «И-НЕ», один

- 14. Шифраторы Шифратор — это комбинационное устройство, преобразующее унарный код (например десятичные числа) в двоичную систему счисления,

- 15. Шифраторы Шифратор иногда называют «кодером» (от англ. coder) и используют, например, для перевода десятичных чисел, набранных

- 16. Типы шифраторов Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на

- 17. Типы шифраторов Так, для преобразования кода кнопочного пульта в четырехразрядное двоичное число достаточно использовать лишь 10

- 18. Синтез схемы шифратора Рассмотрим пример построения шифратора для преобразования десятиразрядного единичного кода (десятичных чисел от 0

- 19. Таблица соответствия входов и выходов шифратора

- 20. Синтез схемы шифратора Используя данную таблицу соответствия, запишем логические выражения, включая в логическую сумму те входные

- 21. Схема шифратора 10х4

- 22. Мультиплексоры Мультиплексоры осуществляют подключение одного из входных каналов к единственному выходному каналу под управлением управляющего (адресующего)

- 23. Структура входов и выхода мультиплексора В цифровой технике мультиплексор имеет m информационных входов данных X1, Х2,

- 24. Передача входного сигнала на выход Двоичный код на входах адреса определяет номер того входа данных, с

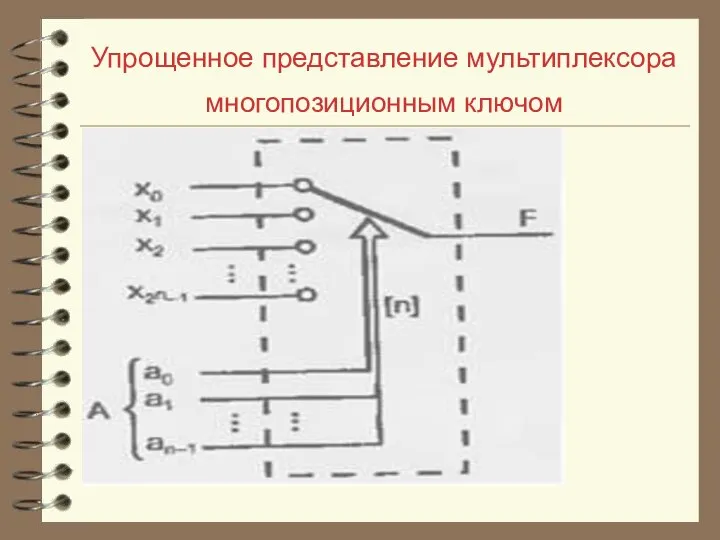

- 25. Упрощенное представление мультиплексора многопозиционным ключом

- 26. Таблица истинности мультиплексора

- 27. Выражение для сигнала на выходе мультиплексора Y=(E*!A1*!A0*X0)+ (E*!A1*A0*X1)+ (E*A1*!A0*X2)+(E*A1*A0*X3) При любом значении адресующего кода все слагаемые,

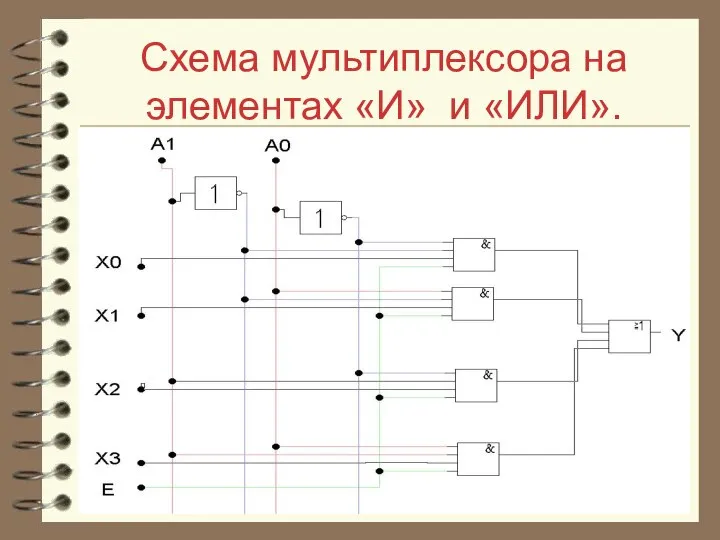

- 28. Схема мультиплексора на элементах «И» и «ИЛИ».

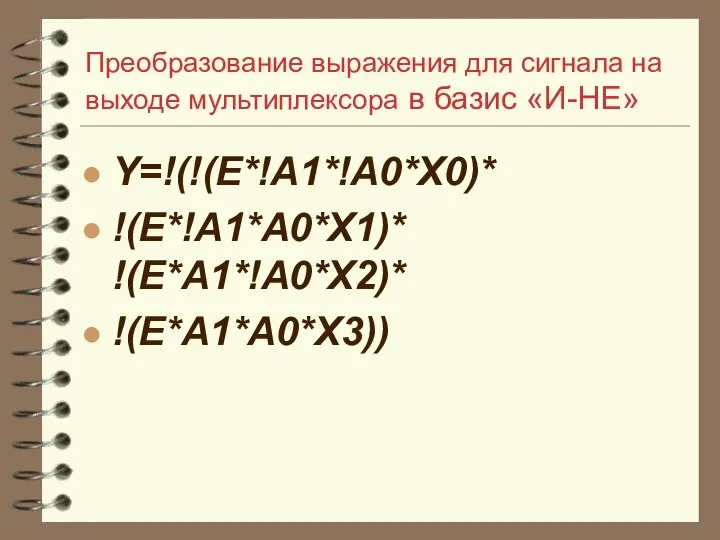

- 29. Преобразование выражения для сигнала на выходе мультиплексора в базис «И-НЕ» Y=!(!(E*!A1*!A0*X0)* !(E*!A1*A0*X1)* !(E*A1*!A0*X2)* !(E*A1*A0*X3))

- 30. Схема мультиплексора на элементах «И-НЕ»

- 31. Каскадное включение мультиплексоров При недостаточной размерности имеющихся микросхем мультиплексоров для решения задачи мультиплексирования большого числа входных

- 32. Каскадное включение мультиплексоров Пространство адресного кода делятся на две группы по имеющейся размерности микросхем мультиплексоров. По

- 33. Каскадное включение мультиплексоров Выходная ступень организуется мультиплексором с количеством информационных входов соответствующем количеству мультиплексоров, применённых во

- 34. Каскадное включение мультиплексоров На мультиплексор выходной ступени подаются разряды старшей адресной группы.

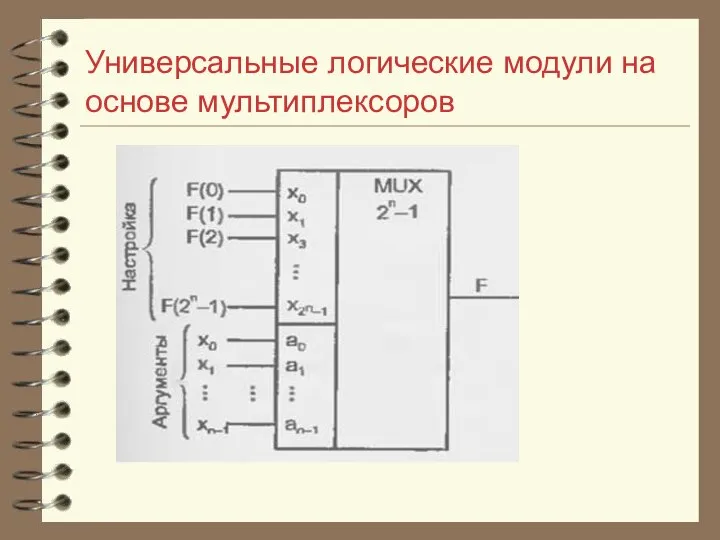

- 35. Универсальные логические модули на основе мультиплексоров Универсальные логические модули (УЛМ) на основе мультиплексоров относятся к устройствам,

- 36. Универсальные логические модули на основе мультиплексоров Известно, что общее число функций n аргументов выражается как 2n

- 37. Универсальные логические модули на основе мультиплексоров Первым способом настройки, используемым в УЛМ, является фиксация некоторых входов.

- 38. Универсальные логические модули на основе мультиплексоров Поясним на примере замены синтеза комбинационной схемы применением мультиплексора.

- 39. Табличное задание булевой функции

- 40. Универсальные логические модули на основе мультиплексоров На адресные входы мультиплексора подаются переменные булевой функции: Х0, X1,

- 41. Универсальные логические модули на основе мультиплексоров

- 42. Демультиплексоры Демультиплексорами называются устройства, которые позволяют подключать один информационный вход к нескольким выходам. Демультиплексор можно построить

- 43. Демультиплексоры Существенным отличием от мультиплексора является возможность объединения нескольких входов в один без дополнительных схем. Однако

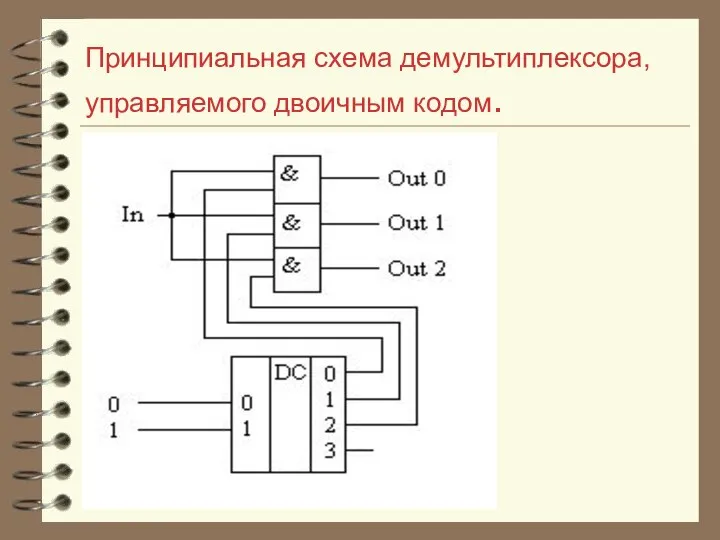

- 44. Принципиальная схема демультиплексора, управляемого двоичным кодом.

- 45. Идентичность демультиплексора с дешифратором с входом разрешения Однако, если рассмотреть принципиальную схему самого дешифратора, то можно

- 47. Скачать презентацию

Цифровые вычислительные устройства и микропроцессоры приборных комплексов. Микропроцессоры ARM

Цифровые вычислительные устройства и микропроцессоры приборных комплексов. Микропроцессоры ARM Цікаві факти про Китай

Цікаві факти про Китай Массопередача

Массопередача Субъекты информационного права Выполнила: Планкина Ирина Группа Ю-122б

Субъекты информационного права Выполнила: Планкина Ирина Группа Ю-122б  Методы монтажа конструкций зданий и сооружений

Методы монтажа конструкций зданий и сооружений Китай периода реформ конец 1970-х-1980-е годы

Китай периода реформ конец 1970-х-1980-е годы Презентация по алгебре Первообразная Правила нахождения первообразных

Презентация по алгебре Первообразная Правила нахождения первообразных  Зима. Фигурное катание. Ведущие мировые школы

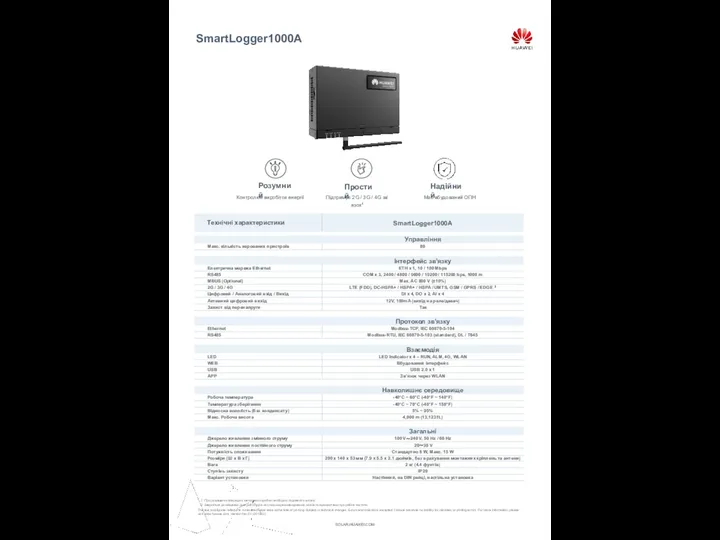

Зима. Фигурное катание. Ведущие мировые школы UA_SmartLogger1000A

UA_SmartLogger1000A Презентация "Земная жизнь Пресвятой Богородицы" - скачать презентации по МХК

Презентация "Земная жизнь Пресвятой Богородицы" - скачать презентации по МХК Герпетические инфекции

Герпетические инфекции Арабские завоевания и создание Арабского халифата

Арабские завоевания и создание Арабского халифата Сергей Анатольевич Маркин - участник войны в Афганистане

Сергей Анатольевич Маркин - участник войны в Афганистане Идеология бренда KITANO. Климатическа техника. Опыт работы компании «Евроклимат» с брендом KITANO

Идеология бренда KITANO. Климатическа техника. Опыт работы компании «Евроклимат» с брендом KITANO Есеп беру. Алматытелекомнын атқаратын қызметі. Транспорттық желінің сипаттамасы

Есеп беру. Алматытелекомнын атқаратын қызметі. Транспорттық желінің сипаттамасы Р.Р. Васнецов Богатыри

Р.Р. Васнецов Богатыри Уголовное законодательство России. История становления и развития

Уголовное законодательство России. История становления и развития Як дійсність перетворити в казку? Як дійсність перетворити в казку?

Як дійсність перетворити в казку? Як дійсність перетворити в казку? Нагрузки и воздействия

Нагрузки и воздействия Мова програмування Python

Мова програмування Python Моделирование режимов электрической сети в Mатlab

Моделирование режимов электрической сети в Mатlab Современные аспекты краниологии

Современные аспекты краниологии Страница Win32

Страница Win32 Сингапур в мировой экономике

Сингапур в мировой экономике Перпендикулярные плоскости

Перпендикулярные плоскости  Карьера и досуг. Может ли досуг стать карьерой

Карьера и досуг. Может ли досуг стать карьерой Тема уроку. Правопорушення

Тема уроку. Правопорушення Школьная форма

Школьная форма