Содержание

- 2. Интегральная микросхема, чип, микрочип — микроэлектронное устройство — электронная схема произвольной сложности, изготовленная на полупроводниковом кристалле

- 3. Степень интеграции малая интегральная схема (МИС) — до 100 элементов в кристалле, средняя интегральная схема (СИС)

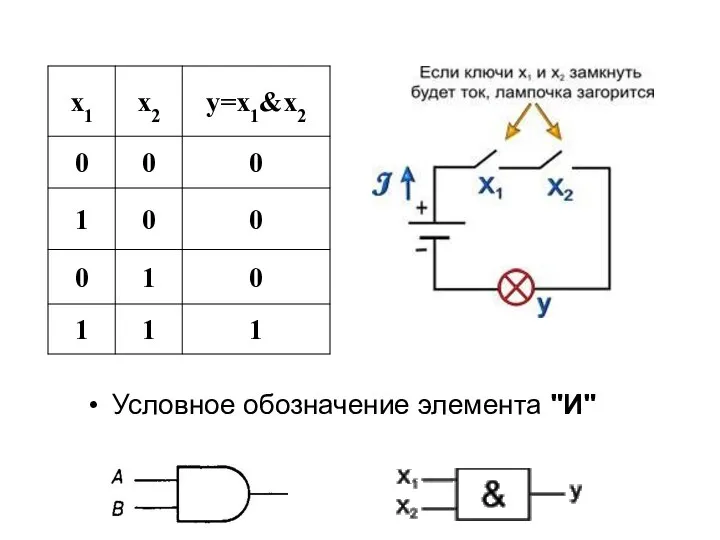

- 4. Базовые логические элементы Схема И Схема реализует конъюнкцию (логическое умножение) двух или более логических значений Единица

- 5. Условное обозначение элемента "И"

- 6. Схема ИЛИ Схема ИЛИ реализует дизъюнкцию (логическое сложение) двух или более логических значений Когда хотя бы

- 7. Условное обозначение элемента "ИЛИ"

- 8. Схема НЕ. Схема НЕ (инвертор) реализует операцию отрицание двух или более логических значений. Условное обозначение элемента

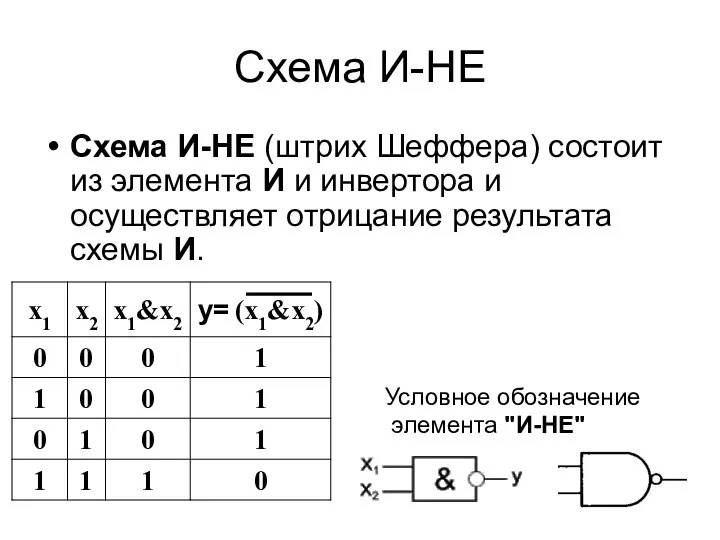

- 9. Схема И-НЕ Схема И-НЕ (штрих Шеффера) состоит из элемента И и инвертора и осуществляет отрицание результата

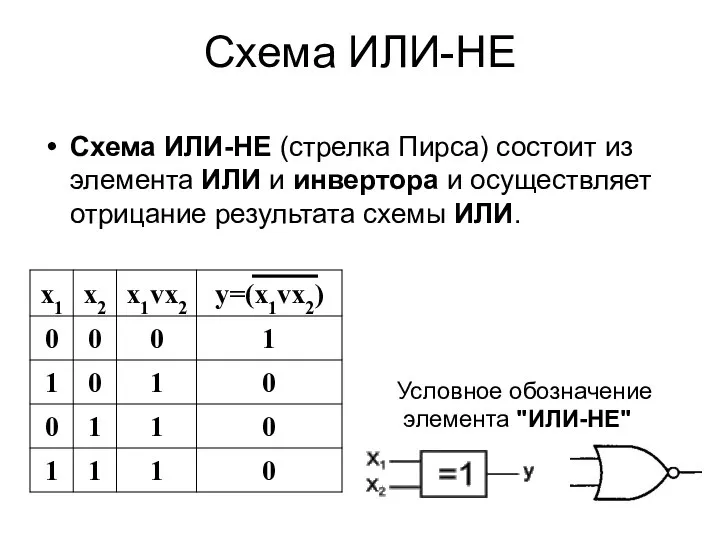

- 10. Схема ИЛИ-НЕ Схема ИЛИ-НЕ (стрелка Пирса) состоит из элемента ИЛИ и инвертора и осуществляет отрицание результата

- 11. Триггер Триггер - электронное устройство, которое может находиться в двух устойчивых состояниях, поэтому они применяются в

- 12. RS-триггер асинхронный RS-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё

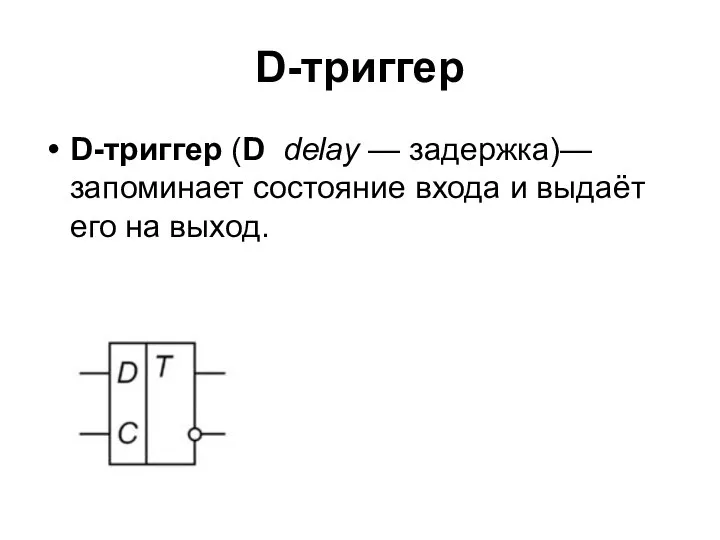

- 13. D-триггер D-триггер (D delay — задержка)— запоминает состояние входа и выдаёт его на выход.

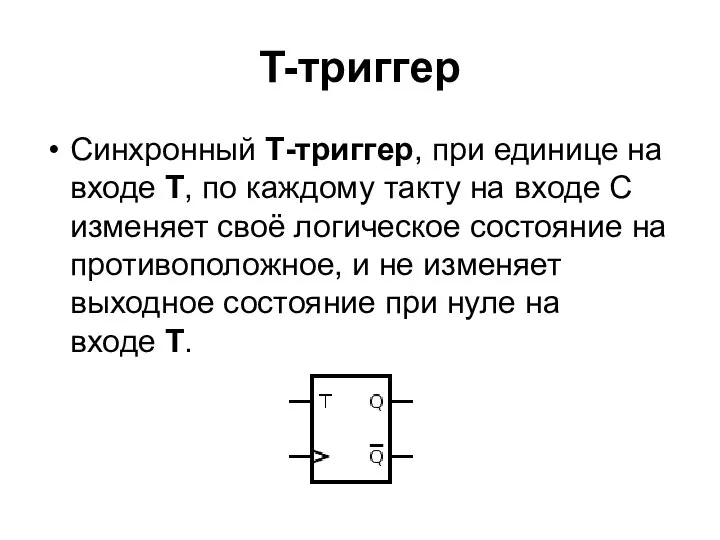

- 14. T-триггер Синхронный Т-триггер, при единице на входе Т, по каждому такту на входе С изменяет своё

- 16. Скачать презентацию

Обзор языка SQL.ppt

Обзор языка SQL.ppt Сведения о бетоне

Сведения о бетоне Оценка качества зданий. Показатели качества зданий. Обследование зданий

Оценка качества зданий. Показатели качества зданий. Обследование зданий Конституционное право

Конституционное право РАДИОТЕХНИЧЕСКИЕ ЦЕПИ И СИГНАЛЫ 16

РАДИОТЕХНИЧЕСКИЕ ЦЕПИ И СИГНАЛЫ 16 Гидравлический привод

Гидравлический привод Электронная торговля

Электронная торговля Критерии проведения обязательного аудита

Критерии проведения обязательного аудита Политическое сознание

Политическое сознание Решение задач с использованием оператора циклов

Решение задач с использованием оператора циклов Биржевая торговля – это прошлое или будущее человечества? Биржа в классическом понимании это: 1) место, где регулярно в одно и тож

Биржевая торговля – это прошлое или будущее человечества? Биржа в классическом понимании это: 1) место, где регулярно в одно и тож Методология исследований управления

Методология исследований управления Чековая лента

Чековая лента БЖД

БЖД Организация помощи при автодорожной травме

Организация помощи при автодорожной травме Греческий ордер

Греческий ордер Изготовление промера

Изготовление промера Информационное общество. WAN

Информационное общество. WAN Геополитическое пространство Южной Азии

Геополитическое пространство Южной Азии Глобальная спутниковая навигационная система GPS

Глобальная спутниковая навигационная система GPS Средние века и Возрождение

Средние века и Возрождение  Сторонник понятия экономического либерализма, который не допускает вмешательства правительства в экономике и принимающий свобод

Сторонник понятия экономического либерализма, который не допускает вмешательства правительства в экономике и принимающий свобод Жан Огюст Доминик Энгр - французский живописец

Жан Огюст Доминик Энгр - французский живописец Административное право

Административное право Политические партии

Политические партии Объекты и классы в PHP

Объекты и классы в PHP Становление и развитие политической науки

Становление и развитие политической науки Общие сведения. Назначение и применение JavaScript

Общие сведения. Назначение и применение JavaScript