Содержание

- 2. Лекция 3. Комбинационные асинхронные устройства Комбинационные схемы: Выходы комбинационных схем зависят только от текущих значений на

- 3. Лекция 3. Комбинационные асинхронные устройства Схема является комбинационной, если она состоит из соединенных между собой элементов

- 4. Лекция 3. Комбинационные асинхронные устройства Схема является комбинационной, если она состоит из соединенных между собой элементов

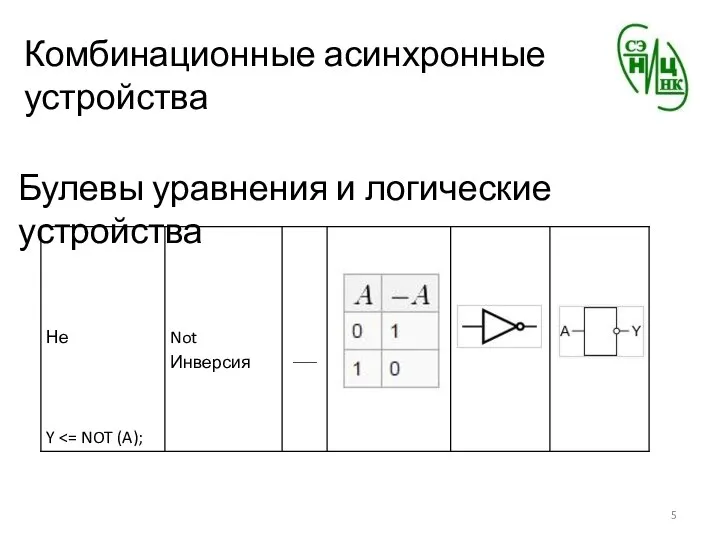

- 5. Комбинационные асинхронные устройства Булевы уравнения и логические устройства

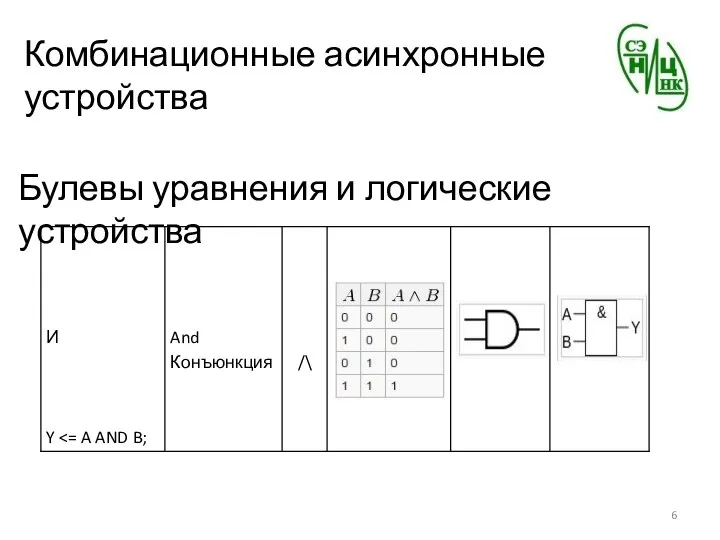

- 6. Комбинационные асинхронные устройства Булевы уравнения и логические устройства

- 7. Комбинационные асинхронные устройства Булевы уравнения и логические устройства

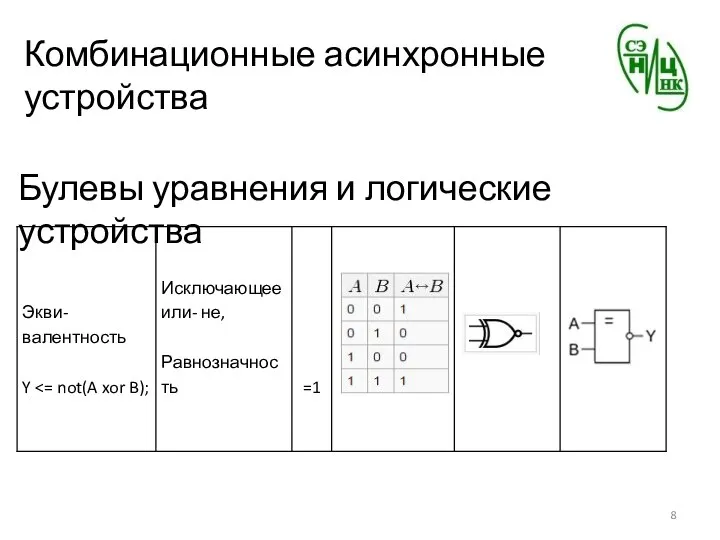

- 8. Комбинационные асинхронные устройства Булевы уравнения и логические устройства

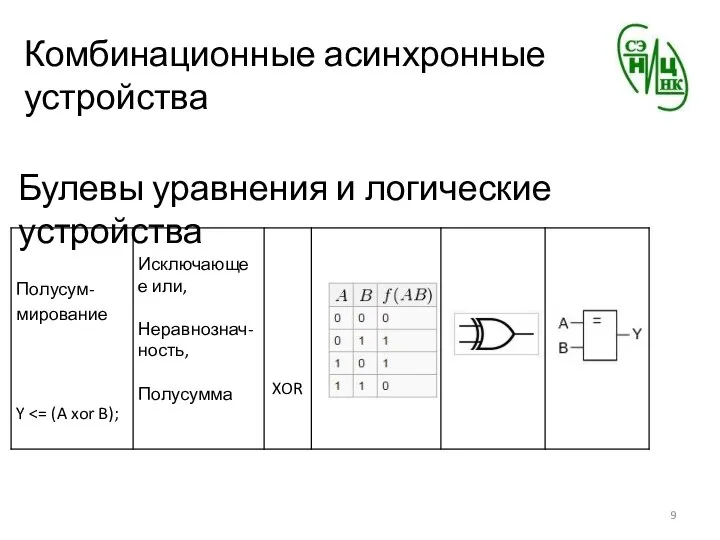

- 9. Комбинационные асинхронные устройства Булевы уравнения и логические устройства

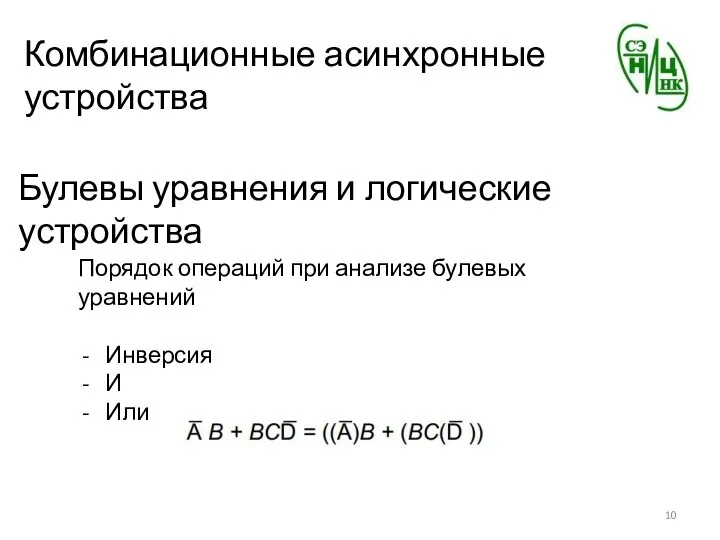

- 10. Комбинационные асинхронные устройства Булевы уравнения и логические устройства Порядок операций при анализе булевых уравнений Инверсия И

- 11. Комбинационные асинхронные устройства Булевы уравнения и логические устройства Минтерм и Макстерм Минтерм (minterm, элементарная конъюнктивная форма)

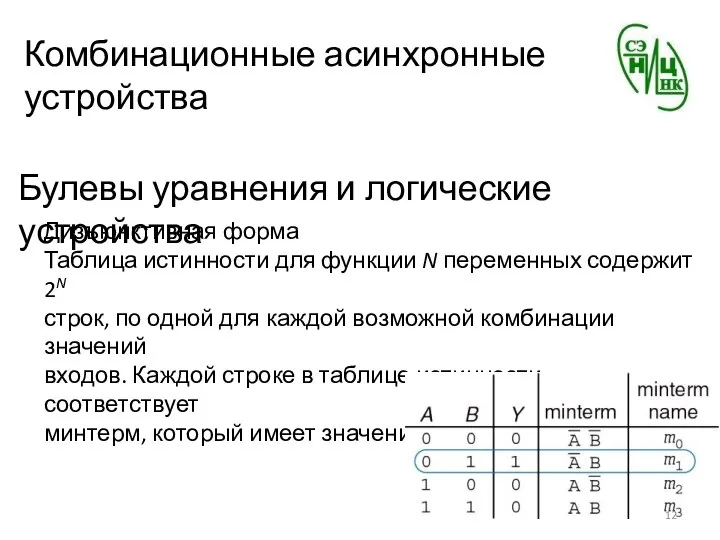

- 12. Комбинационные асинхронные устройства Булевы уравнения и логические устройства Дизъюнктивная форма Таблица истинности для функции N переменных

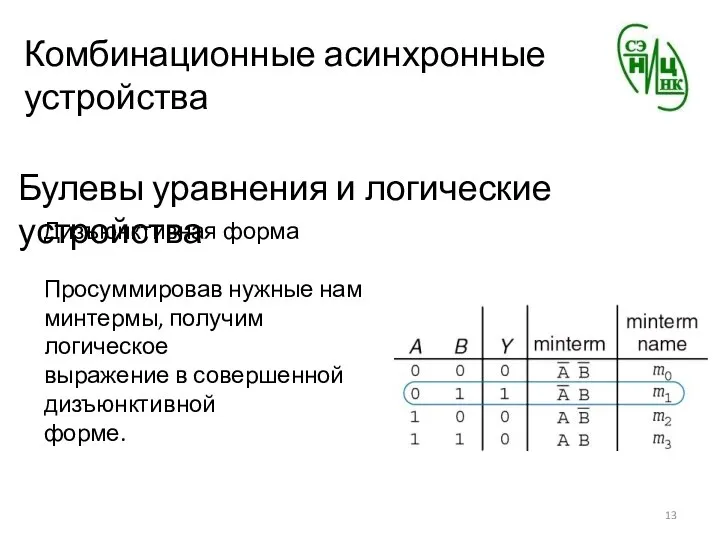

- 13. Комбинационные асинхронные устройства Булевы уравнения и логические устройства Дизъюнктивная форма Просуммировав нужные нам минтермы, получим логическое

- 14. Комбинационные асинхронные устройства Булевы уравнения и логические устройства Конъюктивная форма Таблица истинности для функции N переменных

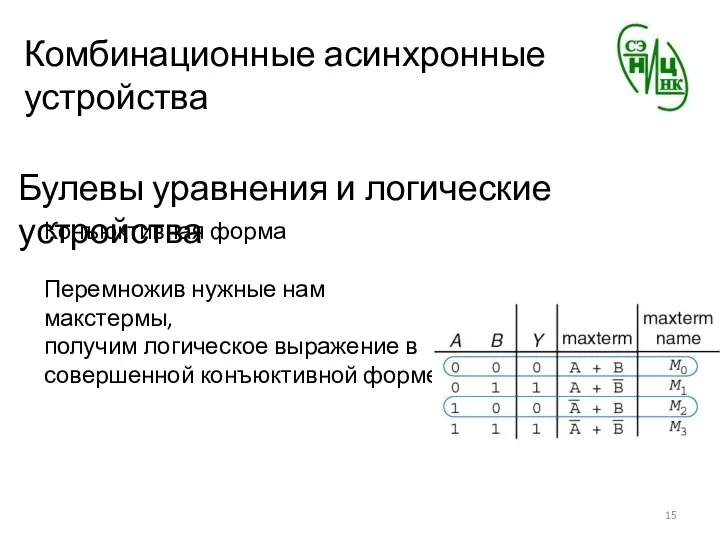

- 15. Комбинационные асинхронные устройства Булевы уравнения и логические устройства Конъюктивная форма Перемножив нужные нам макстермы, получим логическое

- 16. Комбинационные асинхронные устройства Булевы уравнения и логические устройства Конъюктивная и дизъюнктивная формы Задача: написать совершенную дизъюнктивную

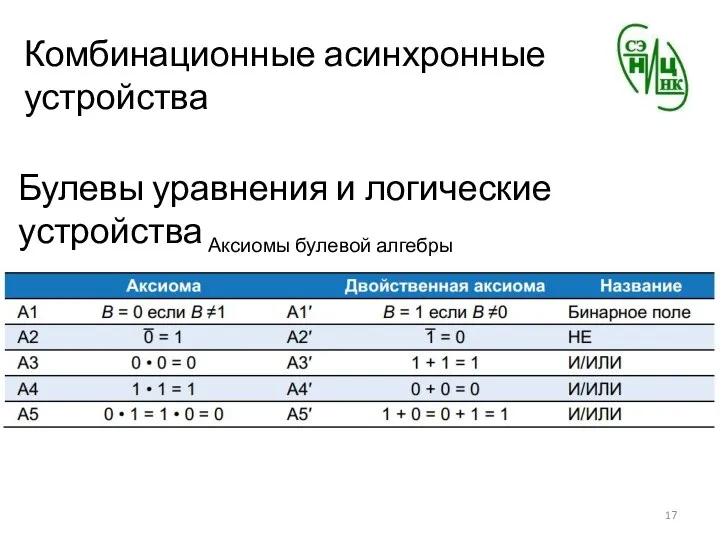

- 17. Комбинационные асинхронные устройства Булевы уравнения и логические устройства Аксиомы булевой алгебры

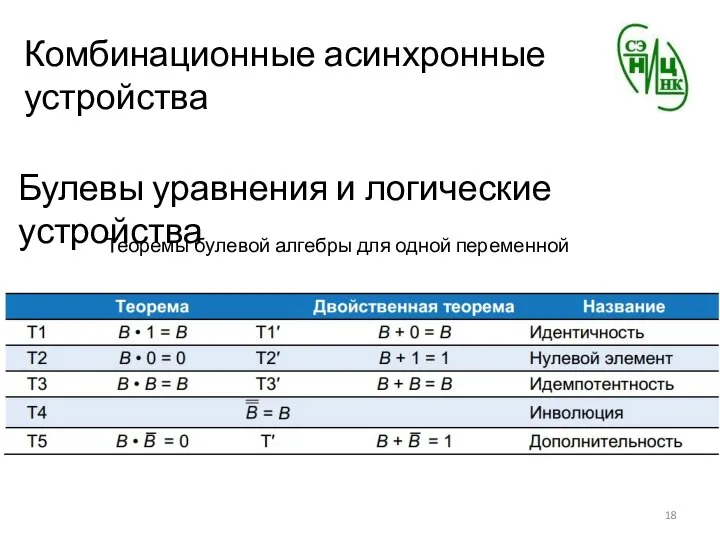

- 18. Комбинационные асинхронные устройства Булевы уравнения и логические устройства Теоремы булевой алгебры для одной переменной

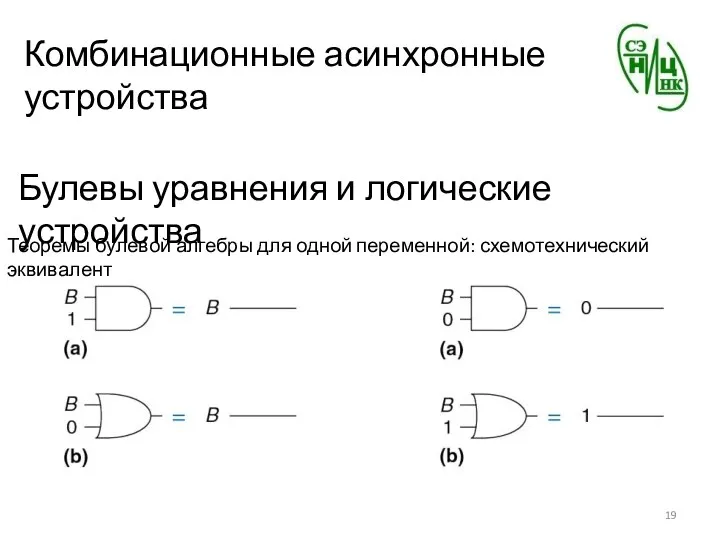

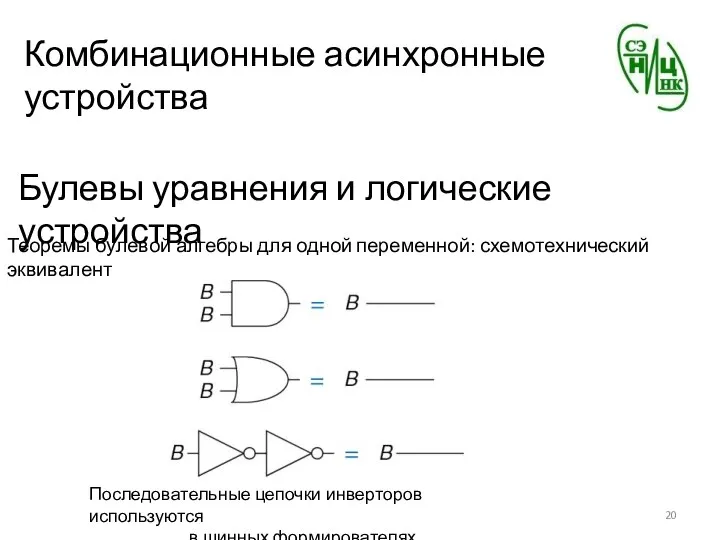

- 19. Комбинационные асинхронные устройства Булевы уравнения и логические устройства Теоремы булевой алгебры для одной переменной: схемотехнический эквивалент

- 20. Комбинационные асинхронные устройства Булевы уравнения и логические устройства Теоремы булевой алгебры для одной переменной: схемотехнический эквивалент

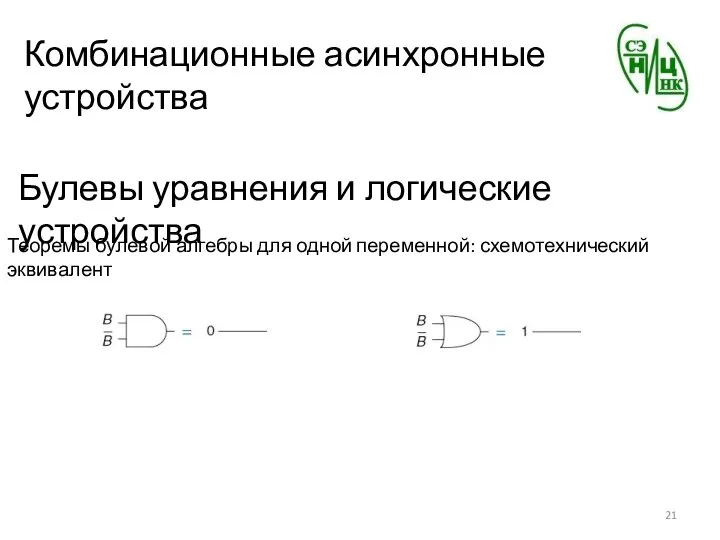

- 21. Комбинационные асинхронные устройства Булевы уравнения и логические устройства Теоремы булевой алгебры для одной переменной: схемотехнический эквивалент

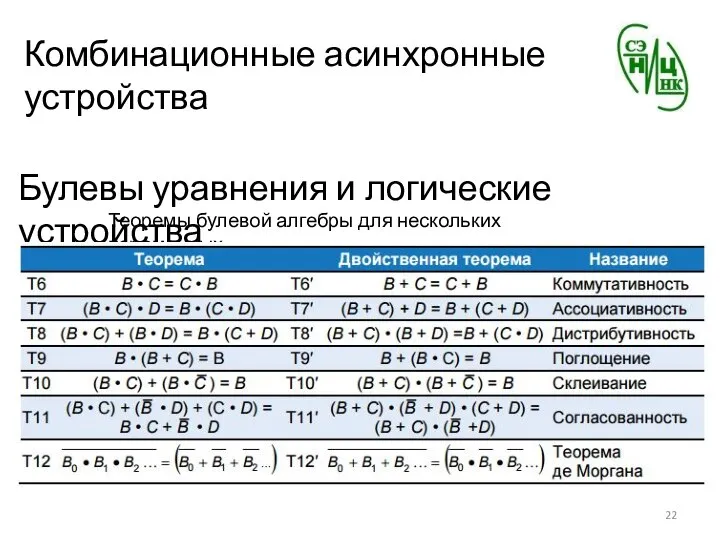

- 22. Комбинационные асинхронные устройства Булевы уравнения и логические устройства Теоремы булевой алгебры для нескольких переменных

- 23. Комбинационные асинхронные устройства Булевы уравнения и логические устройства Теорема де Моргана: схемотехнические эквиваленты

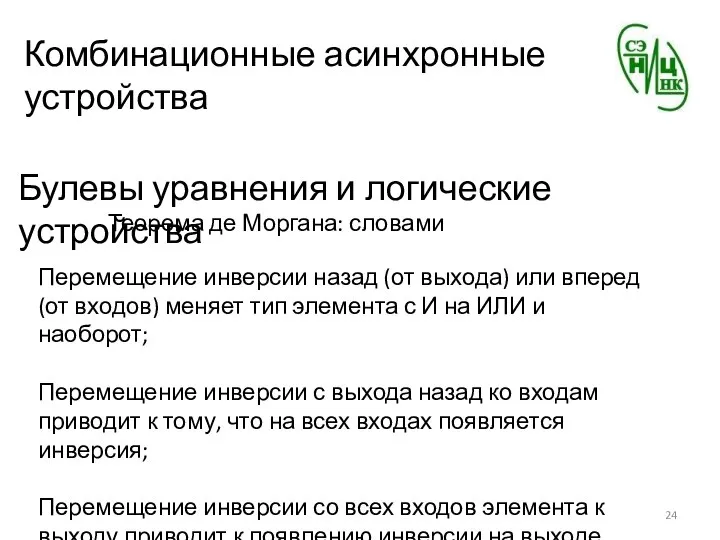

- 24. Комбинационные асинхронные устройства Булевы уравнения и логические устройства Теорема де Моргана: словами Перемещение инверсии назад (от

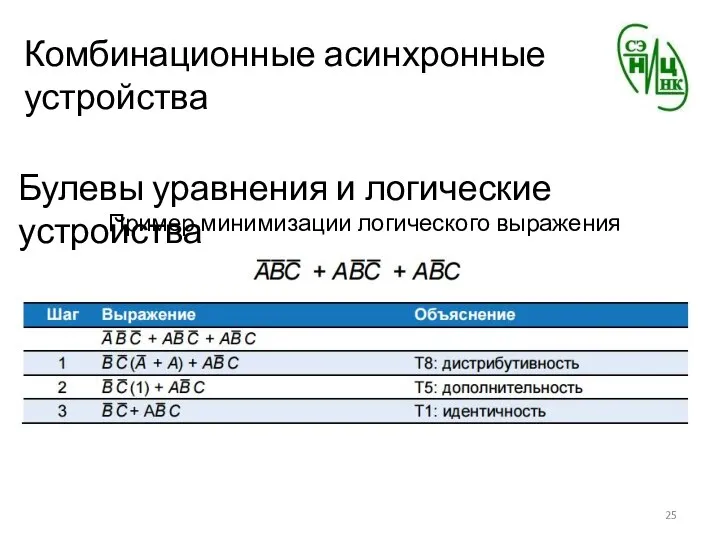

- 25. Комбинационные асинхронные устройства Булевы уравнения и логические устройства Пример минимизации логического выражения

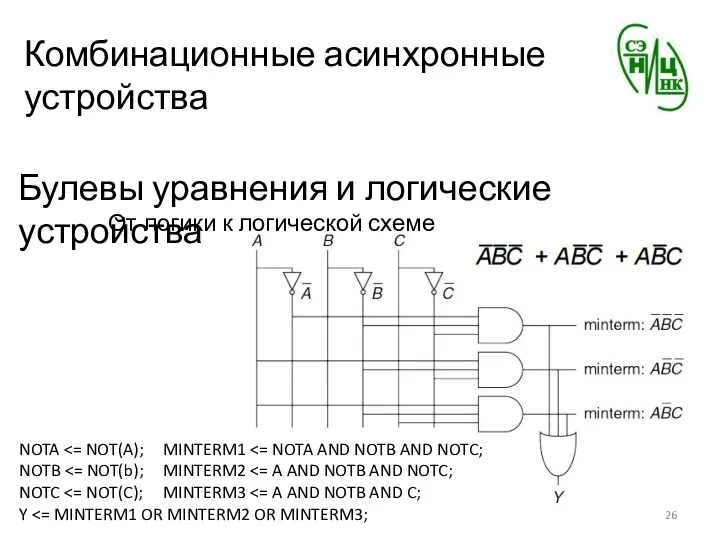

- 26. Комбинационные асинхронные устройства Булевы уравнения и логические устройства От логики к логической схеме NOTA NOTB NOTC

- 27. Комбинационные асинхронные устройства Правила рисования логических схем Входы изображаются на левой (или верхней) части схемы; Выходы

- 28. Комбинационные асинхронные устройства Карты Карно Карты Карно представляют собой наглядный метод для упрощения булевых уравнений. Карты

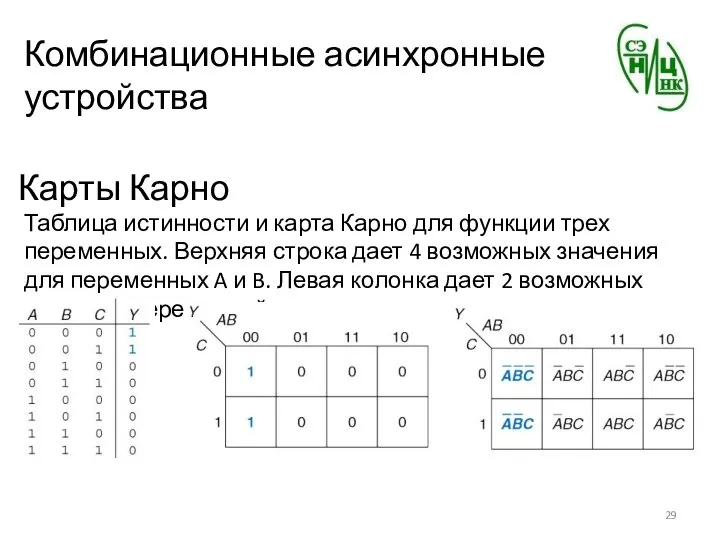

- 29. Комбинационные асинхронные устройства Карты Карно Таблица истинности и карта Карно для функции трех переменных. Верхняя строка

- 30. Комбинационные асинхронные устройства Карты Карно Каждая клетка карты Карно соответствует строке таблицы истинности и содержит значение

- 31. Комбинационные асинхронные устройства Карты Карно Как и раньше, мы могли бы использовать булеву алгебру для минимизации:

- 32. Комбинационные асинхронные устройства Карты Карно Переменные, для которых прямая и комплементарная формы попадают в один овал,

- 33. Комбинационные асинхронные устройства Карты Карно Карты Карно обеспечивают простой визуальный способ минимизации логических выражений. Просто обведите

- 34. Комбинационные асинхронные устройства Карты Карно Правила для нахождения минимального уравнения из карт Карно: Использовать меньше всего

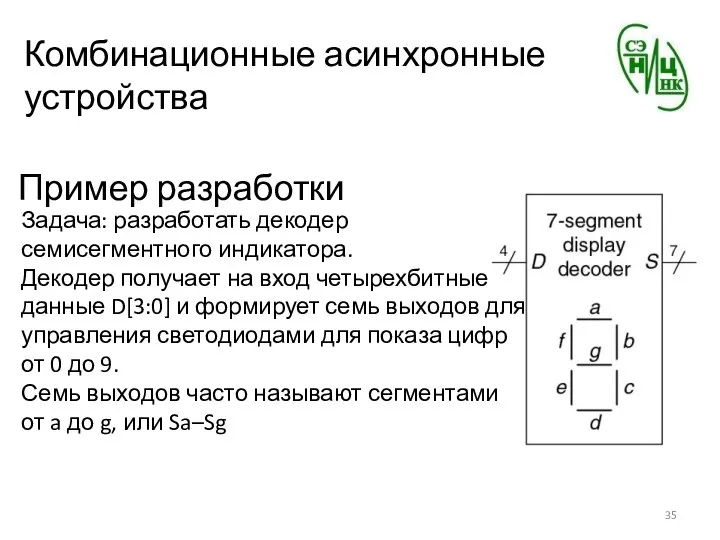

- 35. Комбинационные асинхронные устройства Пример разработки Задача: разработать декодер семисегментного индикатора. Декодер получает на вход четырехбитные данные

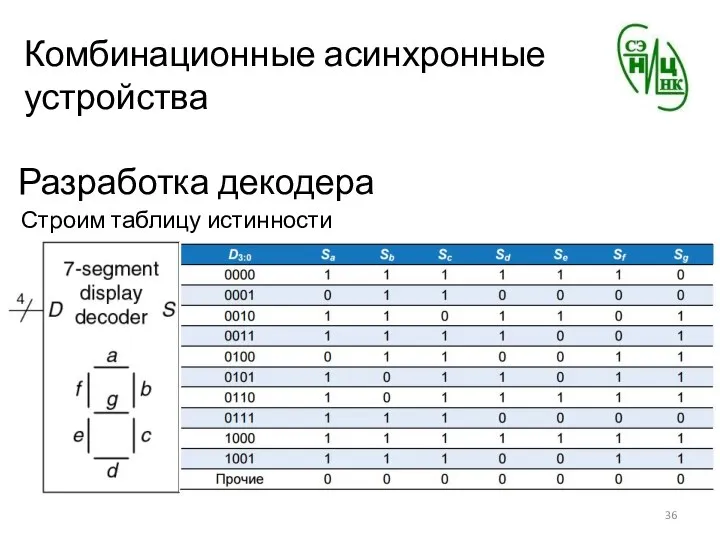

- 36. Комбинационные асинхронные устройства Разработка декодера Строим таблицу истинности

- 37. Комбинационные асинхронные устройства Разработка дешифратора Каждый из семи выходов является независимой функцией от четырех переменных. Карты

- 38. Комбинационные асинхронные устройства Разработка декодера Обводим первичные импликанты и записываем оптимизированные уравнения

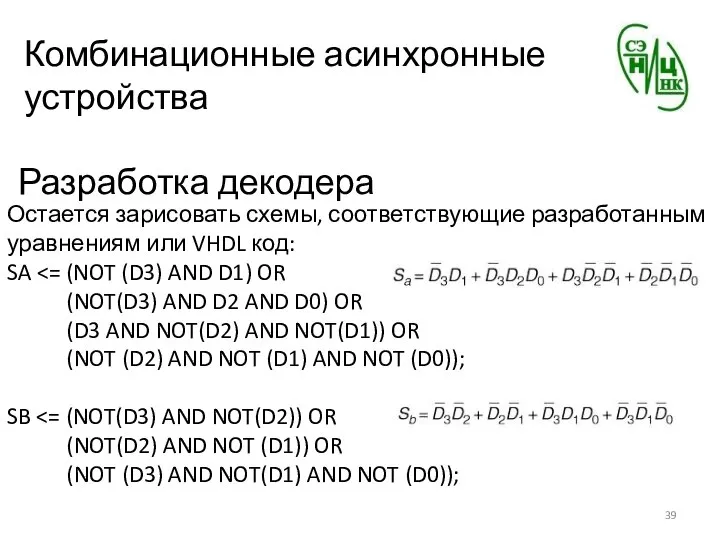

- 39. Комбинационные асинхронные устройства Разработка декодера Остается зарисовать схемы, соответствующие разработанным уравнениям или VHDL код: SA (NOT(D3)

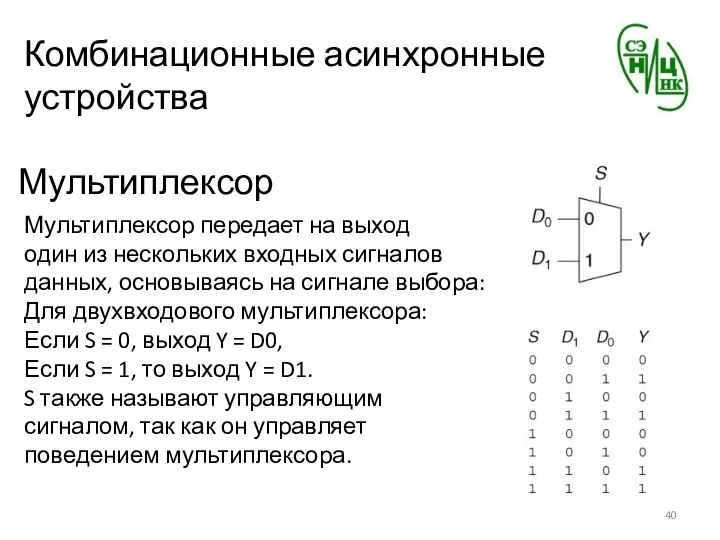

- 40. Комбинационные асинхронные устройства Мультиплексор Мультиплексор передает на выход один из нескольких входных сигналов данных, основываясь на

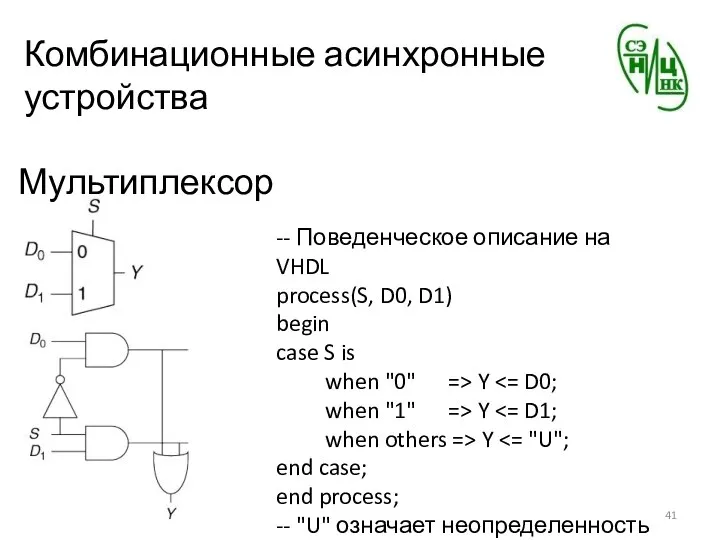

- 41. Комбинационные асинхронные устройства Мультиплексор -- Поведенческое описание на VHDL process(S, D0, D1) begin case S is

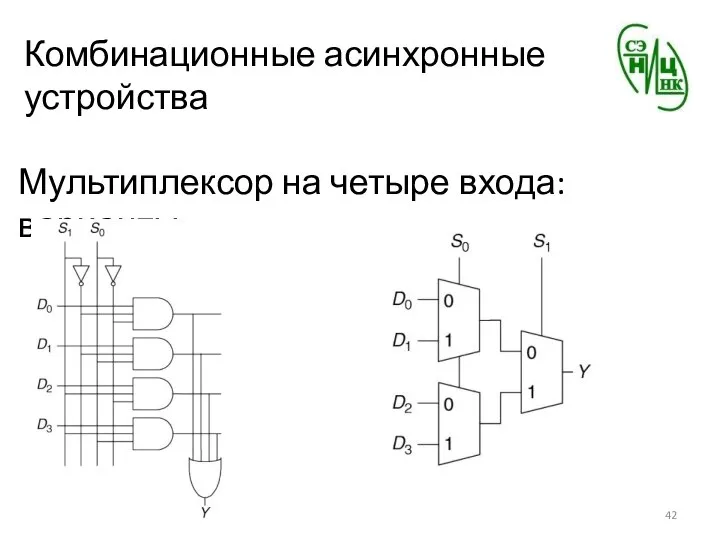

- 42. Комбинационные асинхронные устройства Мультиплексор на четыре входа: варианты

- 43. Комбинационные асинхронные устройства Мультиплексор на четыре входа: VHDL- код library ieee; use ieee.std_logic_1164.all; entity mux4 is

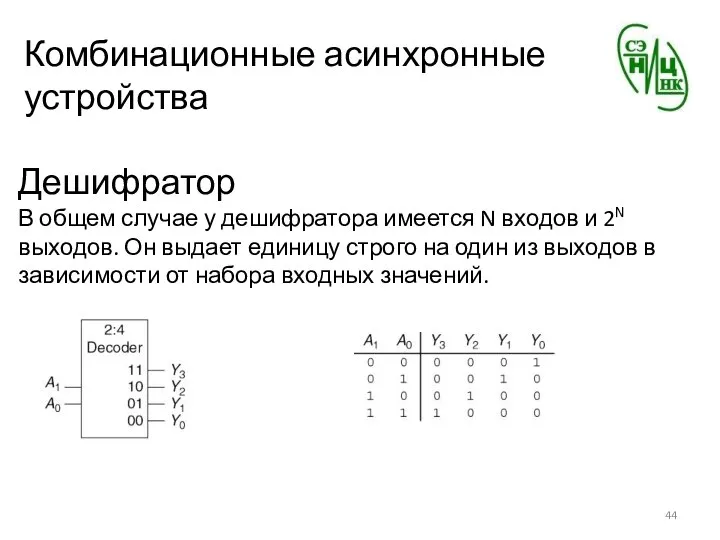

- 44. Комбинационные асинхронные устройства Дешифратор В общем случае у дешифратора имеется N входов и 2N выходов. Он

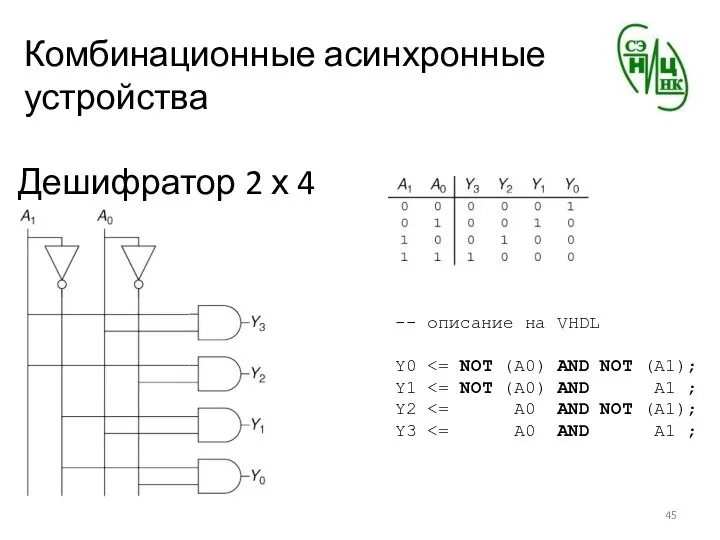

- 45. Комбинационные асинхронные устройства Дешифратор 2 х 4 -- описание на VHDL Y0 Y1 Y2 Y3

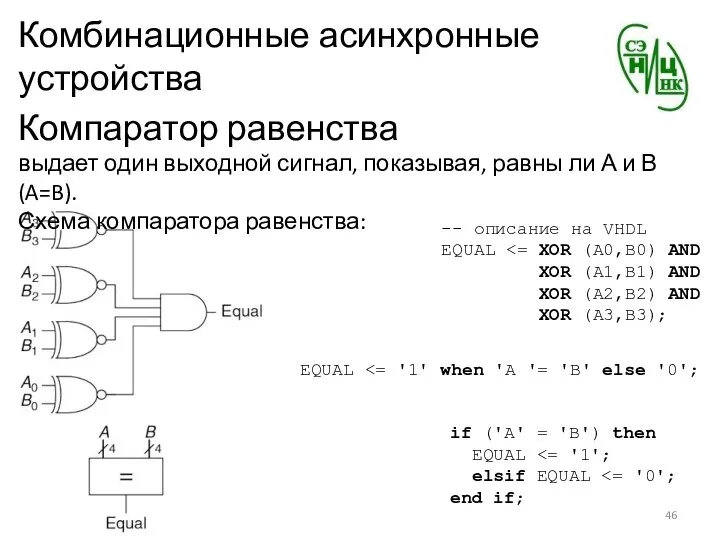

- 46. Комбинационные асинхронные устройства Компаратор равенства выдает один выходной сигнал, показывая, равны ли А и В (A=B).

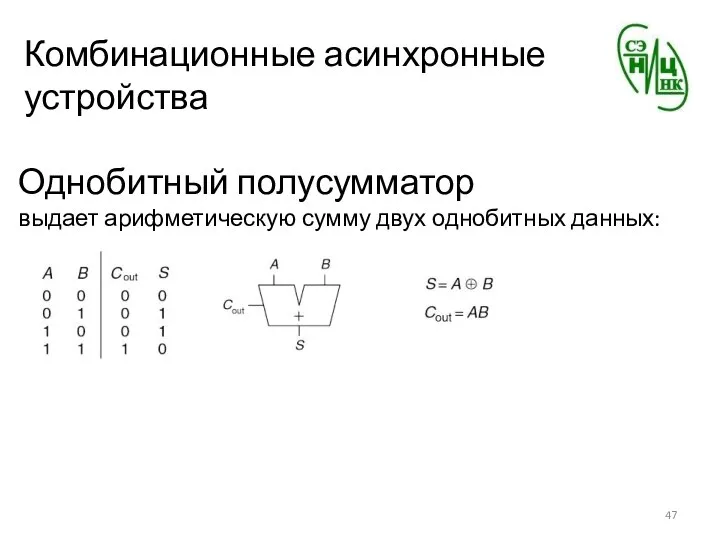

- 47. Комбинационные асинхронные устройства Однобитный полусумматор выдает арифметическую сумму двух однобитных данных:

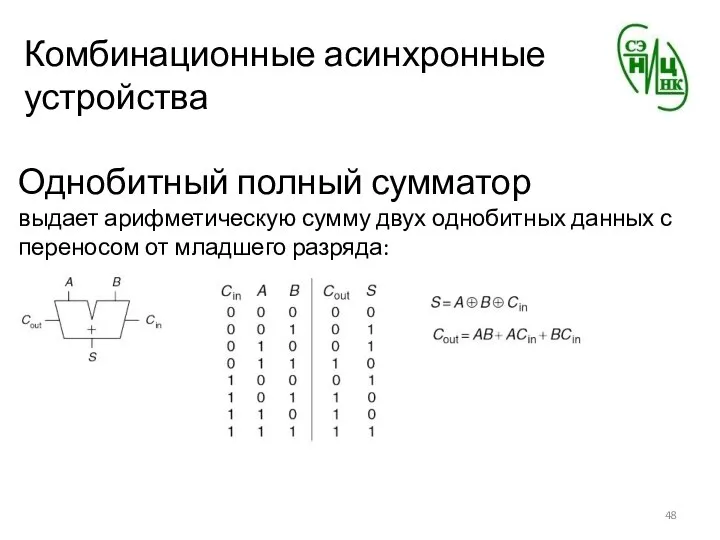

- 48. Комбинационные асинхронные устройства Однобитный полный сумматор выдает арифметическую сумму двух однобитных данных с переносом от младшего

- 49. Комбинационные асинхронные устройства Сумматор с последовательным переносом Строится из однобитных полных сумматоров (в первом разряде- однобитный

- 51. Скачать презентацию

4.2-Служба-трансфузиологии-многопрофильной-больницы

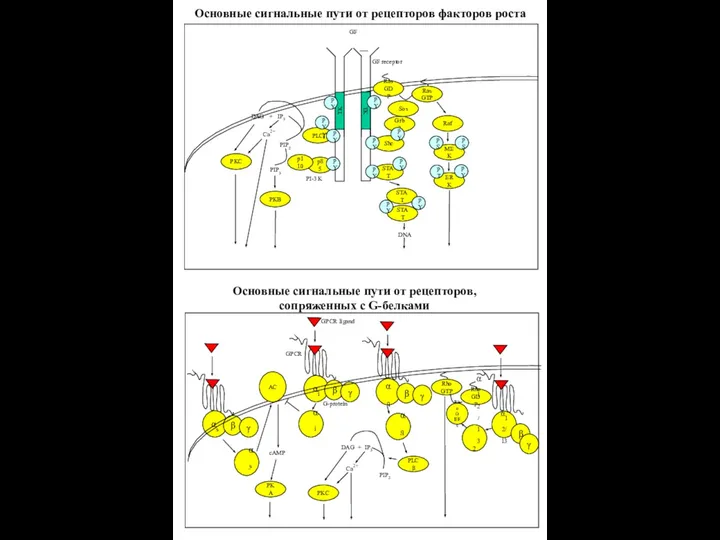

4.2-Служба-трансфузиологии-многопрофильной-больницы Pathways RTK and GPCR

Pathways RTK and GPCR Сайти інтернете

Сайти інтернете Отделочные работы

Отделочные работы Чемпионы мира по шахматам. Сильнейшие шахматисты от древности до наших дней

Чемпионы мира по шахматам. Сильнейшие шахматисты от древности до наших дней Строки Паскаль. Чем плох массив символов?

Строки Паскаль. Чем плох массив символов? ДЕРЖАВНІСТЬ ТА ДЕРЖАВНЕ УПРАВЛЯННЯ ЕКОНОМІКИ

ДЕРЖАВНІСТЬ ТА ДЕРЖАВНЕ УПРАВЛЯННЯ ЕКОНОМІКИ Внимательно слушайте – и всё услышите! Внимательно смотрите – и всё увидите! Думайте – и всё обязательно поймёте! Внимательно

Внимательно слушайте – и всё услышите! Внимательно смотрите – и всё увидите! Думайте – и всё обязательно поймёте! Внимательно  Мишель Фуко. Теория глагола

Мишель Фуко. Теория глагола Презентация по алгебре Алгебраические методы решения прикладных задач на экстремум

Презентация по алгебре Алгебраические методы решения прикладных задач на экстремум А ты знаешь как все начиналось? - презентация

А ты знаешь как все начиналось? - презентация Батик

Батик Орфограммы в суффиксах существительных

Орфограммы в суффиксах существительных  Формы самостоятельных занятий

Формы самостоятельных занятий АПИРОГ. ВОДА С КАРТИНКАМИ

АПИРОГ. ВОДА С КАРТИНКАМИ Интересные факты из жизни великих женщин-математиков

Интересные факты из жизни великих женщин-математиков Электроника NexGen

Электроника NexGen Медицина эпохи рабовладения

Медицина эпохи рабовладения Волшебный узелок

Волшебный узелок Поэтика Марины Цветаевой

Поэтика Марины Цветаевой Общественное служение христианина

Общественное служение христианина Звіт про роботу в конкурсах - презентация для начальной школы_

Звіт про роботу в конкурсах - презентация для начальной школы_ Эстетика Ренессанса

Эстетика Ренессанса Презентация по физкультуре Легкая атлетика организация соревнований

Презентация по физкультуре Легкая атлетика организация соревнований Ислам _

Ислам _ 2 класс 2 четверть Авторы: Хомутовская Л.Н., МОУ Саваслейская ср. шк. Каргина В.В., МОУ Новосельская ср. шк. 2005

2 класс 2 четверть Авторы: Хомутовская Л.Н., МОУ Саваслейская ср. шк. Каргина В.В., МОУ Новосельская ср. шк. 2005 Т р у х а н о в отдых & развлечения банкет-холл

Т р у х а н о в отдых & развлечения банкет-холл Особенности программирования на объектно-ориентированных языках

Особенности программирования на объектно-ориентированных языках