Содержание

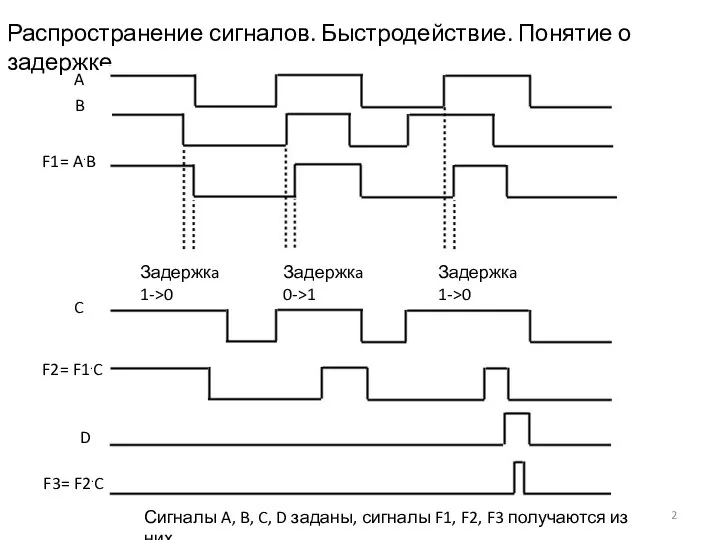

- 2. Распространение сигналов. Быстродействие. Понятие о задержке A B F1= A.B Задержкa 1->0 C F2= F1.C D

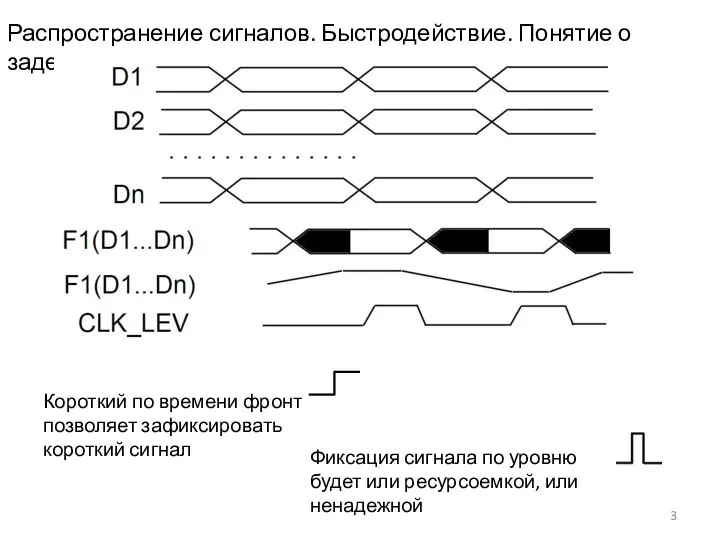

- 3. Распространение сигналов. Быстродействие. Понятие о задержке Короткий по времени фронт позволяет зафиксировать короткий сигнал Фиксация сигнала

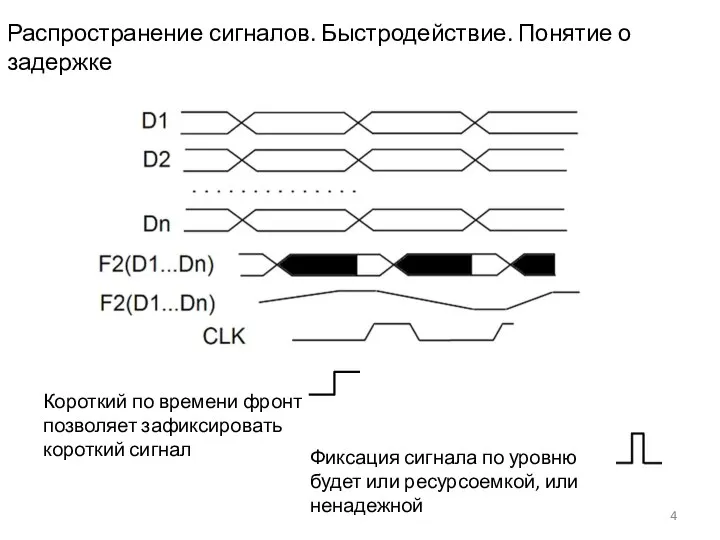

- 4. Распространение сигналов. Быстродействие. Понятие о задержке Короткий по времени фронт позволяет зафиксировать короткий сигнал Фиксация сигнала

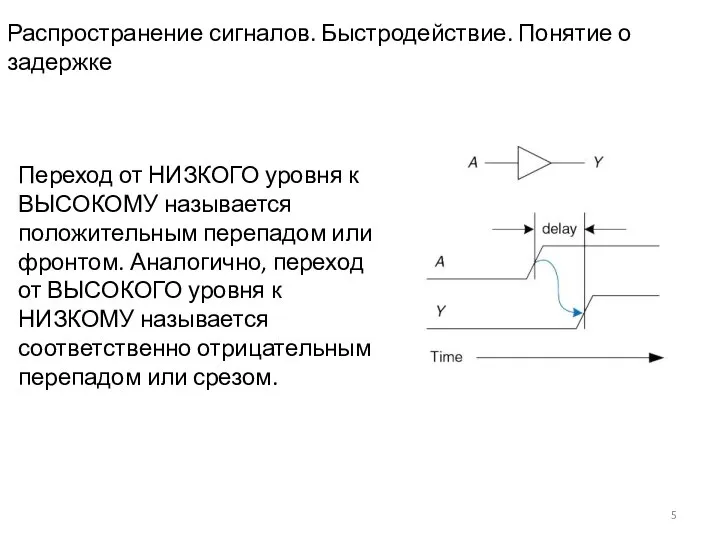

- 5. Распространение сигналов. Быстродействие. Понятие о задержке Переход от НИЗКОГО уровня к ВЫСОКОМУ называется положительным перепадом или

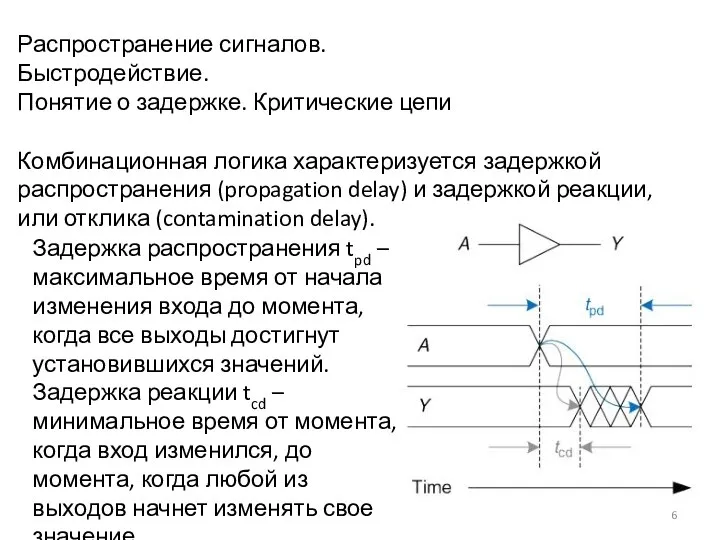

- 6. Распространение сигналов. Быстродействие. Понятие о задержке. Критические цепи Задержка распространения tpd –максимальное время от начала изменения

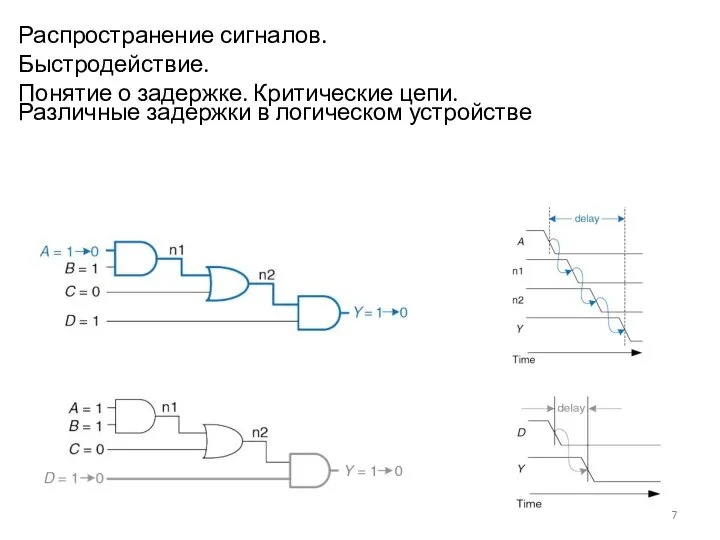

- 7. Различные задержки в логическом устройстве Распространение сигналов. Быстродействие. Понятие о задержке. Критические цепи.

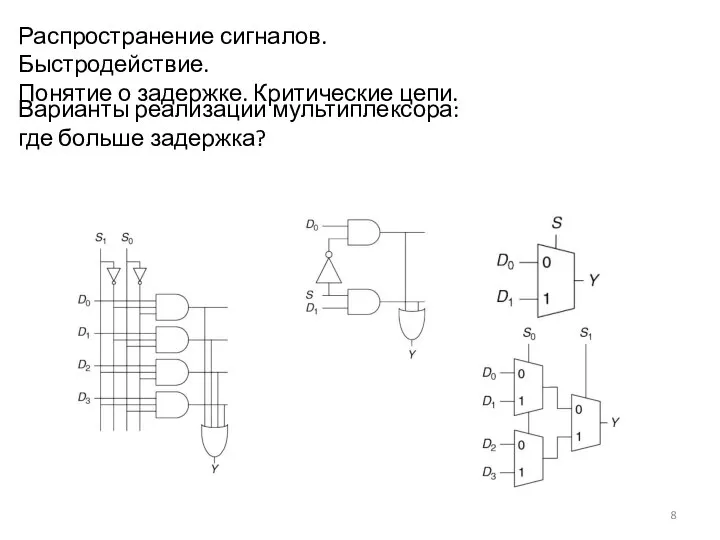

- 8. Варианты реализации мультиплексора: где больше задержка? Распространение сигналов. Быстродействие. Понятие о задержке. Критические цепи.

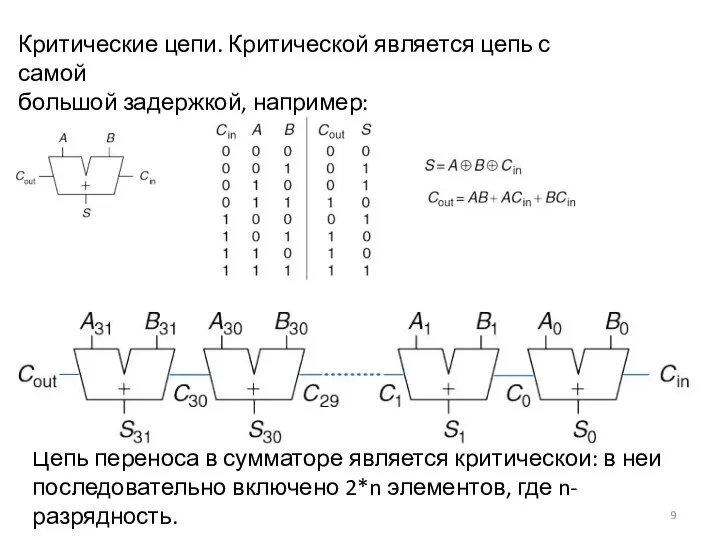

- 9. Цепь переноса в сумматоре является критической: в ней последовательно включено 2*n элементов, где n- разрядность. Критические

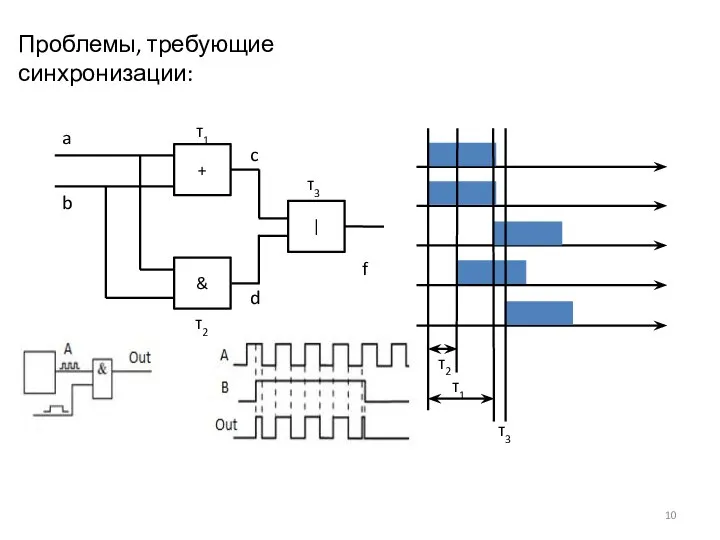

- 10. Проблемы, требующие синхронизации: f

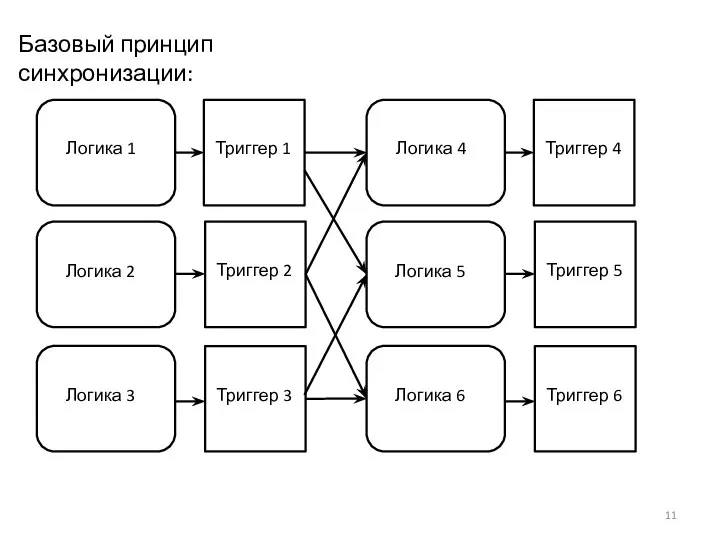

- 11. Базовый принцип синхронизации:

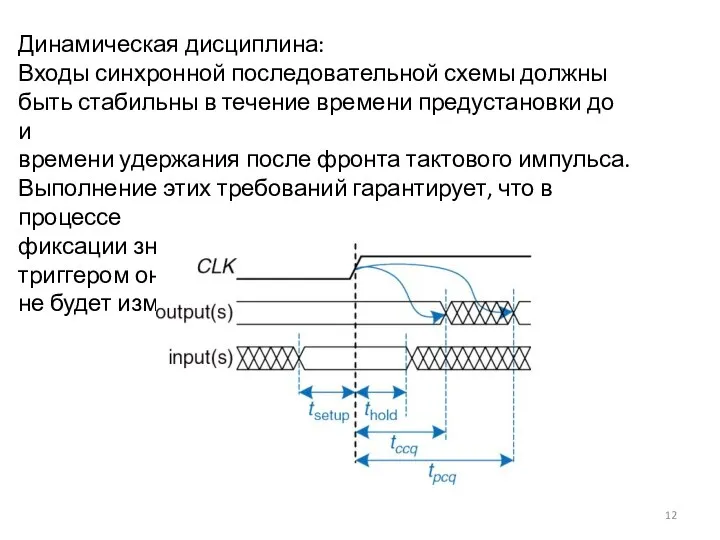

- 12. Динамическая дисциплина: Входы синхронной последовательной схемы должны быть стабильны в течение времени предустановки до и времени

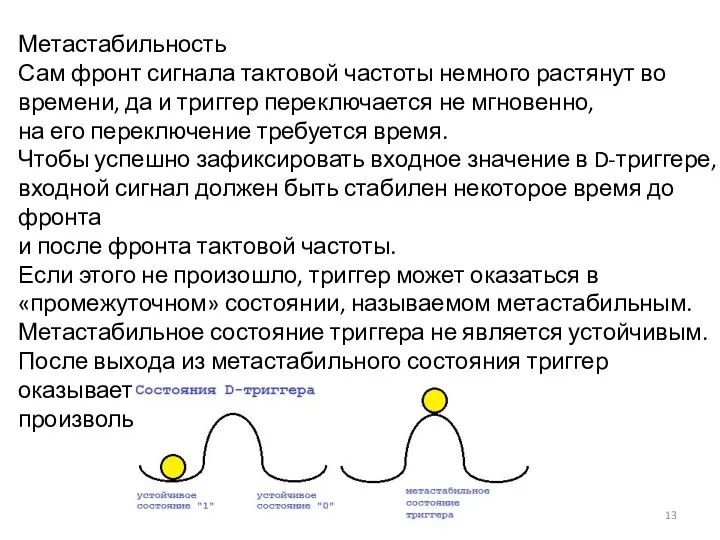

- 13. Метастабильность Сам фронт сигнала тактовой частоты немного растянут во времени, да и триггер переключается не мгновенно,

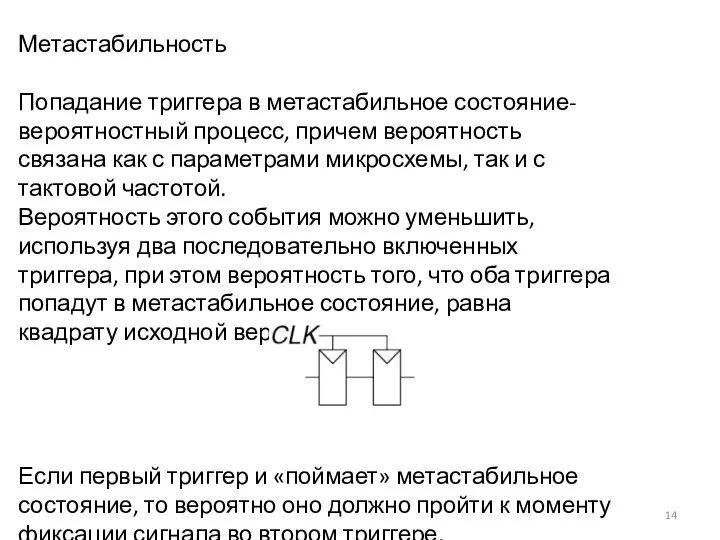

- 14. Метастабильность Попадание триггера в метастабильное состояние- вероятностный процесс, причем вероятность связана как с параметрами микросхемы, так

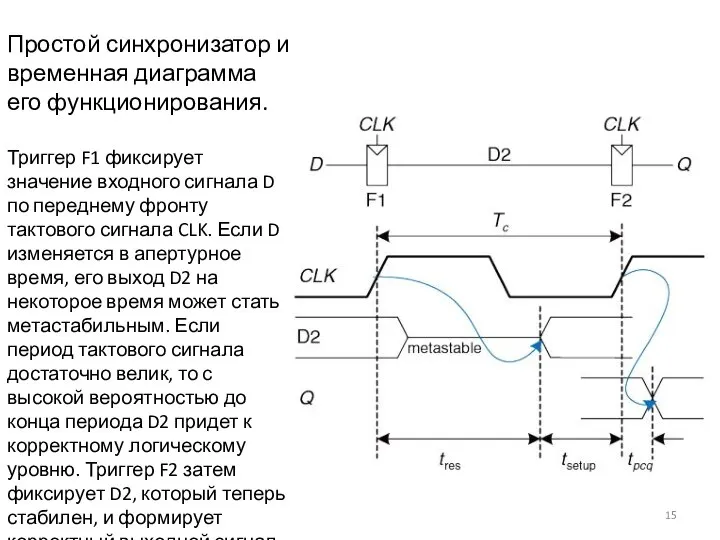

- 15. Простой синхронизатор и временная диаграмма его функционирования. Триггер F1 фиксирует значение входного сигнала D по переднему

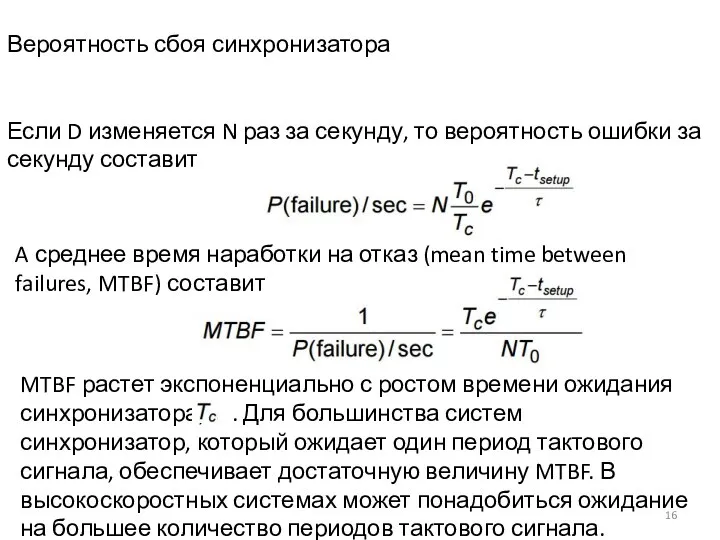

- 16. Вероятность сбоя синхронизатора Если D изменяется N раз за секунду, то вероятность ошибки за секунду составит

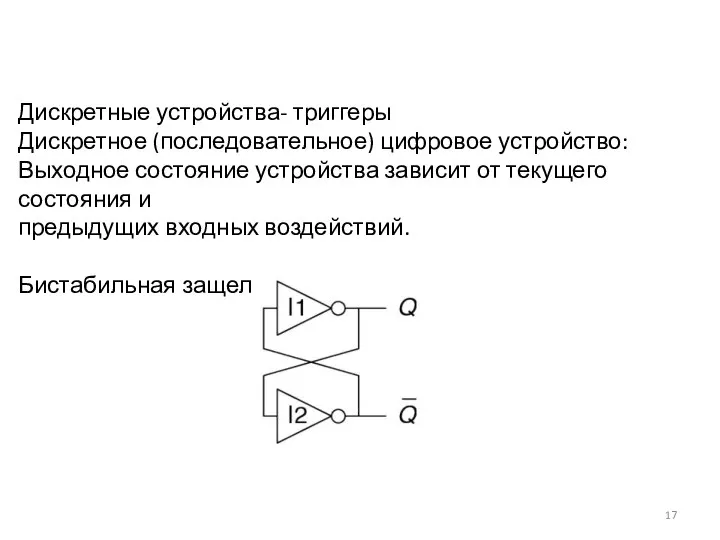

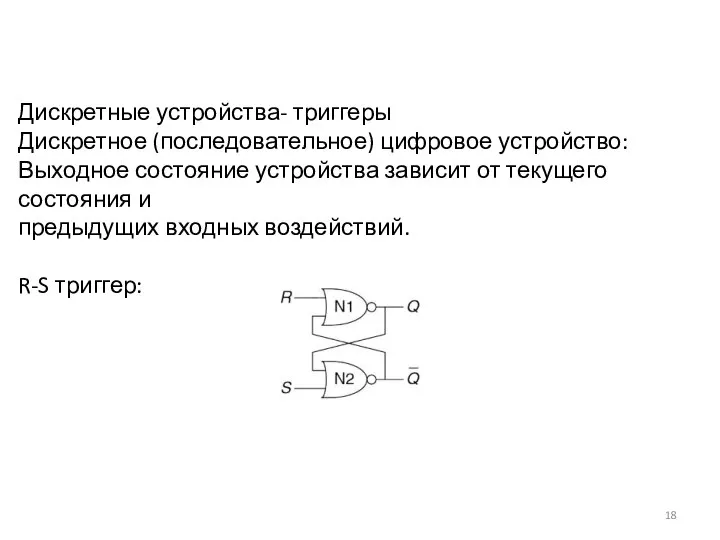

- 17. Дискретные устройства- триггеры Дискретное (последовательное) цифровое устройство: Выходное состояние устройства зависит от текущего состояния и предыдущих

- 18. Дискретные устройства- триггеры Дискретное (последовательное) цифровое устройство: Выходное состояние устройства зависит от текущего состояния и предыдущих

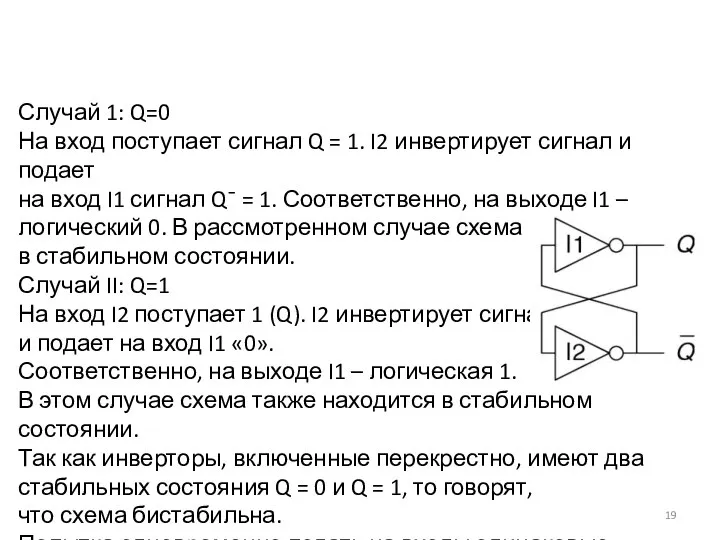

- 19. Случай 1: Q=0 На вход поступает сигнал Q = 1. I2 инвертирует сигнал и подает на

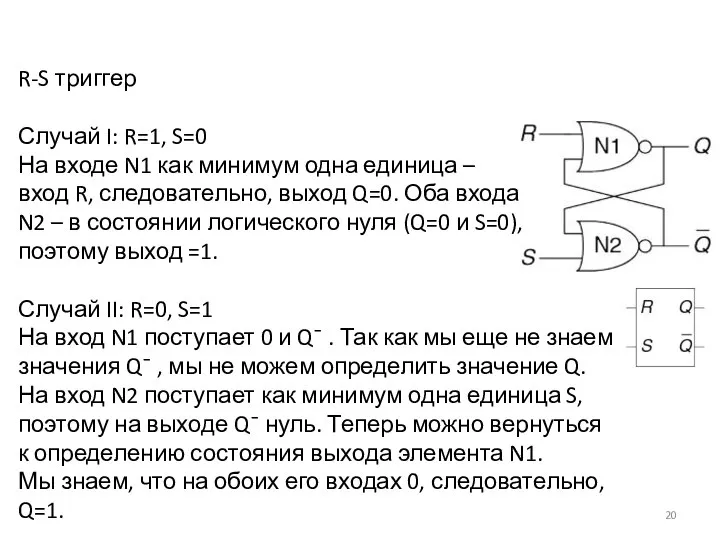

- 20. R-S триггер Случай I: R=1, S=0 На входе N1 как минимум одна единица – вход R,

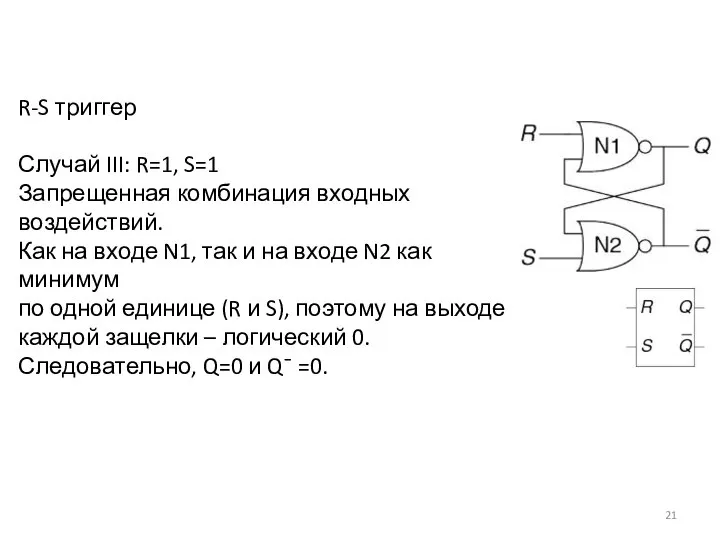

- 21. R-S триггер Случай III: R=1, S=1 Запрещенная комбинация входных воздействий. Как на входе N1, так и

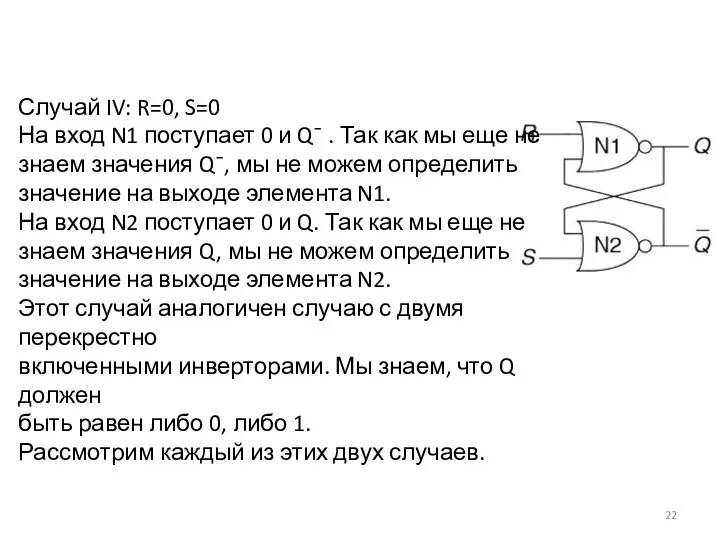

- 22. Случай IV: R=0, S=0 На вход N1 поступает 0 и Q¯ . Так как мы еще

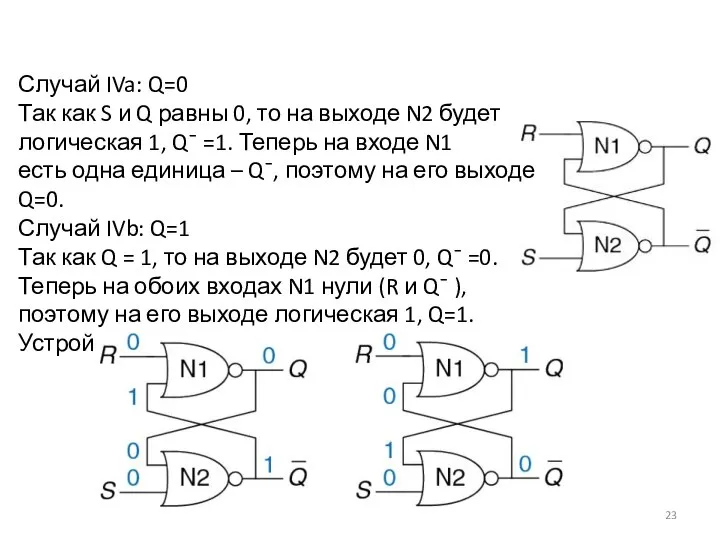

- 23. Случай IVa: Q=0 Так как S и Q равны 0, то на выходе N2 будет логическая

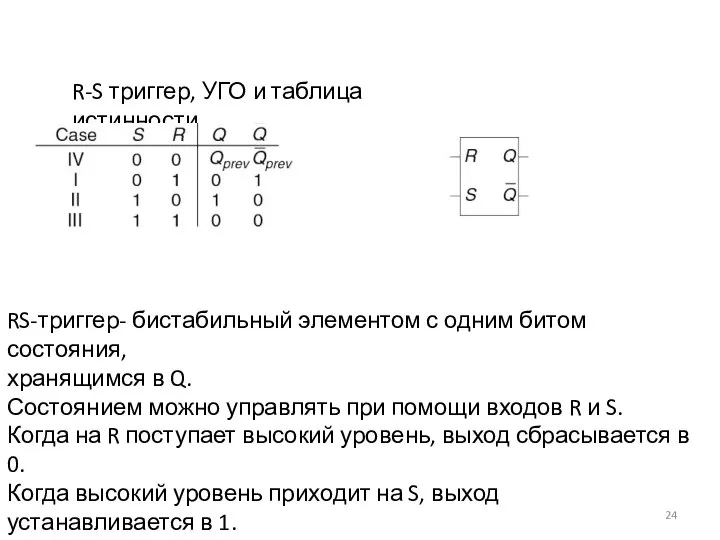

- 24. R-S триггер, УГО и таблица истинности RS-триггер- бистабильный элементом с одним битом состояния, хранящимся в Q.

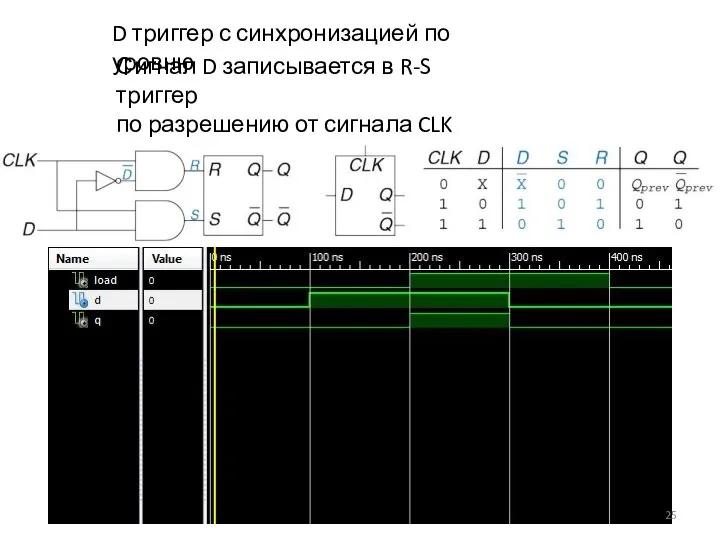

- 25. D триггер с синхронизацией по уровню Сигнал D записывается в R-S триггер по разрешению от сигнала

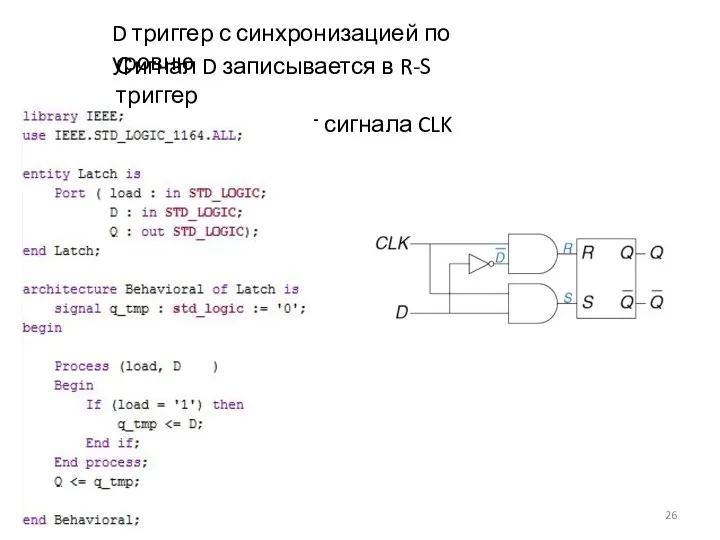

- 26. D триггер с синхронизацией по уровню Сигнал D записывается в R-S триггер по разрешению от сигнала

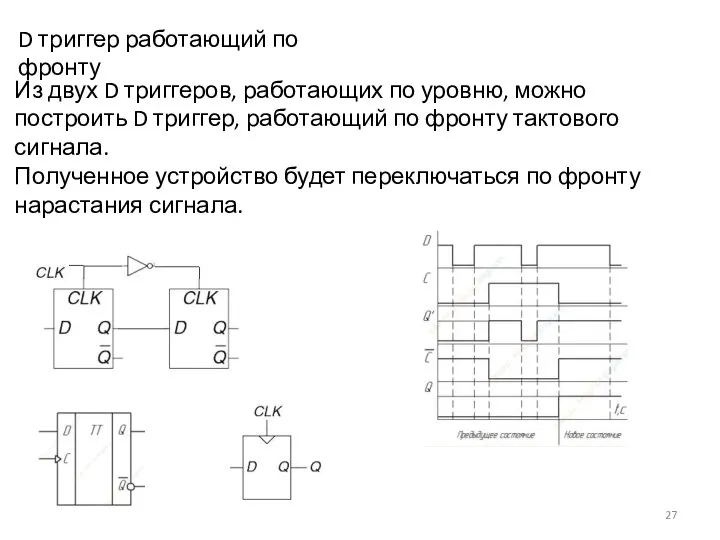

- 27. D триггер работающий по фронту Из двух D триггеров, работающих по уровню, можно построить D триггер,

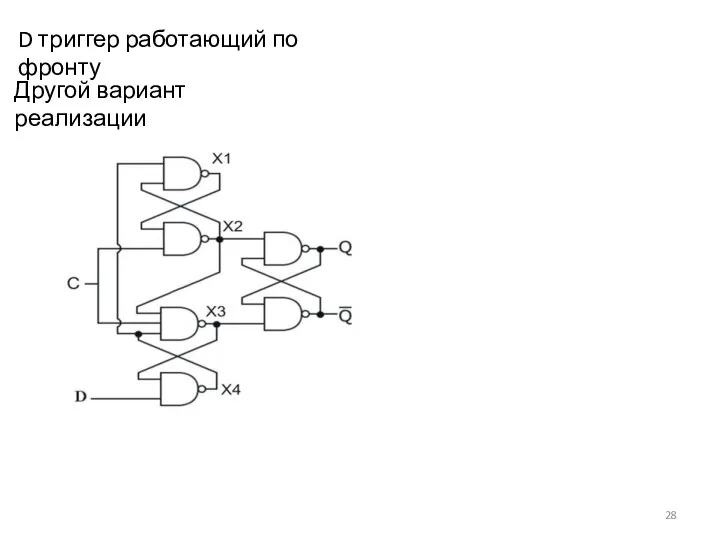

- 28. D триггер работающий по фронту Другой вариант реализации

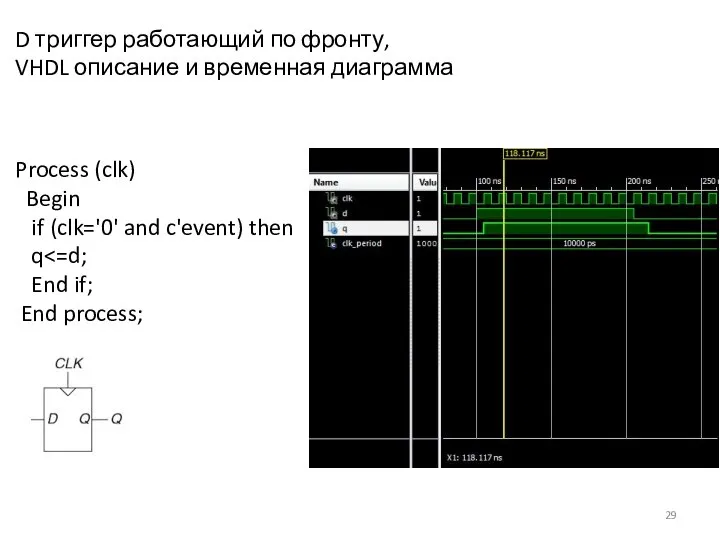

- 29. D триггер работающий по фронту, VHDL описание и временная диаграмма Process (clk) Begin if (clk='0' and

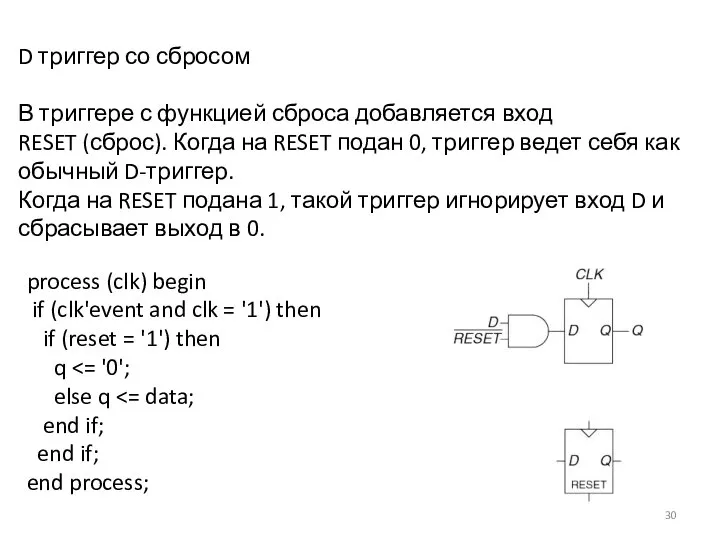

- 30. D триггер со сбросом В триггере с функцией сброса добавляется вход RESET (сброс). Когда на RESET

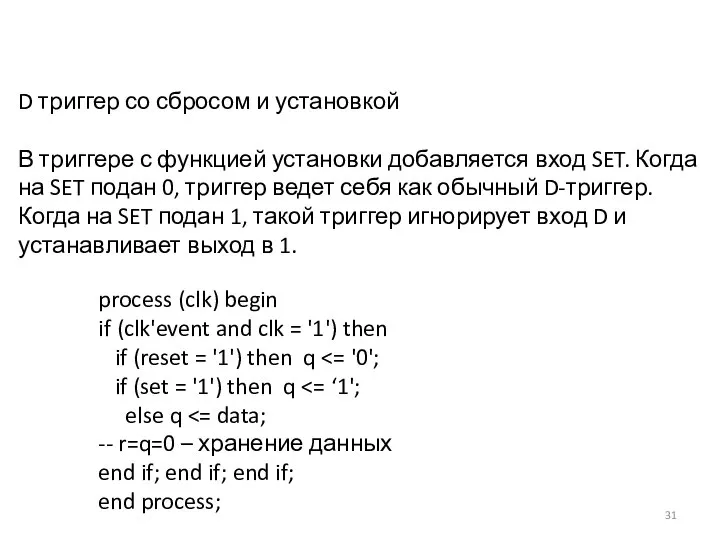

- 31. D триггер со сбросом и установкой В триггере с функцией установки добавляется вход SET. Когда на

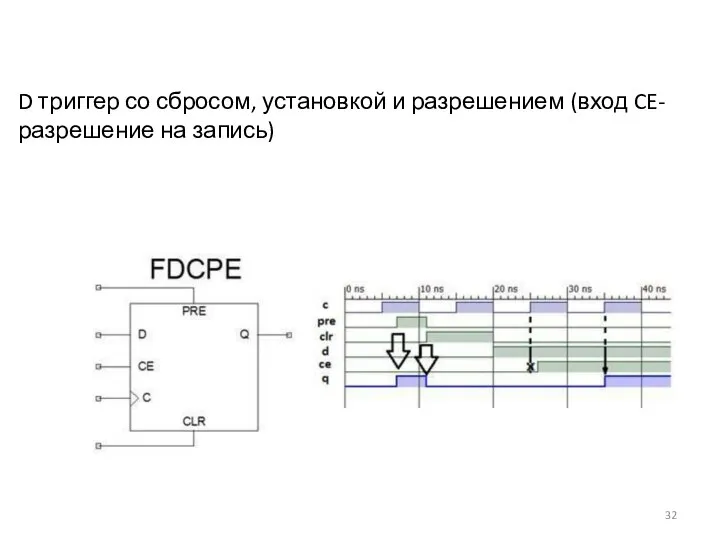

- 32. D триггер со сбросом, установкой и разрешением (вход CE-разрешение на запись)

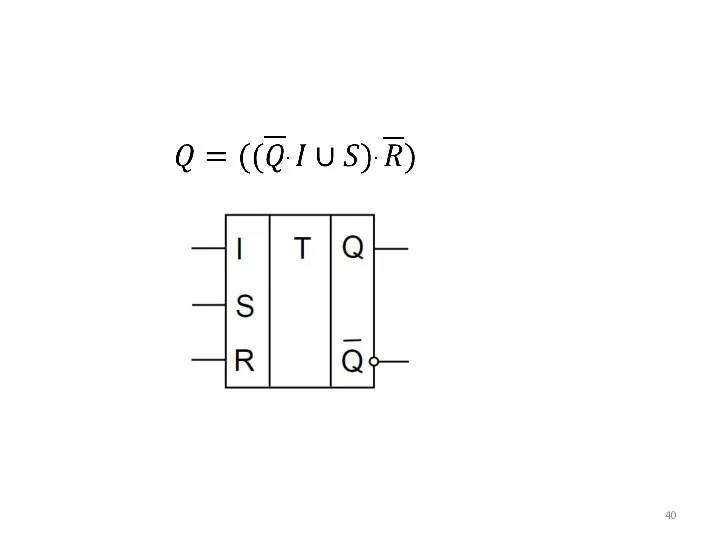

- 33. Счетный триггер D- триггер, у которого инверсный выход подключен к входу, называется Т- триггером. После поступления

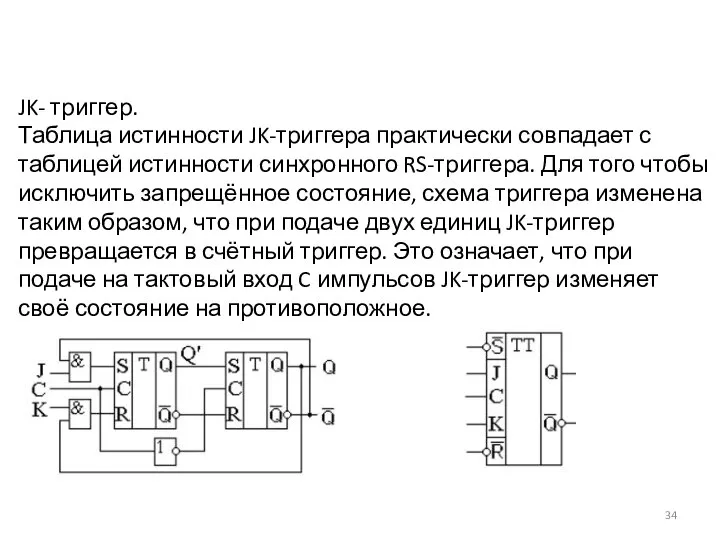

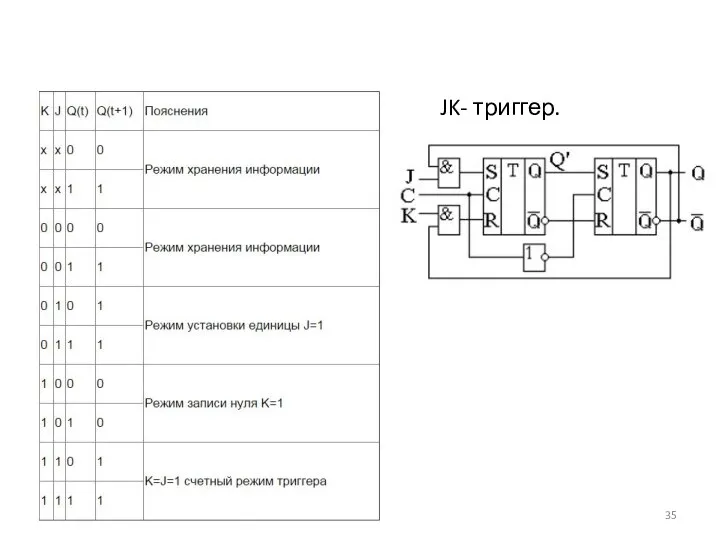

- 34. JK- триггер. Таблица истинности JK-триггера практически совпадает с таблицей истинности синхронного RS-триггера. Для того чтобы исключить

- 35. JK- триггер.

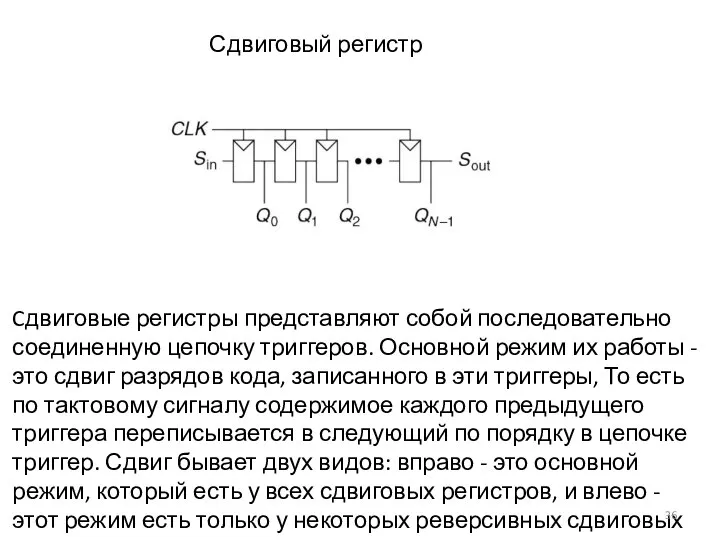

- 36. Сдвиговый регистр Cдвиговые регистры представляют собой последовательно соединенную цепочку триггеров. Основной режим их работы - это

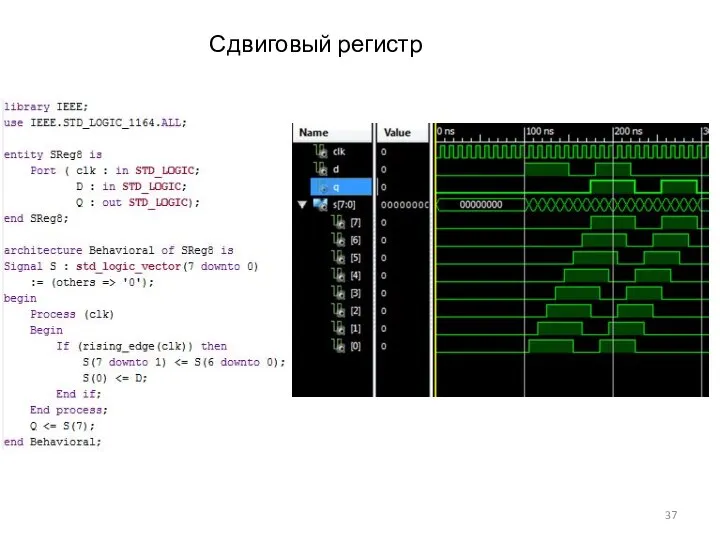

- 37. Сдвиговый регистр

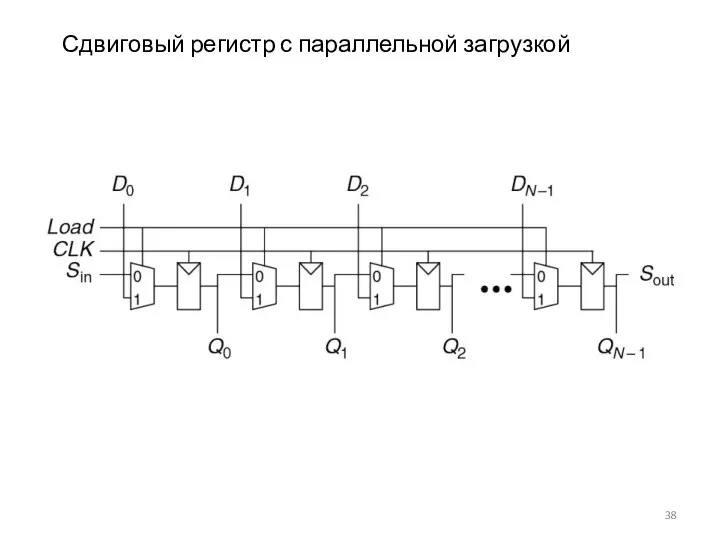

- 38. Сдвиговый регистр с параллельной загрузкой

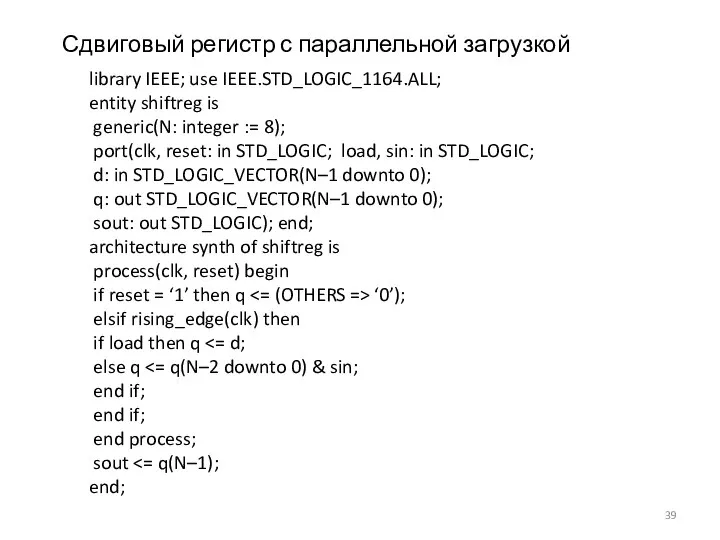

- 39. Сдвиговый регистр с параллельной загрузкой library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity shiftreg is generic(N: integer := 8);

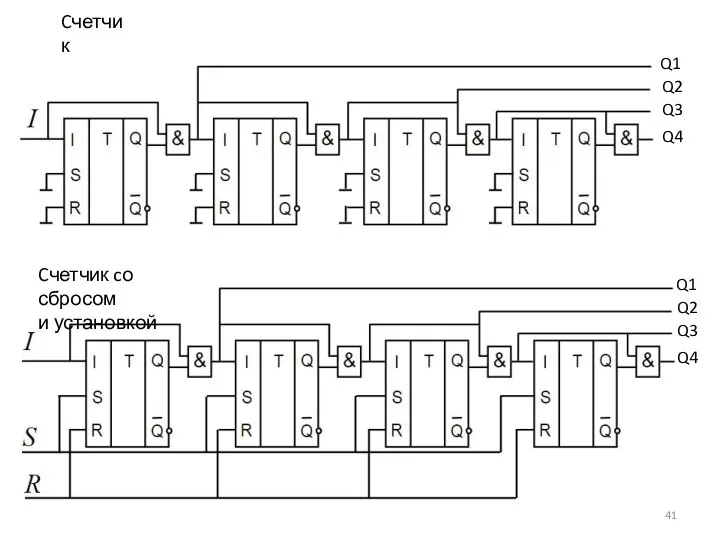

- 41. Cчетчик Q1 Q2 Q3 Q4 Q2 Q3 Q4 Q1 Cчетчик cо сбросом и установкой

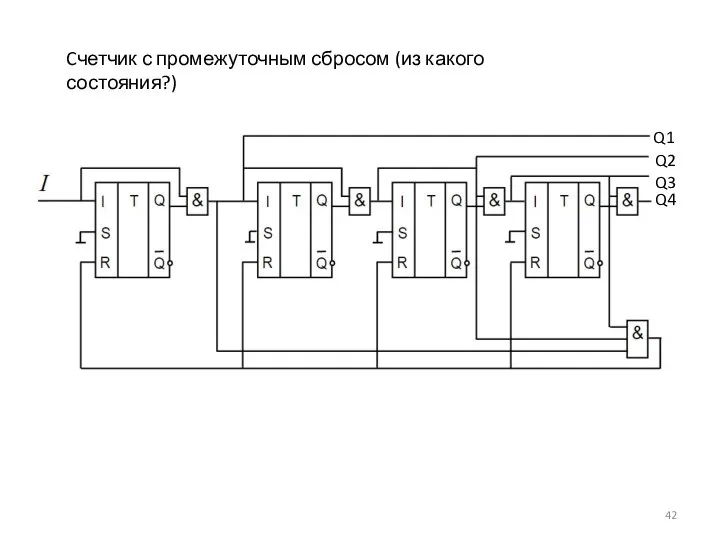

- 42. Cчетчик с промежуточным сбросом (из какого состояния?) Q1 Q2 Q3 Q4

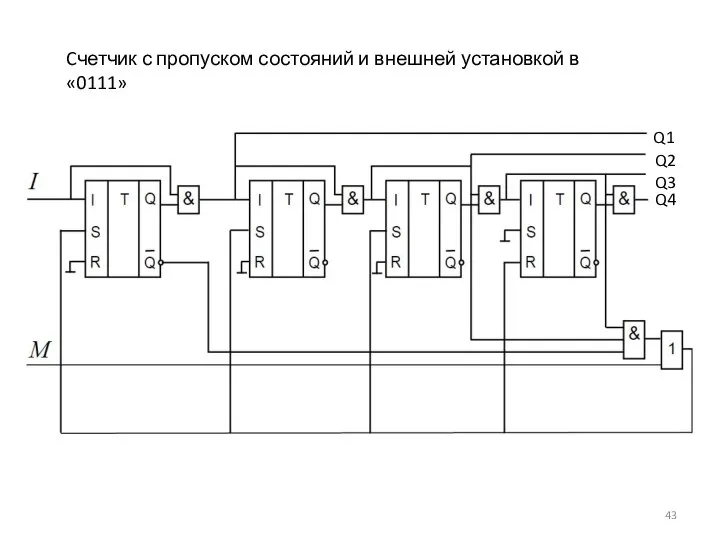

- 43. Cчетчик с пропуском состояний и внешней установкой в «0111» Q1 Q2 Q3 Q4

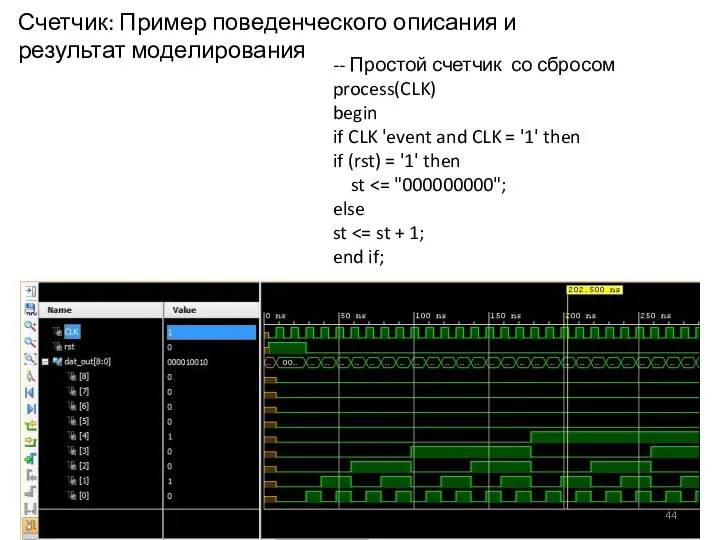

- 44. Счетчик: Пример поведенческого описания и результат моделирования -- Простой счетчик со сбросом process(CLK) begin if CLK

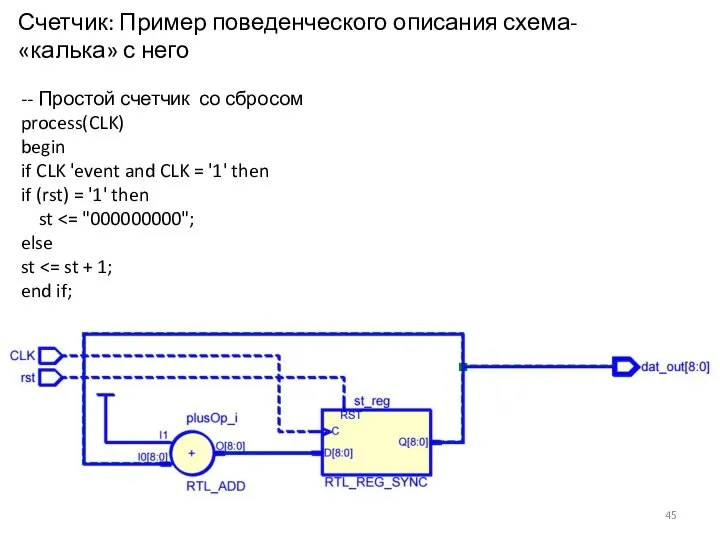

- 45. Счетчик: Пример поведенческого описания схема- «калька» с него -- Простой счетчик со сбросом process(CLK) begin if

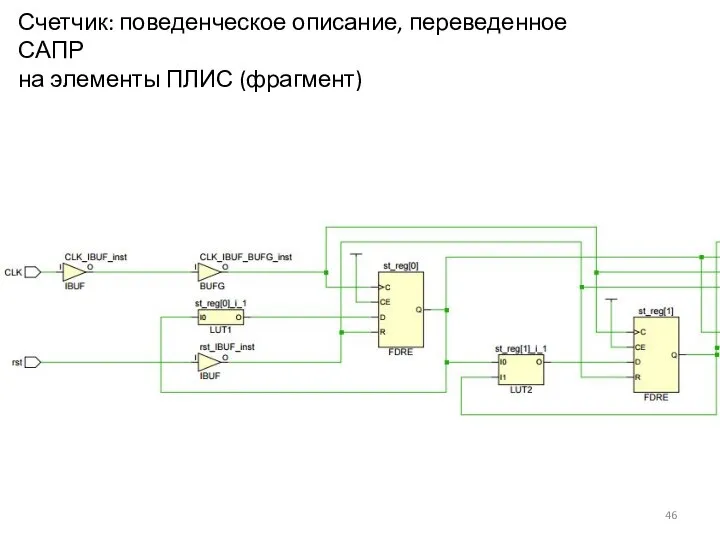

- 46. Счетчик: поведенческое описание, переведенное САПР на элементы ПЛИС (фрагмент)

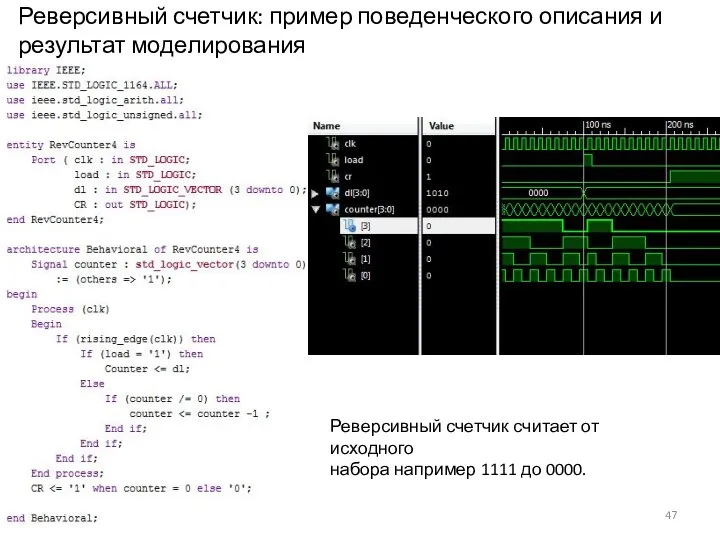

- 47. Реверсивный счетчик: пример поведенческого описания и результат моделирования Реверсивный счетчик считает от исходного набора например 1111

- 49. Скачать презентацию

Od osoby, która cię kocha

Od osoby, która cię kocha Презентация на тему "Изучение проблемы роста объемов необоснованных вызовов скорой медицинской помощи" - скачать презентаци

Презентация на тему "Изучение проблемы роста объемов необоснованных вызовов скорой медицинской помощи" - скачать презентаци Свертывание информации. Виды свертывания. Понятие и структура текста. (Тема 3)

Свертывание информации. Виды свертывания. Понятие и структура текста. (Тема 3) Политический режим

Политический режим Экономический эффект. Экономическая эффективность Управление качеством

Экономический эффект. Экономическая эффективность Управление качеством Организационная культура как мультидисциплинарный объект изучения Круглый стол (технология) Сатикова С.В.

Организационная культура как мультидисциплинарный объект изучения Круглый стол (технология) Сатикова С.В.  Успенский храм

Успенский храм Web-сайт сети магазинов для видеоигр «GameTime»

Web-сайт сети магазинов для видеоигр «GameTime» Соединения кальция в строительстве и природе

Соединения кальция в строительстве и природе Политический режим

Политический режим Моя будущая профессия МОУ «Красночетайская СОШ»

Моя будущая профессия МОУ «Красночетайская СОШ»  Русская народная песня и костюм

Русская народная песня и костюм Радиобиология

Радиобиология  Микропроцессорные системы. Основные положения. (Лекция 1)

Микропроцессорные системы. Основные положения. (Лекция 1) Успех

Успех Я люблю спорт

Я люблю спорт Коллекция одежды: «Нетленность каменной души Воспета музыкой поэта…». Детский театр мод: «Грация»

Коллекция одежды: «Нетленность каменной души Воспета музыкой поэта…». Детский театр мод: «Грация» Тяговый расчет трактора

Тяговый расчет трактора Японская молодежная мода

Японская молодежная мода СЛАЙДЫ ПО ТЕОРИИ ГОСУДАРСТВА

СЛАЙДЫ ПО ТЕОРИИ ГОСУДАРСТВА Перспектива та її особливості

Перспектива та її особливості Система электрооборудования Лада 2190 (Гранта)

Система электрооборудования Лада 2190 (Гранта) Визначення шляхів підвищення рівня фінансової стійкості підприємства

Визначення шляхів підвищення рівня фінансової стійкості підприємства Праздник Курбан-Байрам

Праздник Курбан-Байрам психодиагностика взрослых

психодиагностика взрослых Презентация Бананы

Презентация Бананы Олимпийское движение в ракурсе философско-социалогического кризиса олимпийской идеи

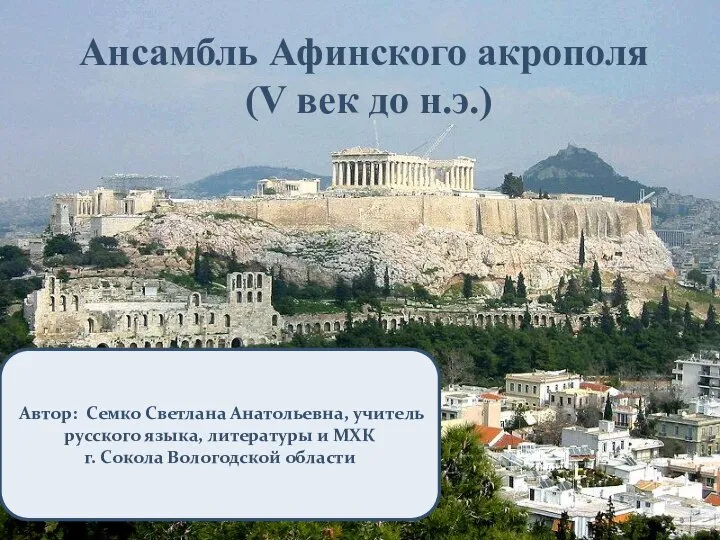

Олимпийское движение в ракурсе философско-социалогического кризиса олимпийской идеи Презентация "Афинский Акрополь" - скачать презентации по МХК

Презентация "Афинский Акрополь" - скачать презентации по МХК