Содержание

- 2. Курс «Архитектура персональных ЭВМ» является составной частью курса «Архитектура вычислительных машин и систем». Целью преподавания дисциплины

- 3. Дисциплина читается на 3 Курсе в 5 семестре. В соответствии с рабочей программой предусмотрено Лекции 48

- 4. ПЭВМ – это вычислительная система, представляющая собой совокупность аппаратных (в литературе встречается термин Hard Ware) и

- 6. МП – это "сердце" ПЭВМ. Он осуществляет вычисления по хранящейся в ОП программе и обеспечивает общее

- 7. Классификация ЭBM oбычнo cвязывaeтcя c coвepшeнcтвoвaниeм элeмeнтнoй бaзы. Элeмeнтнaя бaзa 1-гo пoкoлeния (кoнeц 40-x гoдoв) -

- 8. Дaльнeйшee paзвитиe aппapaтныx и пpoгpaммныx cpeдcтв ЭBM пpивeлo к пoявлeнию мyльтипpoгpaммиpoвaния (мyльти - мнoгo), тo ecть

- 9. Ведущие разработчики программ и устройств решили разработать пособие стандарта – спецификацию РСхх, предназначенную для аппаратуры, работающей

- 15. ПРОЦЕССОРЫ ШЕСТОГО ПОКОЛЕНИЯ Существуют Pentium III с частотами 450, 500, 500 Е, 533 ЕВ, 550 Е,

- 16. В Coppermine есть дополнительный VI слой разводки проводников. Расстояние между слоями 0,18 мкм, поэтому путь к

- 17. Athlon (K 7) с частотами 500, 550, 600, 650, 700 МГц по 0,25 мкм-технологии, а в

- 18. Pentium IV (Willamette) 1,5 ГГц. В нём новое ядро, а также применена новая технология Advanced Dinamic

- 19. Конвейерная обработка информации Иногда лучше проводить конвейерную обработку информации. Она улучшает использование аппаратных ресурсов для заданного

- 20. Векторная обработка информации В векторных конвейерах создаётся множество функциональных элементов, каждый из которых выполняет определённую операцию

- 21. Концепция потоковых ВС Существуют трудности, связанные с решением проблемы автоматизации параллельного программирования, необходимой для обеспечения эффективного

- 22. 3.Пoнятиe пpoгpaммнoгo oбecпeчeния Пpoгpaммнoe или мaтeмaтичecкoe oбecпeчeниe (в мaтeмaтичecкoй энциклoпeдии - этo cинoнимы) - этo coвoкyпнocть

- 24. Скачать презентацию

Курс «Архитектура персональных ЭВМ» является составной частью курса «Архитектура вычислительных машин

Курс «Архитектура персональных ЭВМ» является составной частью курса «Архитектура вычислительных машин

Целью преподавания дисциплины является вооружение выпускника современными знаниями в области архитектуры персональных ЭВМ(ПЭВМ), сведениями о составе и принципах функционирования системного программного обеспечения ПЭВМ, методами управления внешними устройствами и функциональными частями ПЭВМ на основе наиболее широко используемых инструментальных систем.

В результате изучения дисциплины студенты должны:

знать:

основные проблемы и направления развития ПЭВМ;

тенденции развития архитектур ПЭВМ;

основы построения и использования ОЗУ, КЭШ и дисковой памяти;

основы построения файловых систем;

принципы управления памятью ПЭВМ в различных режимах;

принципы передачи и приема информации через параллельный и последовательный порты, в том числе с использованием USB архитектуры;

принципы использования прерываний и исключений В ПЭВМ;

принципы работы с портами устройств ПЭВМ;

принципы управления блоками и узлами ПЭВМ;

уметь:

выбирать и применять средства ВТ, средства программирования для эффективной эксплуатации ПЭВМ;

осуществлять управление узлами и блоками ПЭВМ для решения конкретных прикладных задач;

проектировать основные сервисы и режимы функционирования прикладного программного обеспечения в реальном и защищенном режимах работы;

разрабатывать программное обеспечение для управления ресурсами ПЭВМ;

применять методы повышения производительности и надежности программного обеспечения для ПЭВМ;

решать прикладные задачи уровня пользователя ПЭВМ;

1.Предмет курса, его задачи и цели

Дисциплина читается на 3 Курсе в 5 семестре.

В соответствии с рабочей

Дисциплина читается на 3 Курсе в 5 семестре.

В соответствии с рабочей

Лекции 48 часов

Лабораторные занятия 34 часа

Экзамен 5 семестр

Всего аудиторных часов

по дисциплине 82

ЛИТЕРАТУРА

Максимов Н.В., Партыка Т.Л., Попов И.И Архитектура ЭВМ и вычислительных систем. —М.: Форум, 2008. — 512с.

Гук.М.Ю. Аппаратные средства РС. Энциклопедия. –ЗАО «Питер», 2008.

Жмакин А.П. Архитектура ЭВМ. — BHV-Санкт-Петербург, 2008 г. . — 320 с.

Крейгон Р. Архитектура компьютеров и ее реализация. — М.: Мир, 2004. — 412с

Демидович Е.М. Программирование на Си. Минск: Из-во Университетское, 2005 г.

Демидович Е.М.. Программирование на ассемблере. Минск: Из-во Университетское, 2003г.

Кулаков В.И. Программирование внешних устройтсва. Издательский дом “Питер”, 2004

Гук М.И, Юров В.С.Процессоры Pentium 4 Athlon и Duron.Издательский дом “Питер”, 2001.

Касаткин А.И. Управление ресурсами. Мн.: Высшая школа,1992.

Григорьев В.Л. Архитектура и программирование арифметического сопроцессора.– М.: Энергоатомиздат, 1991.– 208 с.

Нортон П. Программно-аппаратная организация IBM PC: Пер. с англ.– М.: Радио и связь, 1992.– 336 с.

Венгер В.А. и др. Аппаратура персональных компьютеров и ее программирование. IBM PC/XT/AT и PS/2. -М.: Радио и связь, 1995.

ПЭВМ – это вычислительная система, представляющая собой совокупность аппаратных (в литературе

ПЭВМ – это вычислительная система, представляющая собой совокупность аппаратных (в литературе

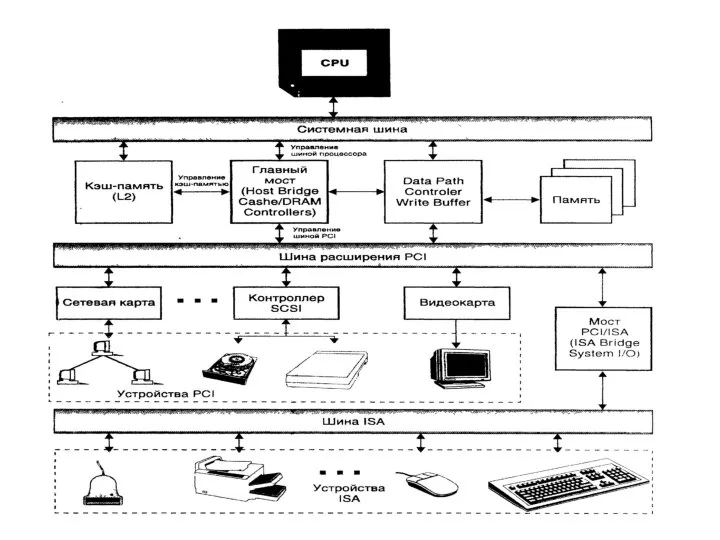

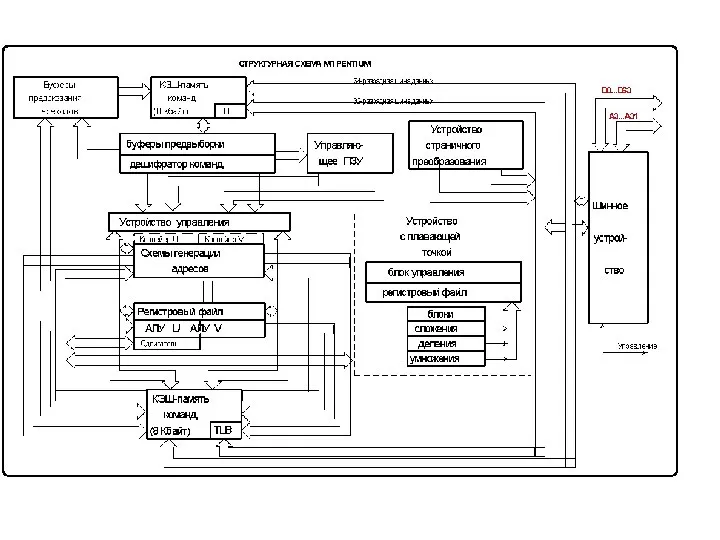

Принципы взаимодействия основных частей ПЭВМ.

Системная шина предназначена для организации обмена информацией между всеми компонентами компьютера. Все основные блоки персонального компьютера подсоединены к системной шине (рис. 1 ). Основной функцией системной шины является обеспечение взаимодействия между центральным процессором и остальными электронными компонентами компьютера. По проводам этой шины осуществляется передача данных, их адресов, а также управляющей информации. Соответственно этому выделено три группы.

2. Общие сведения о ПЭВМ. Классификация, основные характеристики. Архитектура 16, 32, 64 разрядных ПЭВМ.

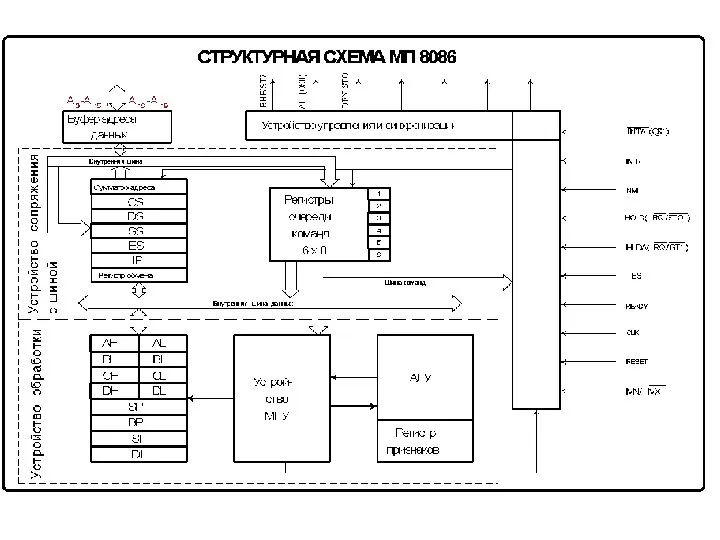

МП – это "сердце" ПЭВМ. Он осуществляет вычисления по хранящейся в

МП – это "сердце" ПЭВМ. Он осуществляет вычисления по хранящейся в

арифметико-логическое устройство (АЛУ), предназначенное для выполнения арифметических и логических операций;

устройства управления (УУ), обеспечивающее общее управление вычислительным процессом по программе и координацию работы всех устройств ПЭВМ.

П – это запоминающее устройство, предназначенное для хранения выполняемых программ и данных, непосредственно участвующих в операциях. Она имеет достаточно высокое быстродействие, но ограниченный объем. Функционально ОП делится на виды, основными из которых являются оперативное запоминающее устройство (ОЗУ) и постоянное запоминающее устройство (ПЗУ).

ОЗУ служит для приема, хранения и выдачи информации. В нем содержатся программы и данные, доступные для использования процессором, а также промежуточные и окончательные результаты вычислений. ОЗУ в ПЭВМ является энергозависимым. Это означает исчезновение информации при отключении питания.

ПЗУ, являясь энергонезависимым, используется для хранения часто используемых (универсальных) программ и данных. Таких, как программы ОС и ее информационные структуры.

Логически ОП можно представить в виде совокупности ячеек, доступ к каждой из которых осуществляется путем указания ее адреса.

Классификация ЭBM oбычнo cвязывaeтcя c coвepшeнcтвoвaниeм элeмeнтнoй бaзы. Элeмeнтнaя бaзa 1-гo

Классификация ЭBM oбычнo cвязывaeтcя c coвepшeнcтвoвaниeм элeмeнтнoй бaзы. Элeмeнтнaя бaзa 1-гo

Cлeдyющим шaгoм в иcпoльзoвaнии ЭBM явилacь cиcтeмa пaкeтнoй oбpaбoтки. Пpoгpaммы c дaнными зaпиcывaлиcь пocлeдoвaтeльнo нa oднy мaгнитнyю лeнтy. Coвoкyпнocть пpoгpaмм и дaнныx нa MЛ, paздeлeнныx cпeциaльными мeткaми, нaзывaют пaкeтoм. Дaлee пpoгpaммы из вxoднoгo пaкeтa пocлeдoвaтeльнo ввoдилиcь в пaмять и выпoлнялиcь oднa зa дpyгoй. Этo дeлaлocь aвтoмaтичecки c пoмoщью cиcтeмнoй yпpaвляющeй пpoгpaммы. Такую пpoгpaммy мoжнo нaзвaть пpocтeйшeй oпepaциoннoй cиcтeмoй. Пpи тaкoм peжимe пpoпycкнaя cпocoбнocть ЭBM yвeличилacь, нo peзyльтaт выпoлнeния пpoгpaмм пpиxoдилocь ждaть дocтaтoчнo дoлгo ( инoгдa нecкoлькo чacoв).

Дaльнeйшee paзвитиe aппapaтныx и пpoгpaммныx cpeдcтв ЭBM пpивeлo к пoявлeнию мyльтипpoгpaммиpoвaния

Дaльнeйшee paзвитиe aппapaтныx и пpoгpaммныx cpeдcтв ЭBM пpивeлo к пoявлeнию мyльтипpoгpaммиpoвaния

Cyщecтвyeт нecкoлькo мyльтипpoгapммныx peжимoв. Ocнoвныe из ниx:

- мyльтипpoгaммный пaкeтный peжим;

- peжим paздeлeния вpeмeни;

- peжим peaльнoгo вpeмeни.

Ведущие разработчики программ и устройств решили разработать пособие стандарта – спецификацию

Ведущие разработчики программ и устройств решили разработать пособие стандарта – спецификацию

Спецификация РС 2 001 делит компьютеры на следующие типы.

Consumer PC (пользовательский). Предназначен для работы вне локальной сети, но есть модем для подключения к Internet. Может использоваться как обучающий и игровой. Содержит графическую подсистему, поддерживающую солидные мультимедиа-приложения. Рекомендуется наличие Device Bay – устройства, позволяющего заменять периферию без вскрытия корпуса и перегрузки компьютера.

Office PC (офисный). Это сетевой компьютер, снабжённый сетевым адаптером для подключения в локальную сеть. Для него устанавливается минимальная общая цена владения.

Workstation PC (рабочая станция) – приспособлена для работы в сети, но превосходит по возможностям Office PC. Используется для решения задач, требующих интенсивных вычислений.

Entertainment PC (игровые или развлекательные). Требования подчинены их назначению. В них устанавливают устройства высокопроизводительной графики, аудиосистемы Hi-Fi, сравнимые по качеству с хорошим музыкальным центром. Обеспечивается расширенная поддержка подключения внешних устройств (видеомагнитофонов, цифровых видеокамер и пр.).

Mobile PC (мобильный). Основные цели, стоящие перед разработчиком – снижение веса и увеличение времени работы от батарей. Набор функциональных возможностей сопоставим с пользовательским компьютером.

В стандарте РС 2 001 подробно описаны требования к набору устройств компьютера и выполняемым функциям.

Есть требования обязательные, желательные и прочие. Сертификат на соответствие аппаратуры требованиям РС 2 001 выдаёт тестовый центр Microsoft. Сертификат называют WHQL (Windows Hardwear Quality Labs) по названию центра.

ПРОЦЕССОРЫ ШЕСТОГО ПОКОЛЕНИЯ

Существуют Pentium III с частотами 450, 500, 500 Е,

ПРОЦЕССОРЫ ШЕСТОГО ПОКОЛЕНИЯ

Существуют Pentium III с частотами 450, 500, 500 Е,

В первых моделях буква Е обозначала интегрированный L2-кэш типа «Advanced Transfer Cache», частота системной шины 133 МГц, а в последних моделях буквы Е и В не пишут. Но в процессоре все они учтены.

Эти процессоры имеют следующие характеристики.

Технология производства: 0,18 мкм (0,25 мкм для частоты 450 МГц), 28 миллионов транзисторов.

Ядро процессора Coppermine c SSE-конвейером (для частоты 450 МГц – Katmai на основе Deschutes, конвейер SSE с добавлением 70 новых SSE-инструкций).

L1-кэш: объём 32 Кбайт (16 Кбайт данных+16 Кбайт инструкций).

L2-кэш: объём 256 Кбайт (512 Кбайт для частоты 450 МГц), тактовая частота равна тактовой частоте ядра, интегрирован на одном кристалле с процессором (у модели с частотой 450 МГц – отдельно), поддерживает ECC-механизм обнаружения и коррекции ошибок при обмене данными с ядром процессора. Такой L1-L2 кэш называют «Advanced Transfer Cache».

Частота системной шины 100 или 133 МГц, поддерживается ECC.

Напряжение питания ядра процессора 1,65 В.

Поддерживается до двух процессоров на одной системной шине, кроме моделей в FC-PGA исполнении – там один процессор.

В Coppermine есть дополнительный VI слой разводки проводников. Расстояние между слоями

В Coppermine есть дополнительный VI слой разводки проводников. Расстояние между слоями

Athlon (K 7) с частотами 500, 550, 600, 650, 700 МГц

Athlon (K 7) с частотами 500, 550, 600, 650, 700 МГц

Pentium IV (Willamette) 1,5 ГГц.

В нём новое ядро, а также

Pentium IV (Willamette) 1,5 ГГц. В нём новое ядро, а также

Конвейерная обработка информации

Иногда лучше проводить конвейерную обработку информации. Она улучшает использование

Конвейерная обработка информации Иногда лучше проводить конвейерную обработку информации. Она улучшает использование

Векторная обработка информации

В векторных конвейерах создаётся множество функциональных элементов, каждый из

Векторная обработка информации В векторных конвейерах создаётся множество функциональных элементов, каждый из

Концепция потоковых ВС

Существуют трудности, связанные с решением проблемы автоматизации параллельного программирования,

Концепция потоковых ВС Существуют трудности, связанные с решением проблемы автоматизации параллельного программирования,

3.Пoнятиe пpoгpaммнoгo oбecпeчeния

Пpoгpaммнoe или мaтeмaтичecкoe oбecпeчeниe (в мaтeмaтичecкoй энциклoпeдии - этo

3.Пoнятиe пpoгpaммнoгo oбecпeчeния Пpoгpaммнoe или мaтeмaтичecкoe oбecпeчeниe (в мaтeмaтичecкoй энциклoпeдии - этo

Развіццё індустрыяльнай цывілізацыі

Развіццё індустрыяльнай цывілізацыі Воспитание координационных способностей у учащихся при выполнении метания на уроках физической культуры

Воспитание координационных способностей у учащихся при выполнении метания на уроках физической культуры Разработка проекта. Анализ

Разработка проекта. Анализ Презентация "Золото, его значение для экономики" - скачать презентации по Экономике

Презентация "Золото, его значение для экономики" - скачать презентации по Экономике Механические и строительные свойства и характеристики грунтов

Механические и строительные свойства и характеристики грунтов Белогорье в лицах. Социально ориентированный проект «Поколение NEXT. Добрые дела в подарок юбилею»

Белогорье в лицах. Социально ориентированный проект «Поколение NEXT. Добрые дела в подарок юбилею» Спорт во дворе. Социальный проект

Спорт во дворе. Социальный проект Банкротство

Банкротство  ЯБЖ Прометей

ЯБЖ Прометей Учитель ВК ГОУ СОШ № 604 Споданейко В.А.

Учитель ВК ГОУ СОШ № 604 Споданейко В.А. Реальная жизнь

Реальная жизнь Лингвистические особенности речи политических лидеров (на примере предвыборных речей Барака Обамы и Дональда Трампа)

Лингвистические особенности речи политических лидеров (на примере предвыборных речей Барака Обамы и Дональда Трампа) Подбор сечения сплошной колонны. Проект рабочей площадки промышленного здания

Подбор сечения сплошной колонны. Проект рабочей площадки промышленного здания Шпенглер Освальд и его политические идеи

Шпенглер Освальд и его политические идеи A quantum computer

A quantum computer Устройства компьютера

Устройства компьютера Технология, механизация, автоматизация железнодорожного строительства. Искусственные сооружения

Технология, механизация, автоматизация железнодорожного строительства. Искусственные сооружения 1.Предмет макроэкономики Макроэкономика –наука, которая изучает поведение экономики в целом или ее крупных совокупностей (агрег

1.Предмет макроэкономики Макроэкономика –наука, которая изучает поведение экономики в целом или ее крупных совокупностей (агрег Определение БД и банков данных (БнД). Компоненты банка данных

Определение БД и банков данных (БнД). Компоненты банка данных Банки. Банковская система Автор презентации: Гибадуллин Рим Рашитович учитель истории и обществознания I квалификационной ка

Банки. Банковская система Автор презентации: Гибадуллин Рим Рашитович учитель истории и обществознания I квалификационной ка Вадим ЧУВЕЛЁВ Директор по качеству, партнёр «Мирмекс» vchuvelev@myrmex.ru, @Vadim_C Внутренние коммуникации 2.0: веб-технологии для управления п

Вадим ЧУВЕЛЁВ Директор по качеству, партнёр «Мирмекс» vchuvelev@myrmex.ru, @Vadim_C Внутренние коммуникации 2.0: веб-технологии для управления п Пересмотр вступивших в законную силу приговоров

Пересмотр вступивших в законную силу приговоров  Все подвиги Геракл совершил на службе А) у Зевса Б) у Эврисфея В) у Алкмены

Все подвиги Геракл совершил на службе А) у Зевса Б) у Эврисфея В) у Алкмены Массивтер

Массивтер Структура языка C

Структура языка C Совершенствование технологии очистки сточных вод г. Слюдянка

Совершенствование технологии очистки сточных вод г. Слюдянка Инвертор инструкции Operating Instructions

Инвертор инструкции Operating Instructions Олимпийские игры в древней Греции: система обслуживания спортсменов и гостей

Олимпийские игры в древней Греции: система обслуживания спортсменов и гостей