Содержание

- 2. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 3. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 4. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 5. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 6. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 7. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 8. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 9. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 10. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 11. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 12. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 13. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 14. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 15. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 16. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 17. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 18. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 19. Используемая литература: Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices

- 20. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 22. Скачать презентацию

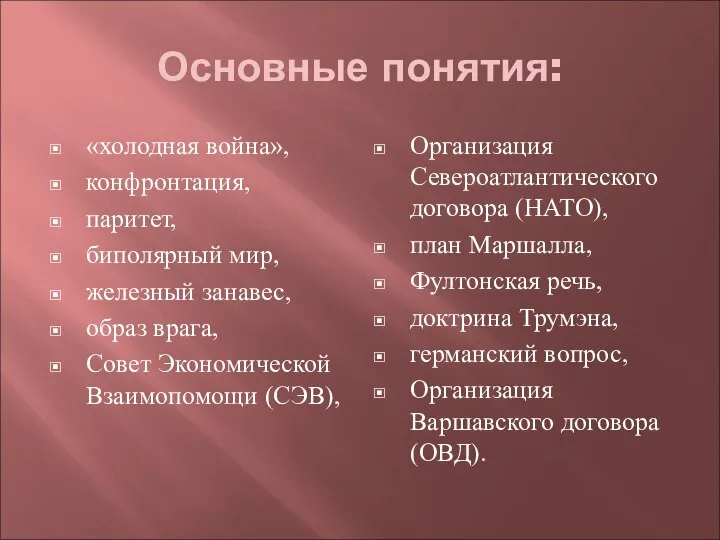

Основные возможности использования IKT в когнитивной таксономии

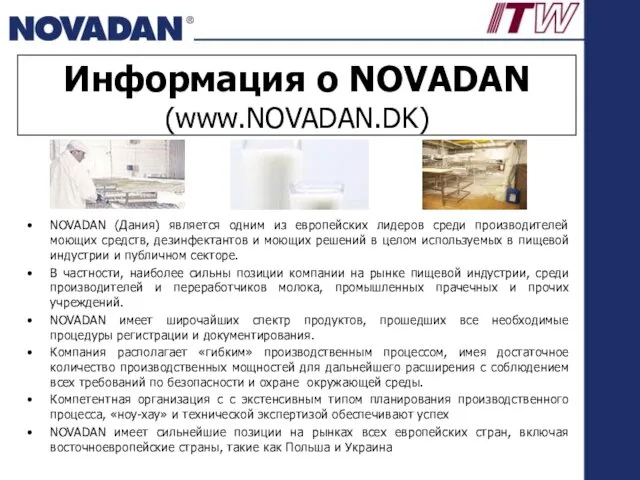

Основные возможности использования IKT в когнитивной таксономии Информация о NOVADAN (www.NOVADAN.DK) NOVADAN (Дания) является одним из европейских лидеров среди производителей моющих средств, дезинфектантов

Информация о NOVADAN (www.NOVADAN.DK) NOVADAN (Дания) является одним из европейских лидеров среди производителей моющих средств, дезинфектантов  Искусство и религия

Искусство и религия  Презентация Научные основания таможенной деятельности

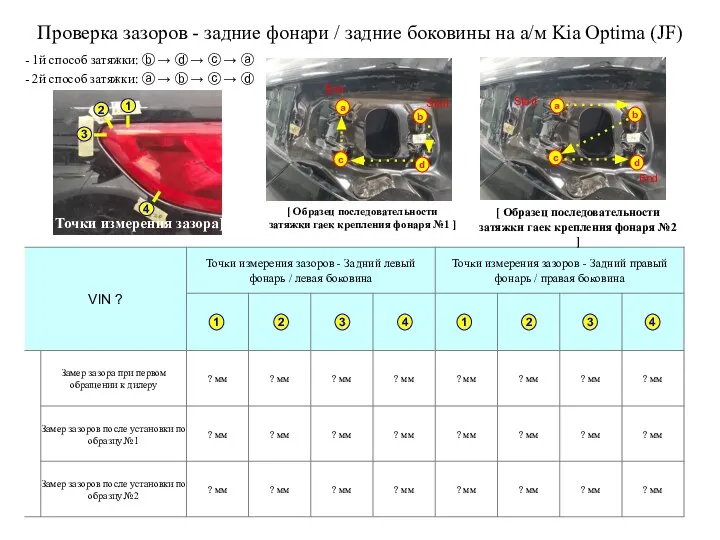

Презентация Научные основания таможенной деятельности Проверка зазоров - задние фонари / задние боковины на а/м Kia Optima (JF)

Проверка зазоров - задние фонари / задние боковины на а/м Kia Optima (JF) Межбюджетные отношения

Межбюджетные отношения  Саясаттану – саясат туралы ғылым және пән

Саясаттану – саясат туралы ғылым және пән Вирус папиллом

Вирус папиллом Психологические возрастные особенности подростка. Родительское собрание 7класс.

Психологические возрастные особенности подростка. Родительское собрание 7класс. Программирование на языке С

Программирование на языке С Туристическое снаряжение

Туристическое снаряжение Услуги по дооборудованию автомобиля UAZ Hunter

Услуги по дооборудованию автомобиля UAZ Hunter 1154555

1154555 Совершенствование работы склада за счет улучшения процесса взаимодействия между отделами

Совершенствование работы склада за счет улучшения процесса взаимодействия между отделами Political philosophy

Political philosophy Проект: Общественное пространство «Городская лаборатория «Затулинка» на левом берегу Новосибирска»

Проект: Общественное пространство «Городская лаборатория «Затулинка» на левом берегу Новосибирска» Надпочечниковая недостаточность

Надпочечниковая недостаточность ПРОБЛЕМЫ ПРЕЕМСТВЕННОСТИ ПРИ ПЕРЕХОДЕ ИЗ НАЧАЛЬНОЙ ШКОЛЫ В СРЕДНЕЕ ЗВЕНО.

ПРОБЛЕМЫ ПРЕЕМСТВЕННОСТИ ПРИ ПЕРЕХОДЕ ИЗ НАЧАЛЬНОЙ ШКОЛЫ В СРЕДНЕЕ ЗВЕНО. Медицина в XVIII веке в России. Организация ухода за больными и ранеными

Медицина в XVIII веке в России. Организация ухода за больными и ранеными Самооптимизирующееся производство. Искусственный интеллект. Ожидания и актуальное состояние

Самооптимизирующееся производство. Искусственный интеллект. Ожидания и актуальное состояние Рулевое управление

Рулевое управление Устройство компьютера

Устройство компьютера Пиратство в интернете

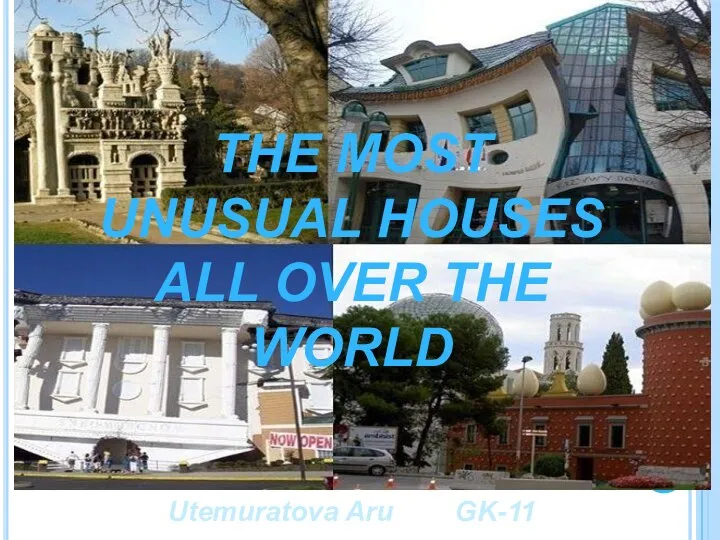

Пиратство в интернете The most unusual houses all over the world

The most unusual houses all over the world Дальномер

Дальномер ATA — параллельный интерфейс подключения накопителей к компьютеру

ATA — параллельный интерфейс подключения накопителей к компьютеру Значение, строение, функционирование нервной системы.

Значение, строение, функционирование нервной системы.  Трансформаторы

Трансформаторы