Содержание

- 2. Рассматриваются два самых крупных производителя микропроцессоров Intel Corporation Advanced Micro Devices, Inc.

- 3. Микроархитектура Intel Core В основе лежит философия экономного использования электроэнергии; Микроархитектура Intel Core включает следующие инновации:

- 4. Ядро Conroe

- 5. Conroe — 65 нм технологический процесс Микропроцессор для настольных систем с поддержкой симметричной многопроцессорности (SMP), ограниченной

- 6. Ядро Kentsfield

- 7. Kentsfield — 65 нм технологический процесс Микропроцессор для настольных систем с четырьмя ядрами (Quad Core) с

- 8. Микроархитектуры ближайших лет Процессоры для настольных ПК нового поколения с рабочим названием Penryn будут построены на

- 9. Penryn Усовершенствования, которые принесет переход на новый техпроцесс, интересно рассмотреть с позиций количественного сравнения. Например, четырехъядерные

- 10. Механизм Wide Dynamic Execution обеспечивает выполнение большего числа команд за один тактовый цикл, что увеличивает производительность

- 11. Две новые технологии: Deep Power Down Technology и Enhanced Dynamic Acceleration Technology. Технология Deep Power Down

- 12. Микроархитектура Nehalem Микроархитектура Nehalem будет поддерживать технологию Simultaneous Multi-Treading (SMT), которая фактически является возрождением знаменитой Hyper-Threading

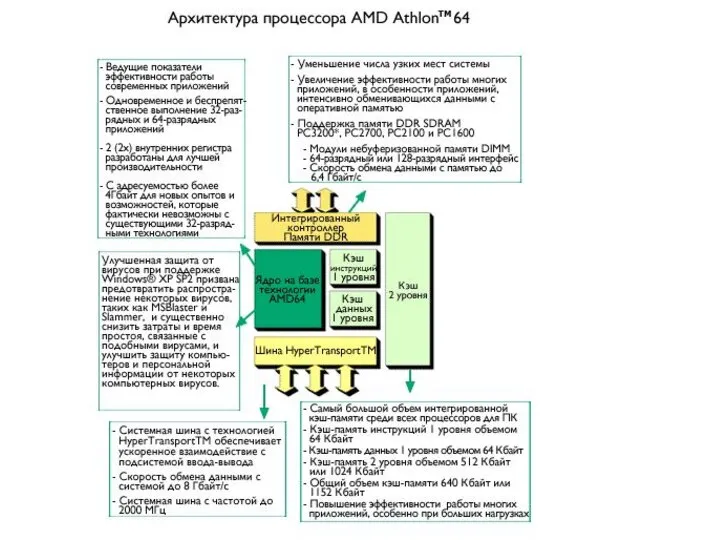

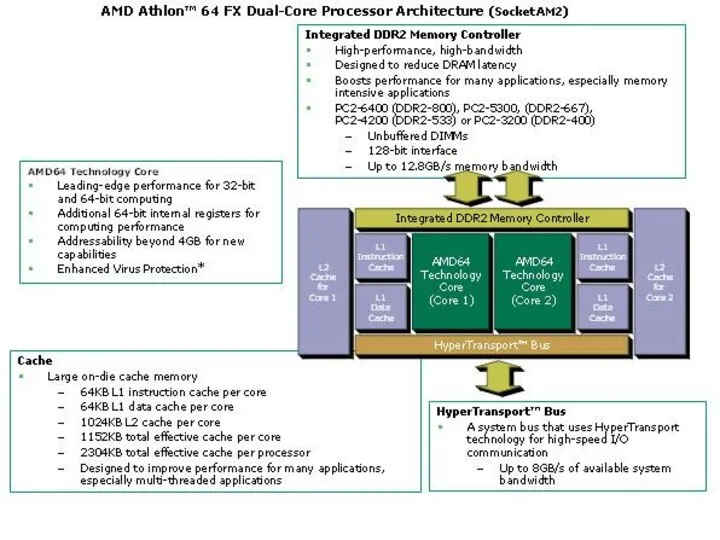

- 13. Микроархитектура K8 K8 — x86 совместимая микроархитектура центрального процессора разработанная корпорацией AMD. Впервые представленна 22 апреля

- 17. Скачать презентацию

Рассматриваются два самых крупных производителя микропроцессоров

Intel Corporation

Advanced Micro Devices, Inc.

Рассматриваются два самых крупных производителя микропроцессоров

Intel Corporation

Advanced Micro Devices, Inc.

Микроархитектура Intel Core

В основе лежит философия экономного использования электроэнергии;

Микроархитектура Intel Core

Микроархитектура Intel Core

В основе лежит философия экономного использования электроэнергии;

Микроархитектура Intel Core

Intel Wide Dynamic Execution - технология выполнения большего количества команд за каждый такт, повышающая эффективность выполнения приложений и сокращающая энергопотребление. Каждое ядро процессора может выполнять до четырех инструкций одновременно с помощью 14-стадийного конвейера

Intel Intelligent Power Capability - технология, с помощью которой для исполнения задач активируется работа отдельных узлов чипа по мере необходимости, что значительно снижает энергопотребление системы в целом

Intel Advanced Smart Cache - технология использования общей для всех ядер кэш-памяти L2, что снижает общее энергопотребление и повышает производительность, при этом, по мере необходимости, одно из ядер процессора может использовать весь объём кэш-памяти при динамическом отключении другого ядра

Intel Smart Memory Access - технология оптимизации работы подсистемы памяти, сокращающая время отклика и повышающая пропускную способность подсистемы памяти

Intel Advanced Digital Media Boost - технология обработки 128-разрядных команд SSE, SSE2 и SSE3, широко используемых в мультимедийных и графических приложениях, за один такт

Ядро Conroe

Ядро Conroe

Conroe — 65 нм технологический процесс

Микропроцессор для настольных систем

Conroe — 65 нм технологический процесс

Микропроцессор для настольных систем

Представлен: 27 июля 2006 года

Поддержка инструкций SIMD: SSE4

Количество транзисторов:

291 миллион у моделей с 4 МБ кэш-памяти

167 миллионов у моделей с 2 МБ кэш-памяти

Реализованы технологии:

Intel Virtualization Technology — поддержка нескольких операционных систем на одном компьютере (кроме моделей Core 2 Duo E4x00)

LaGrande Technology — enhanced security hardware extensions

Execute Disable Bit

EIST (Enhanced Intel SpeedStep Technology)

iAMT2 (Intel Active Management Technology) — удаленное управление компьютерами

Сокет: LGA775

Варианты:

Core 2 Duo E6850 — 3,00 ГГц (Кэш L2 размером 4 Мб, 1333 MHz FSB)

Core 2 Duo E6800 — 2,93 ГГц (Кэш L2 размером 4 Мб, 1066 МГц FSB)

Core 2 Duo E6750 — 2,67 ГГц (Кэш L2 размером 4 Мб, 1333 MHz FSB)

Core 2 Duo E6700 — 2,67 ГГц (Кэш L2 размером 4 Мб, 1066 МГц FSB)

Core 2 Duo E6650 — 2,33 ГГц (Кэш L2 размером 4 Мб, 1333 MHz FSB)

Core 2 Duo E6600 — 2,40 ГГц (Кэш L2 размером 4 Мб, 1066 МГц FSB)

Core 2 Duo E6420 — 2,13 ГГц (Кэш L2 размером 4 Мб, 1066 МГц FSB)

Core 2 Duo E6400 — 2,13 ГГц (Кэш L2 размером 2 Мб, 1066 МГц FSB)

Core 2 Duo E6320 — 1,86 ГГц (Кэш L2 размером 4 Мб, 1066 МГц FSB)

Core 2 Duo E6300 — 1,86 ГГц (Кэш L2 размером 2 Мб, 1066 МГц FSB)

Core 2 Duo E4500 — 2,20 ГГц (Кэш L2 размером 2 Мб, 800 MHz FSB, нет VT)

Core 2 Duo E4400 — 2,00 ГГц (Кэш L2 размером 2 Мб, 800 МГц FSB, нет VT)

Core 2 Duo E4300 — 1,80 ГГц (Кэш L2 размером 2 Мб, 800 МГц FSB, нет VT)

Core 2 Duo E4200 — 1,60 ГГц (Кэш L2 размером 2 Мб, 800 МГц FSB, нет VT)

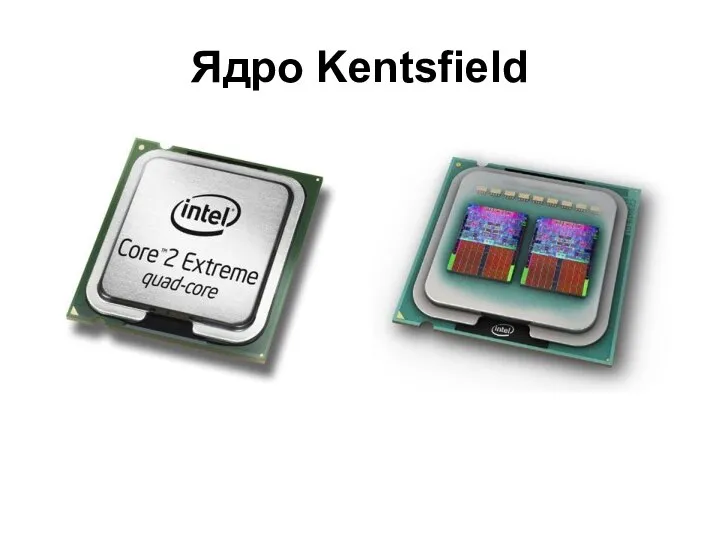

Ядро Kentsfield

Ядро Kentsfield

Kentsfield — 65 нм технологический процесс

Микропроцессор для настольных систем

Kentsfield — 65 нм технологический процесс

Микропроцессор для настольных систем

Представлен: 13 декабря 2006 года

Реализованы те же технологии, что и у микропроцессора Conroe, но в отличие от него имеет 4 ядра

Сокет: Socket 775

Варианты:

Core 2 Extreme QX6850 — 3,00 ГГц (Кэш L2 размером 2x4 Мб, 1333 МГц FSB) (16 июля 2007 года)

Core 2 Extreme QX6800 — 2,93 ГГц (Кэш L2 размером 2x4 Мб, 1066 МГц FSB) (9 апреля 2007 года)

Core 2 Extreme QX6700 — 2,66 ГГц (Кэш L2 размером 2x4 Мб, 1066 МГц FSB) (4 ноября 2006 года)

Core 2 Quad Q6700 — 2,66 ГГц (Кэш L2 размером 2x4 Мб, 1066 МГц FSB) (16 июля 2007 года)

Core 2 Quad Q6600 — 2,40 ГГц (Кэш L2 размером 2x4 Мб, 1066 МГц FSB) (7 января 2007 года)

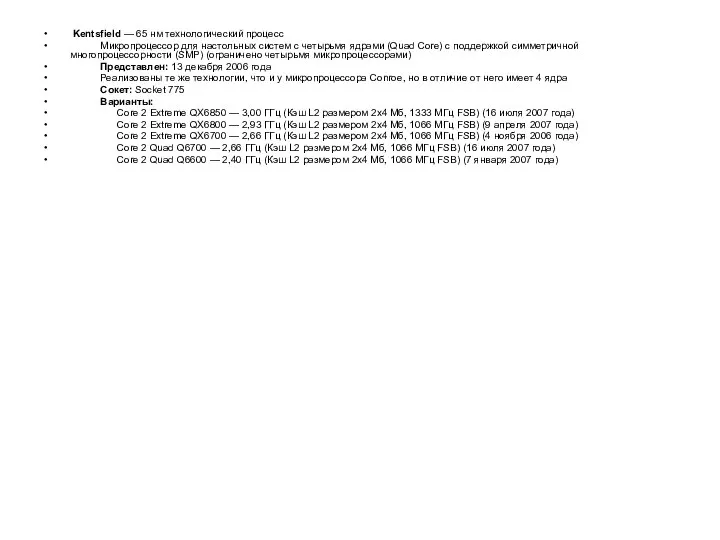

Микроархитектуры ближайших лет

Процессоры для настольных ПК нового поколения с рабочим названием

Микроархитектуры ближайших лет

Процессоры для настольных ПК нового поколения с рабочим названием

После наладки массового производства чипов Penryn, Intel планирует представить процессоры Nehalem с новой одноименной микроархитектурой - на смену Intel Core. Примерно через два-три года после анонса 45-нм процессоров – ориентировочно, ближе к 2009-2010, Intel надеется представить новый, более прецизионный 32-нм техпроцесс.

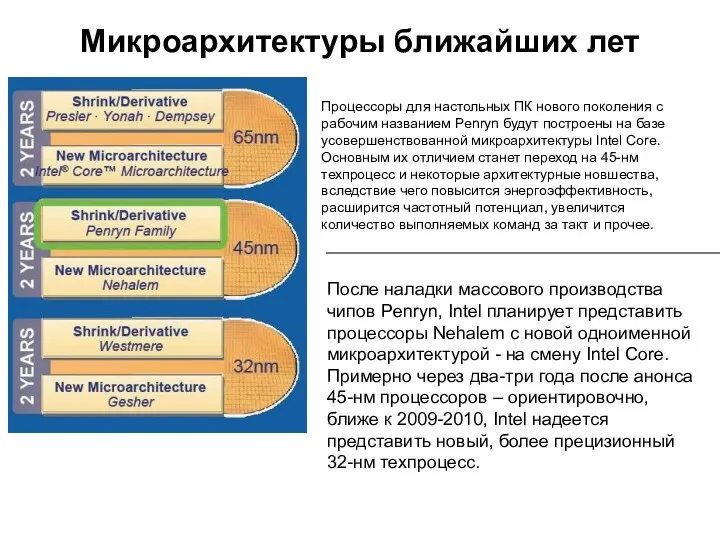

Penryn

Усовершенствования, которые принесет переход на новый техпроцесс, интересно рассмотреть с

Penryn

Усовершенствования, которые принесет переход на новый техпроцесс, интересно рассмотреть с

Новшества, которые принесет следующее поколение процессоров, можно рассматривать по отношению к пяти современным технологиям Intel: Wide Dynamic Execution, Advanced Smart Cache, Smart Memory Access, Advanced Digital Media Boost, Intelligent Power Capability.

Механизм Wide Dynamic Execution обеспечивает выполнение большего числа команд за один

Механизм Wide Dynamic Execution обеспечивает выполнение большего числа команд за один

Технология Advanced Smart Cache нацелена на обеспечение более высокой производительности и эффективности кэш-памяти. В процессорах семейства Penryn компания Intel решила увеличить объем кэша. Так, двухъядерные процессоры будут оснащаться кэшем L2 емкостью до 6 Мб, а отдельные четырехъядерные модели обзаведутся 12-Мб кэш-памятью. О частотных характеристиках пока говорится в ключе преодоления планки 3 ГГц.

В рамках технологии Smart Memory Access говорится об увеличении пропускной способности шины. Подтверждается информация об освоении шины FSB 1600 МГц. Сообщается, что шина FSB 1600 МГц появится в некоторых моделях процессоров для серверов и рабочих станций; когда будут выпущены модели с высокоскоростной шиной для настольных ПК, пока не уточняется.

Технология Advanced Digital Media Boost применяется для ускорения обработки видео, изображения и речевых потоков. Для повышения производительности при обработке медиаданных Intel решила добавить к архитектуре ISA набор расширений SSE4 (Streaming SIMD Extensions 4), который станет доступным для большинства массовых секторов рынка ПК с появлением 45-нм процессоров. Этот новый набор команд включает множество инновационных инструкций (их насчитывается около 50), которые условно можно разделить на две группы:

Примитивы векторизации для компиляторов и ускорители мультимедийных приложений;

Ускорители обработки строк и текстовой информации.

Еще одним усовершенствованием является механизм перестановок - Super Shuffle Engine. Новый блок умеет выполнять перестановки значений сразу во всем 128-разрядном регистре за один такт. Это существенно повышает производительность при обработке операций, связанных с перестановкой (упаковка, распаковка, сдвиг упакованных значений, вставка). Сравнение количества тактов, нужных для выполнения базовых операций SSE, приведено на диаграмме. В среднем наблюдается двукратное увеличение производительности.

Две новые технологии: Deep Power Down Technology и Enhanced Dynamic Acceleration

Две новые технологии: Deep Power Down Technology и Enhanced Dynamic Acceleration

Технология Deep Power Down Technology будет внедрена, в первую очередь, в процессоры для мобильных платформ (Mobile Penryn). Для понижения энергопотребления в режиме бездействия добавлено еще одно особое состояние процессора, именуемое как Deep Power Down Technology State, или C6. В этом режиме предусмотрено отключение ядер, при этом также полностью отключается кэш-память. Это позволяет существенно понизить напряжение ядра и потребляемой мощности, что, в свою очередь, увеличивает время работы батареи.

Интересным нововведением является технология Enhanced Dynamic Acceleration Technology (EDAT). Её идея состоит в следующем. Для простоты возьмем случай с двухъядерным процессором. Поскольку в однопоточных приложениях от многоядерности толку мало, основную роль здесь играет производительность отдельно взятого ядра. Поэтому Intel предусмотрела увеличение частоты работающего ядра (non-idle core), в то время как второе (idle core) находится в одном из состояний бездействия (C3-C6) и его тепловыделение резко сокращается. Эту разницу использует работающее ядро и повышает свою частоту до достижения процессором граничного уровня TDP. Для наглядности приводим следующую иллюстрацию.

Микроархитектура Nehalem

Микроархитектура Nehalem будет поддерживать технологию Simultaneous Multi-Treading (SMT), которая

Микроархитектура Nehalem

Микроархитектура Nehalem будет поддерживать технологию Simultaneous Multi-Treading (SMT), которая

В новых процессорах планируется использовать концепцию многоуровневого разделяемого кэша. При этом отмечают, что разделяемым будет только кэш высшего уровня. Также упоминается о технологии Enhanced Dynamic Power Management, связанной с улучшениями показателя «производительность на ватт», хотя подробных сведений о ней пока нет.

Из уст представителей Intel прозвучала информация о планах внедрения в CPU интегрированного контроллера памяти (IMC). Пока не уточняется, какие типы памяти будут поддерживаться IMC, но с учетом времени появления процессоров Nehalem (вторая половина 2008 года) логично предположить о поддержке DDR3. Говорится о замене FSB последовательной скоростной шиной типа Serial Point-to-point Interconnect (вероятнее всего, речь идет о CSI, Common Systems Interconnect). Подтверждается информация о намерении представить модели со встроенным GPU. Впрочем, все выше приведенные сведения вряд ли можно назвать неожиданными, важно было найти подтверждение слухов и догадок на официальном уровне.

По слухам, на базе чипов с микроархитектурой Nehalem будут представлены платформы, известные под кодовыми именами Stoutland и Thurley. В платформе Stoutland предусмотрена передача данных по шине CSI со скоростью от 4,8 до 6,4 гигатранзакций в секунду. В рамках этой платформы упоминается чипсет Boxboro с 72 линиями шины PCI Express 2.0. Платформа Thurley будет поддерживать 42 линии шины PCI Express. В систему можно будет установить до 96 Гб системной памяти. Сетевые возможности будут определяться Ethernet-контроллером с пропускной способностью 10 Гбит/с.

Микроархитектура K8

K8 — x86 совместимая микроархитектура центрального процессора разработанная корпорацией

Микроархитектура K8

K8 — x86 совместимая микроархитектура центрального процессора разработанная корпорацией

Микропроцессоры K8 являются суперскалярными, мультиконвеерными процессорами с предсказанием ветвлений и спекулятивным исполнением. Как и процессоры AMD K7 и Intel P6 они теоретически способны исполнять до 3-х инструкций за один такт. Как и любой современный x86 процессор K8 вначале перекодирует внешний сложный CISC набор x86 инструкций во внутренние RISC-подобные микрооперации, которые в свою очередь уже идут на исполнение. Для повышения производительности в рамках микроархитектуры реализовано спекулятивное исполнение с предсказанием ветвлений и Out-of-Order запуском микроопераций, для снижения влияния зависимостей по данным используются техники переименования регистров, Result forwarding и ряд других.

Culture оf Italy

Culture оf Italy Стратегический анализ внутренней и внешней среды организации

Стратегический анализ внутренней и внешней среды организации Sintec масла 1л 01.09-31.10

Sintec масла 1л 01.09-31.10 Петля КМПЦ

Петля КМПЦ London Parks

London Parks Презентация на тему "Правила поведения для малышей . Правила поведения в обществе" - скачать презентации по Педагогике

Презентация на тему "Правила поведения для малышей . Правила поведения в обществе" - скачать презентации по Педагогике Алгоритмы и структуры данных. Сортировка.Тема 07

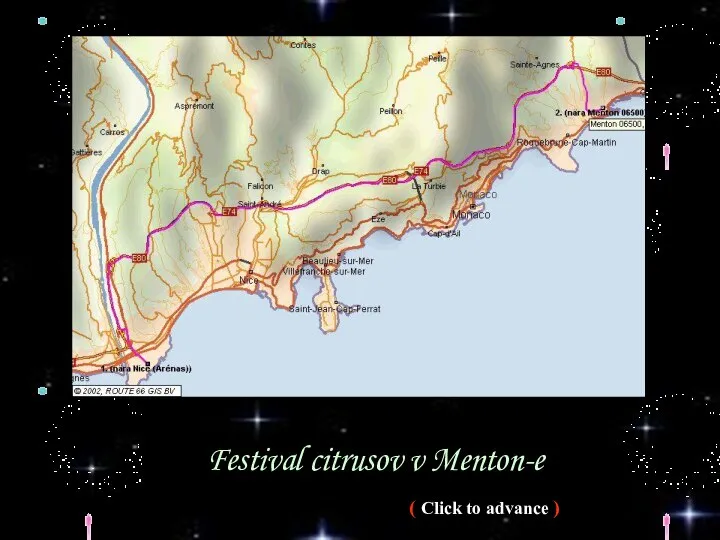

Алгоритмы и структуры данных. Сортировка.Тема 07 Citrus Festival a Methone

Citrus Festival a Methone Развитие спорта в Ростовской области

Развитие спорта в Ростовской области Moskau

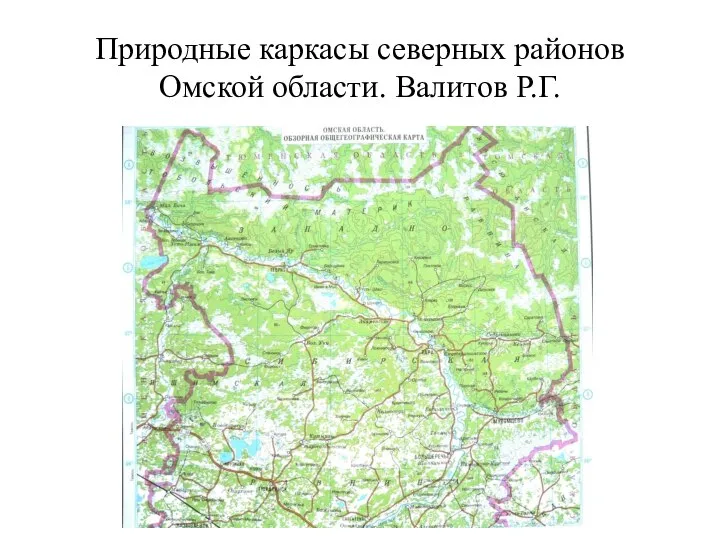

Moskau Природные каркасы северных районов ОО

Природные каркасы северных районов ОО Кафедра «Финансы и налоги» Преподаватель: Просалова Вероника Сергеевна, к.э.н., доцент «БЮДЖЕТНОЕ ПЛАНИРОВАНИЕ И ПРОЛНОЗИРОВА

Кафедра «Финансы и налоги» Преподаватель: Просалова Вероника Сергеевна, к.э.н., доцент «БЮДЖЕТНОЕ ПЛАНИРОВАНИЕ И ПРОЛНОЗИРОВА Доклад на тему «Механизм разработки и установления вывозных таможенных пошлин» Подготовили: студентки 3-го курса ФТД, группы Т

Доклад на тему «Механизм разработки и установления вывозных таможенных пошлин» Подготовили: студентки 3-го курса ФТД, группы Т Архитектурно-дизайнерское проектирование. (Проект 1. Тема 1)

Архитектурно-дизайнерское проектирование. (Проект 1. Тема 1) Тема 9. Организация маркетинговой деятельности на предприятии и управление маркетингом. Маркетинг как концепция и функция бизне

Тема 9. Организация маркетинговой деятельности на предприятии и управление маркетингом. Маркетинг как концепция и функция бизне Патофизиология почек

Патофизиология почек Автомат для зарядки гаджетов

Автомат для зарядки гаджетов Тема урока «Нарушение осанки и плоскостопие»

Тема урока «Нарушение осанки и плоскостопие»  Патология твердых тканей зубов кариозного и некариозного происхождения

Патология твердых тканей зубов кариозного и некариозного происхождения Презентация Российская Федерация как социальное государство

Презентация Российская Федерация как социальное государство Технологическая культура

Технологическая культура Аппаратно-Компьютерные медицинские системы

Аппаратно-Компьютерные медицинские системы . АООП АОП

. АООП АОП Моделі життєвого циклу програмних систем

Моделі життєвого циклу програмних систем Проект по продвижению комплекса ГТО

Проект по продвижению комплекса ГТО Представление символьной информации. ASCII

Представление символьной информации. ASCII ПРЕЗЕНТАЦИЯ Теория развития цивилизаций А.Тойнби.

ПРЕЗЕНТАЦИЯ Теория развития цивилизаций А.Тойнби. Презентация XVIII столетие-начало новой эры в истории России.

Презентация XVIII столетие-начало новой эры в истории России.