Содержание

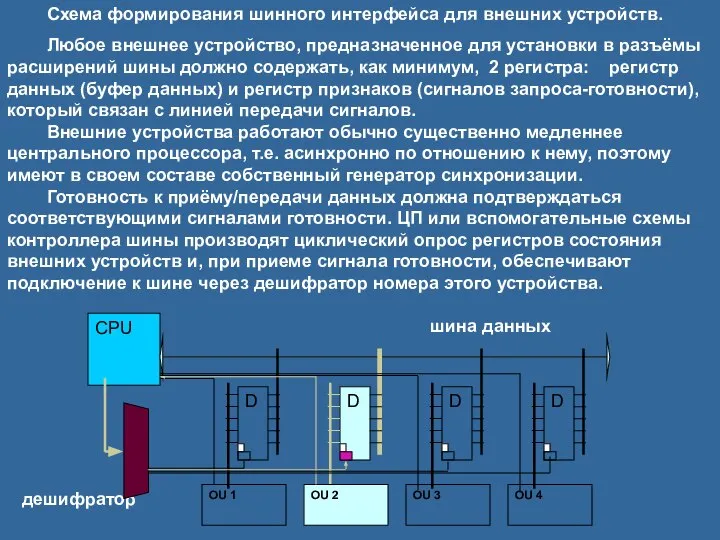

- 2. Схема формирования шинного интерфейса для внешних устройств. Любое внешнее устройство, предназначенное для установки в разъёмы расширений

- 3. Пояснения к шинной архитектуре ПЭВМ Контроллер шины является устройством, связывающим центральный процессор с периферийными устройствами по

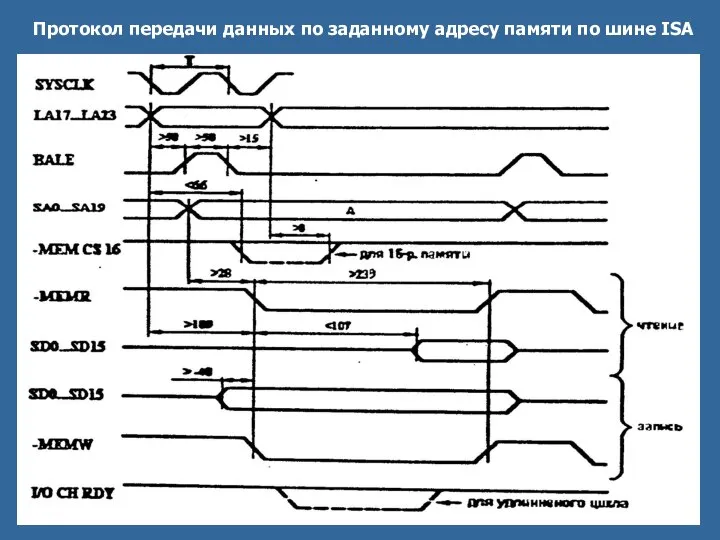

- 4. Протокол передачи данных по заданному адресу памяти по шине ISA

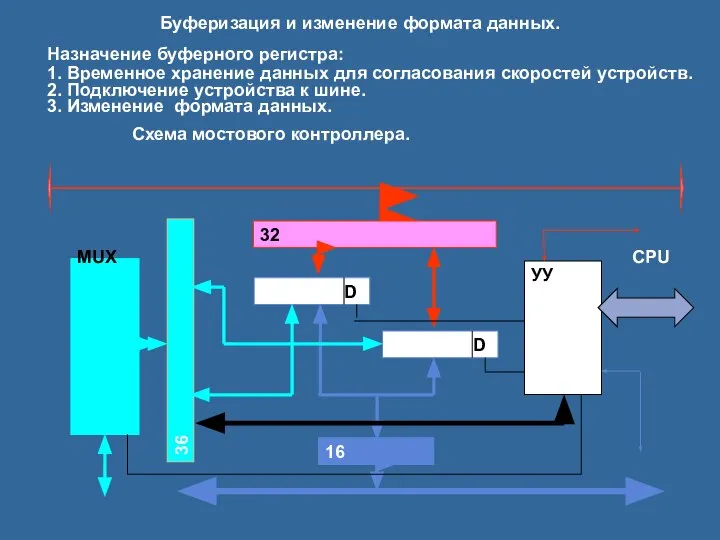

- 5. УУ Буферизация и изменение формата данных. Назначение буферного регистра: 1. Временное хранение данных для согласования скоростей

- 6. Схема наследуемой шинной архитектуры на базе шины ISA ЦП ОЗУ Контроллер клавиатуры клавиатура Контроллер ISA LPT1

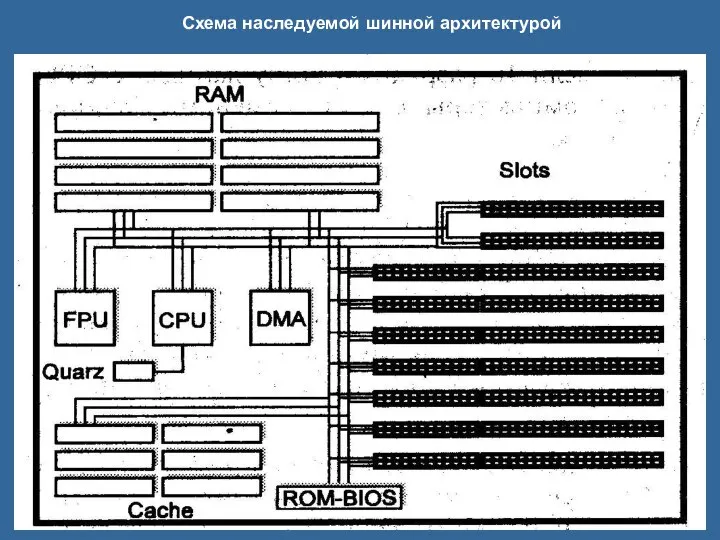

- 7. Схема наследуемой шинной архитектурой

- 8. Внешний вид системной платы с наследуемой шинной архитектурой

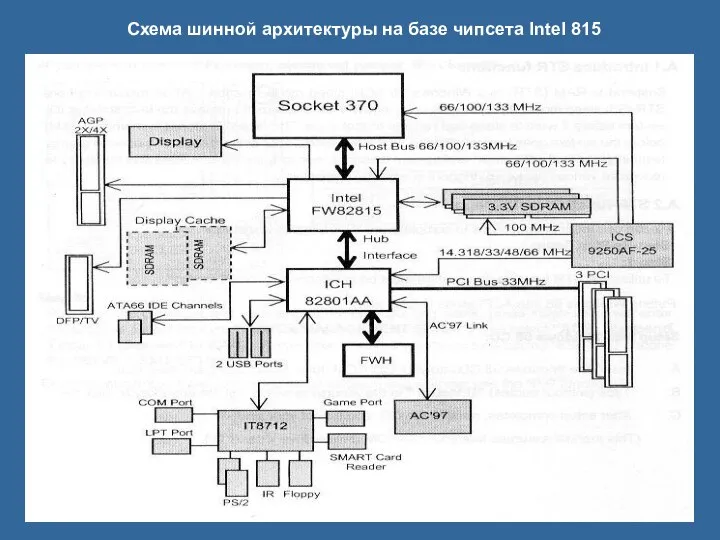

- 9. Схема шинной архитектуры на базе чипсета Intel 815

- 10. Внешний вид системной платы с шинной архитектуры Intel 815

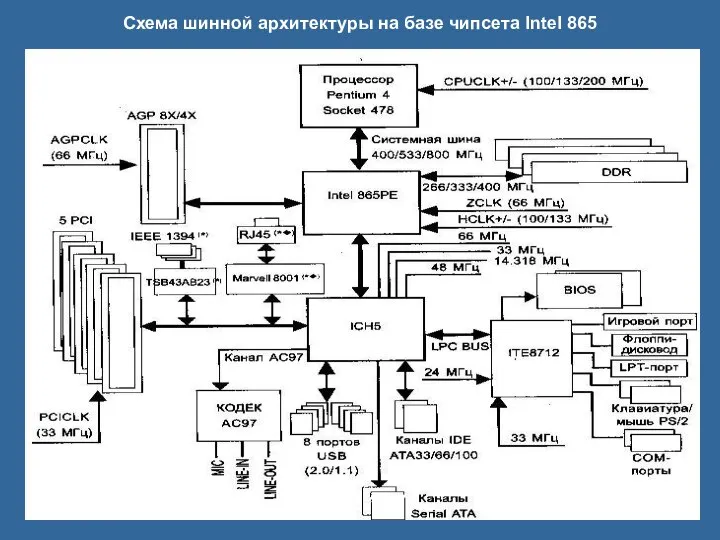

- 11. Схема шинной архитектуры на базе чипсета Intel 865

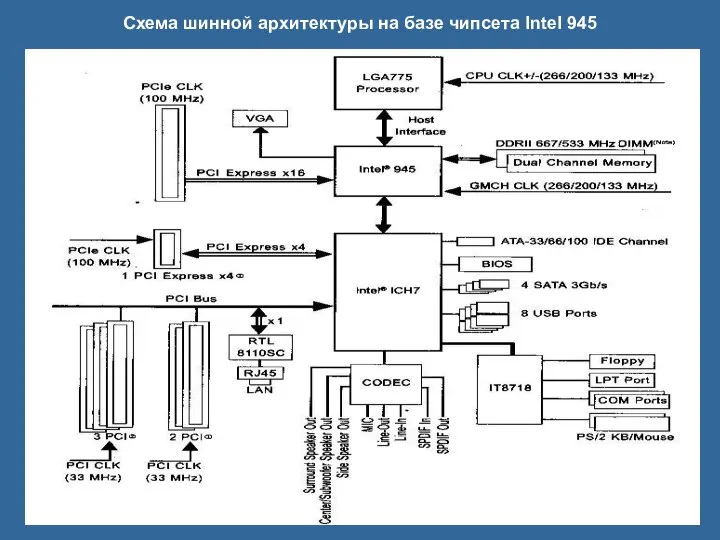

- 12. Схема шинной архитектуры на базе чипсета Intel 945

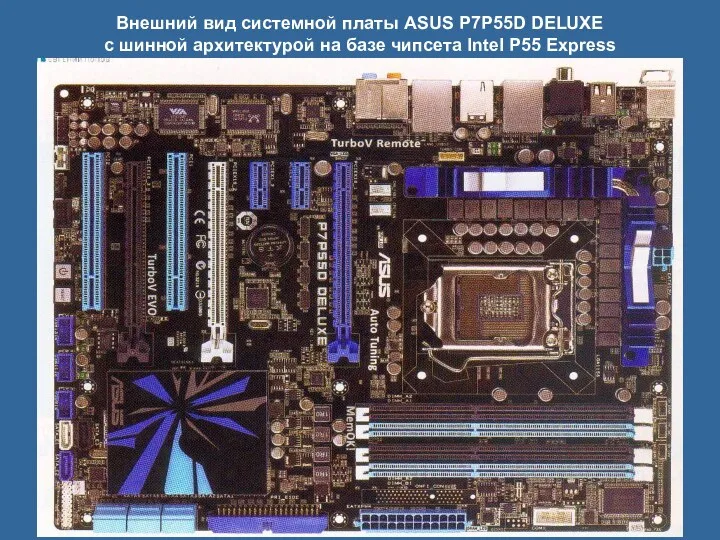

- 13. Внешний вид системной платы ASUS P7P55D DELUXE с шинной архитектурой на базе чипсета Intel P55 Express

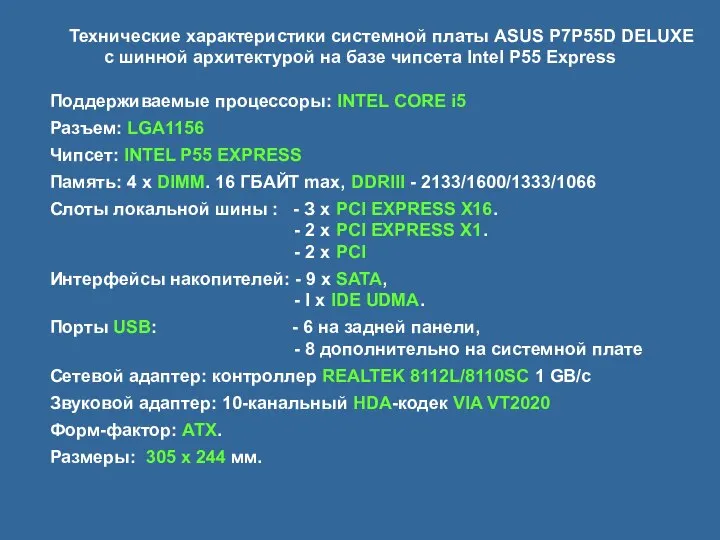

- 14. Технические характеристики системной платы ASUS P7P55D DELUXE с шинной архитектурой на базе чипсета Intel P55 Express

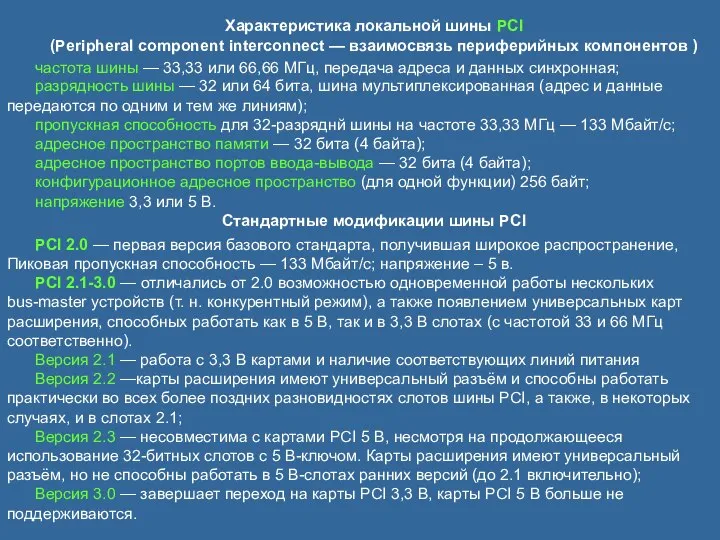

- 15. Характеристика локальной шины PCI (Peripheral component interconnect — взаимосвязь периферийных компонентов ) частота шины — 33,33

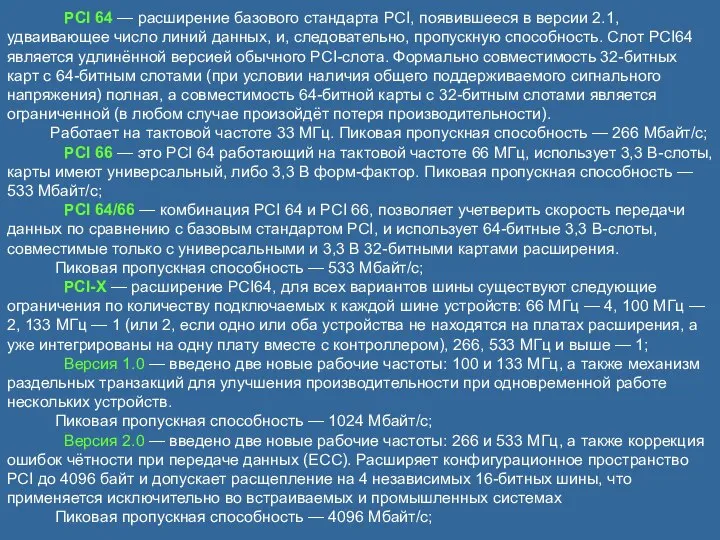

- 16. PCI 64 — расширение базового стандарта PCI, появившееся в версии 2.1, удваивающее число линий данных, и,

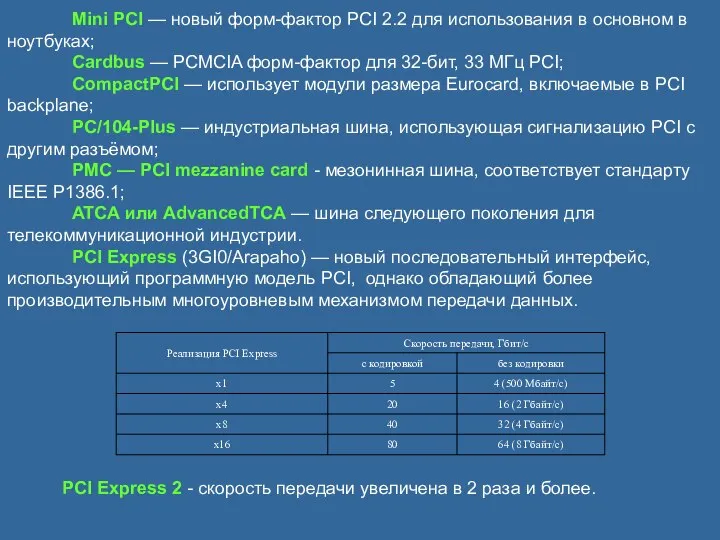

- 17. Mini PCI — новый форм-фактор PCI 2.2 для использования в основном в ноутбуках; Cardbus — PCMCIA

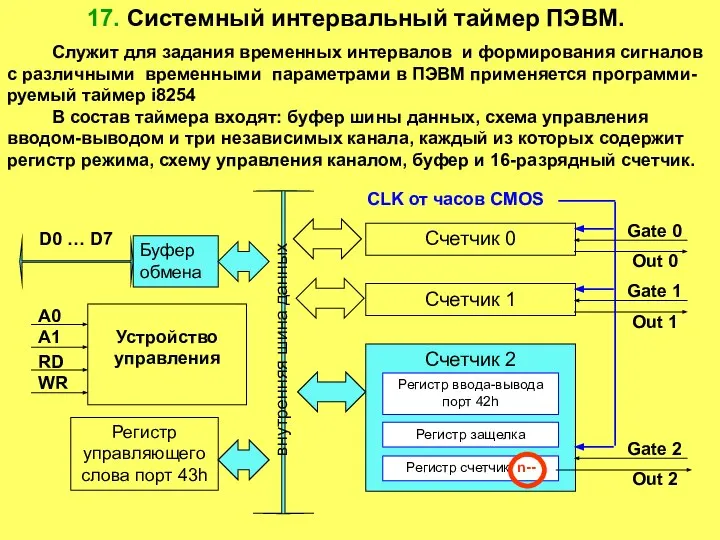

- 18. Счетчик 2 17. Системный интервальный таймер ПЭВМ. Служит для задания временных интервалов и формирования сигналов с

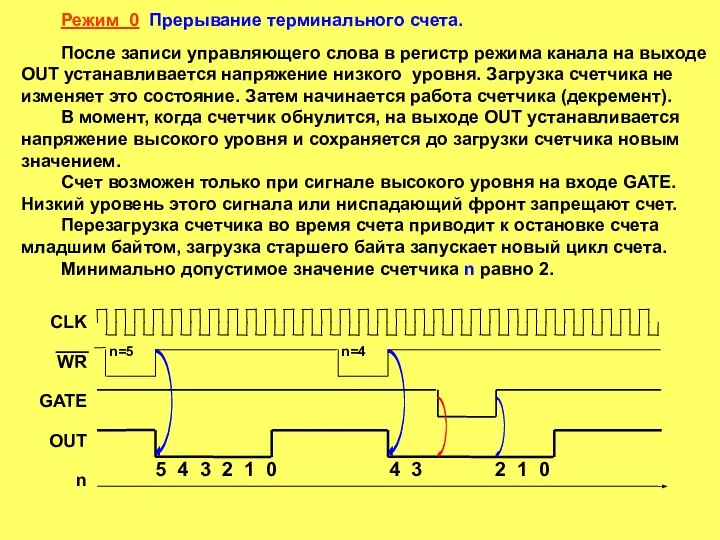

- 19. Режим 0 Прерывание терминального счета. После записи управляющего слова в регистр режима канала на выходе ОUT

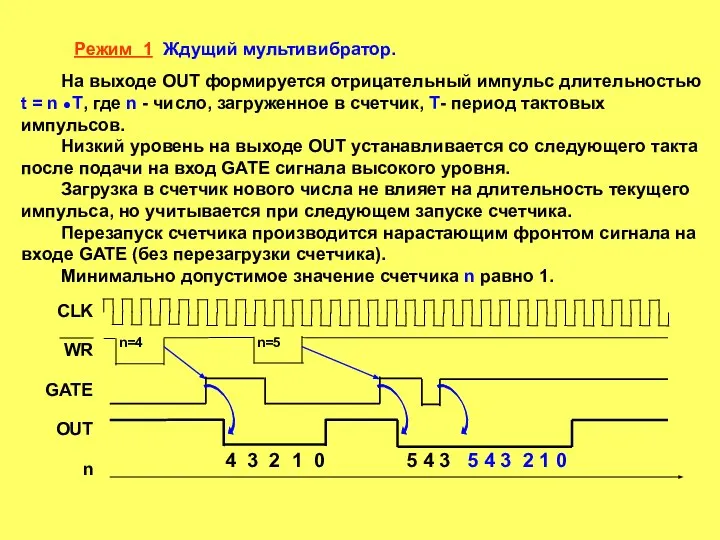

- 20. Режим 1 Ждущий мультивибратор. На выходе OUT формируется отрицательный импульс длительностью t = n ●T, где

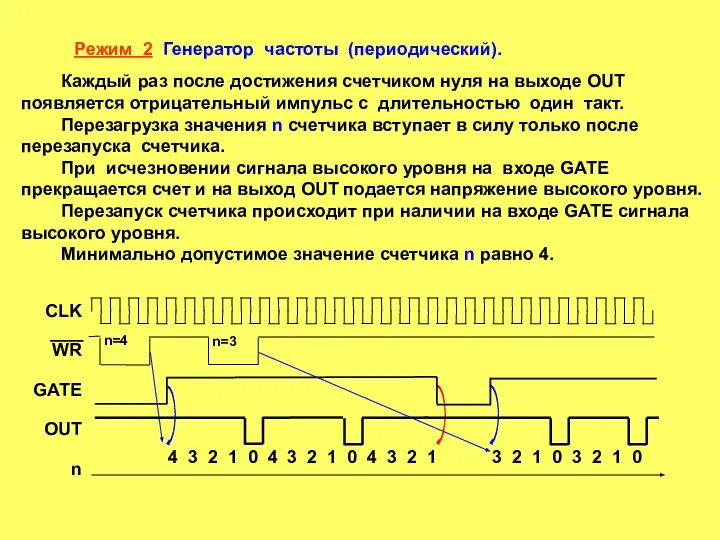

- 21. Режим 2 Генератор частоты (периодический). Каждый раз после достижения счетчиком нуля на выходе OUT появляется отрицательный

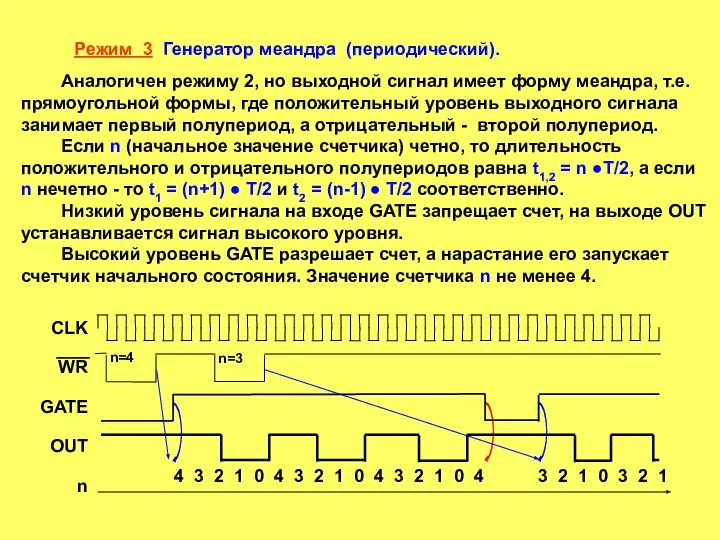

- 22. Режим 3 Генератор меандра (периодический). Аналогичен режиму 2, но выходной сигнал имеет форму меандра, т.е. прямоугольной

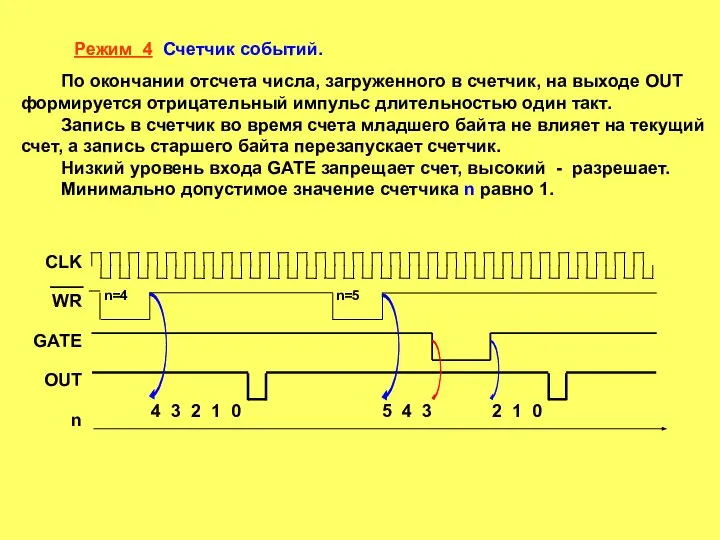

- 23. Режим 4 Счетчик событий. По окончании отсчета числа, загруженного в счетчик, на выходе OUT формируется отрицательный

- 24. Режим 5 Счетчик событий с автозагрузкой. Отличие от режима 4 состоит в том, что каждое нарастание

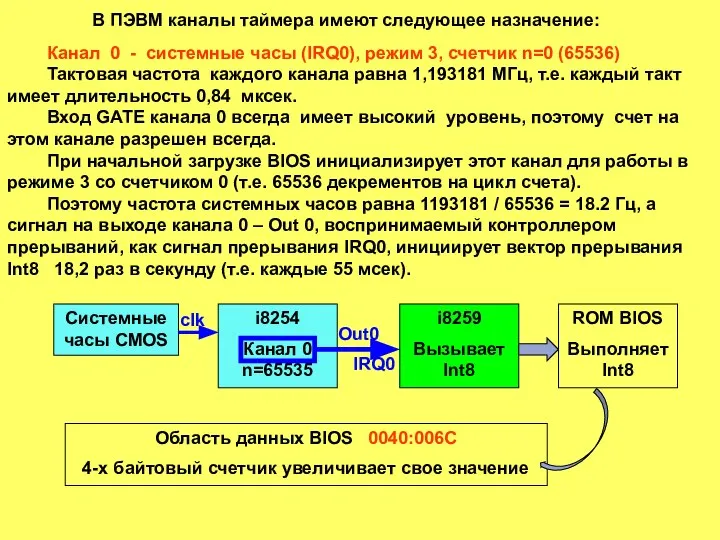

- 25. В ПЭВМ каналы таймера имеют следующее назначение: Канал 0 - системные часы (IRQ0), режим 3, счетчик

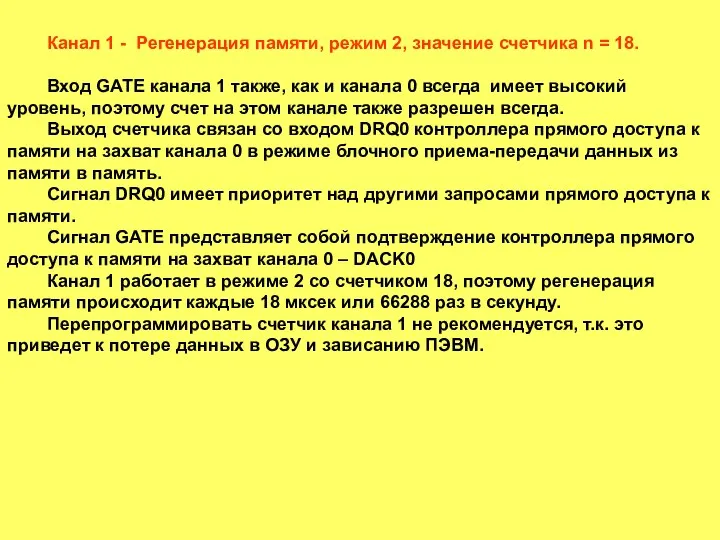

- 26. Канал 1 - Регенерация памяти, режим 2, значение счетчика n = 18. Вход GATE канала 1

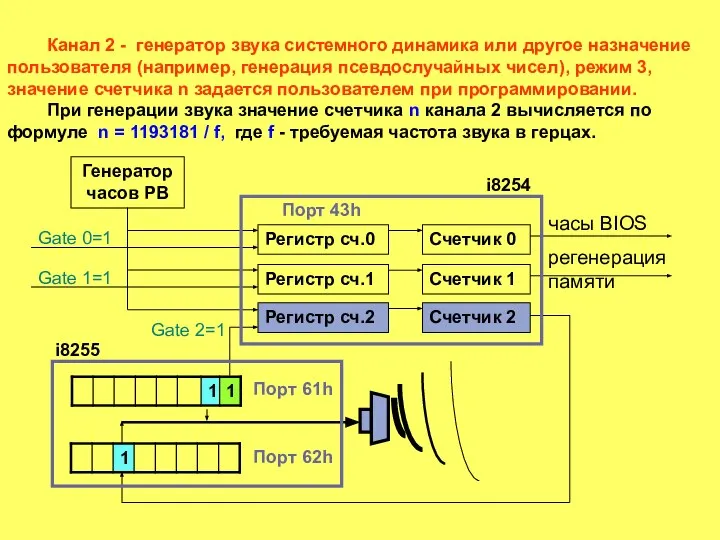

- 27. Генератор часов РВ Регистр сч.0 Счетчик 0 Регистр сч.1 Счетчик 1 Регистр сч.2 Счетчик 2 Gate

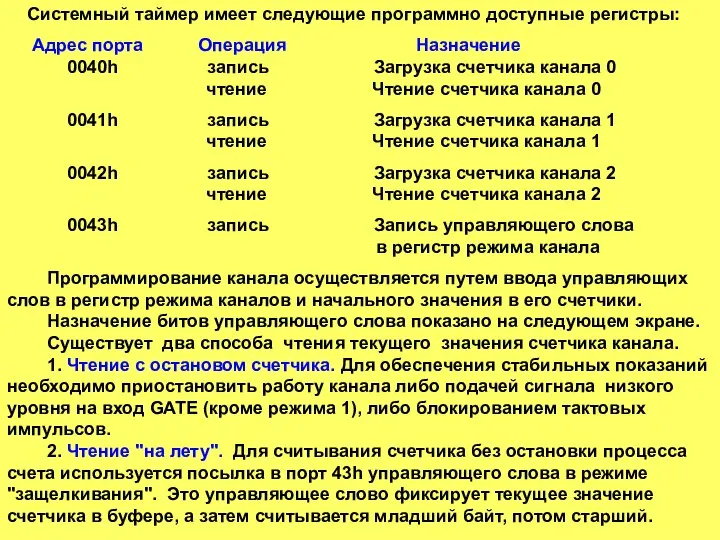

- 28. Системный таймер имеет следующие программно доступные регистры: Адрес порта Операция Назначение 0040h запись Загрузка счетчика канала

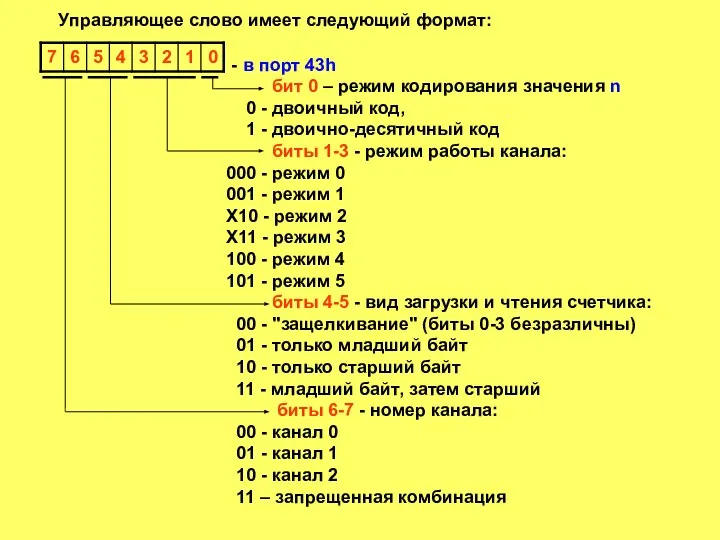

- 29. Управляющее слово имеет следующий формат: - в порт 43h бит 0 – режим кодирования значения n

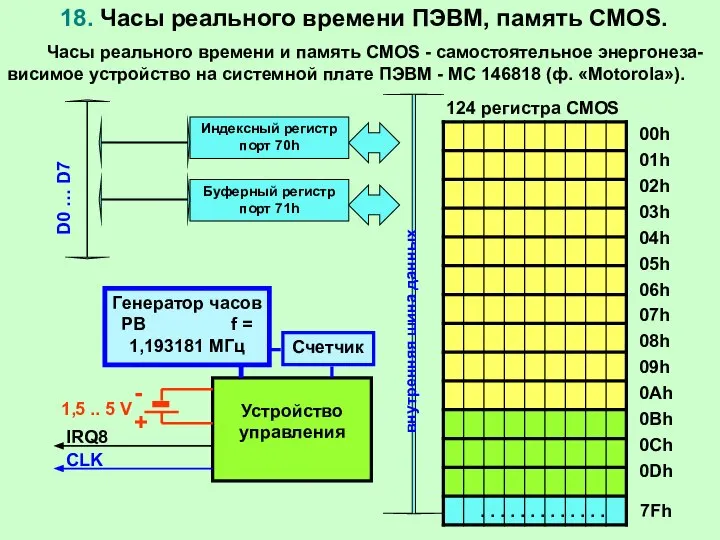

- 30. 18. Часы реального времени ПЭВМ, память CMOS. Часы реального времени и память CMOS - самостоятельное энергонеза-висимое

- 31. Содержание основных регистров часов реального времени в CMOS 00h секунды 01h секундная тренога (будильник) 02h минуты

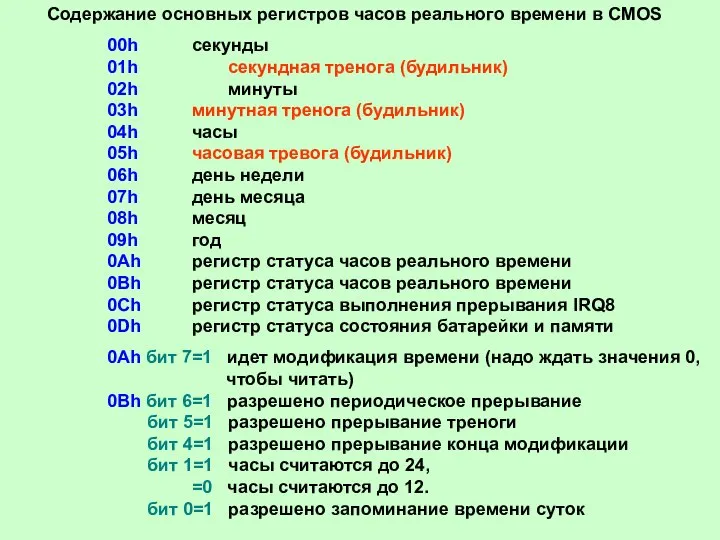

- 32. Содержание регистров SETUP в CMOS 0Eh состояние констант POST после загрузки BIOS 0Fh состояние констант POST

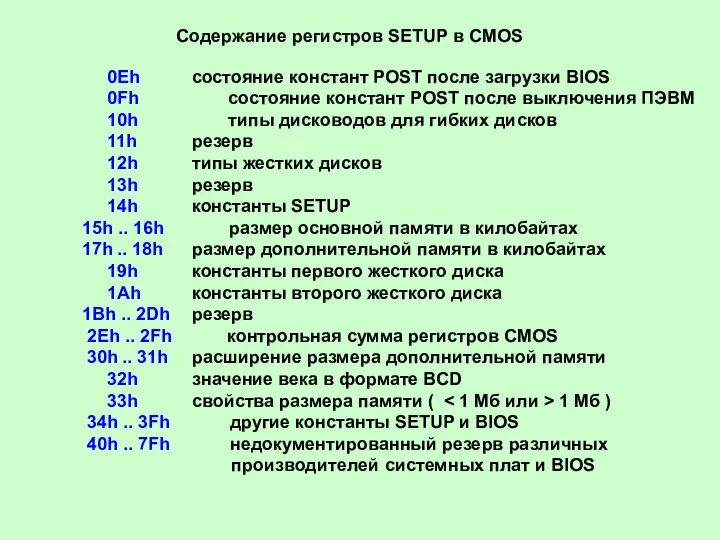

- 33. Особенности использования аппаратного прерывания IRQ8 Часы реального времени вызывают аппаратное (радиальное) прерывание IRQ8 и соответствующее векторное

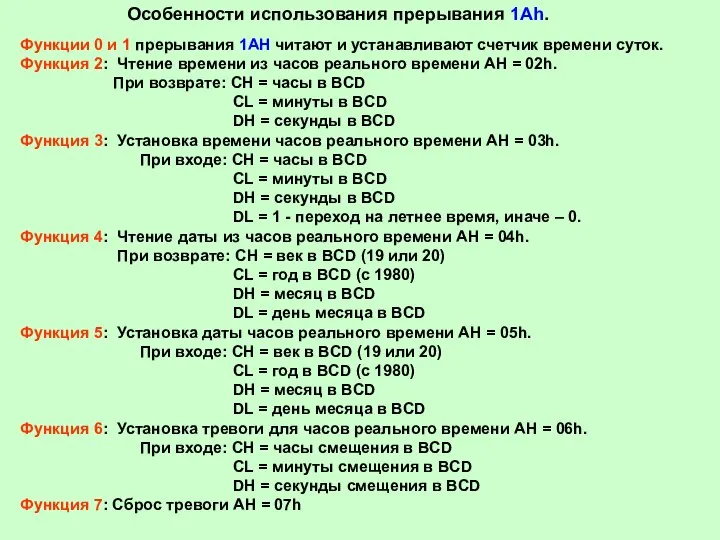

- 34. Особенности использования прерывания 1Ah. Функции 0 и 1 прерывания 1АН читают и устанавливают счетчик времени суток.

- 35. Особенности использования формата BCD. Поскольку показания часов реального времени никогда не состоят более чем из двух

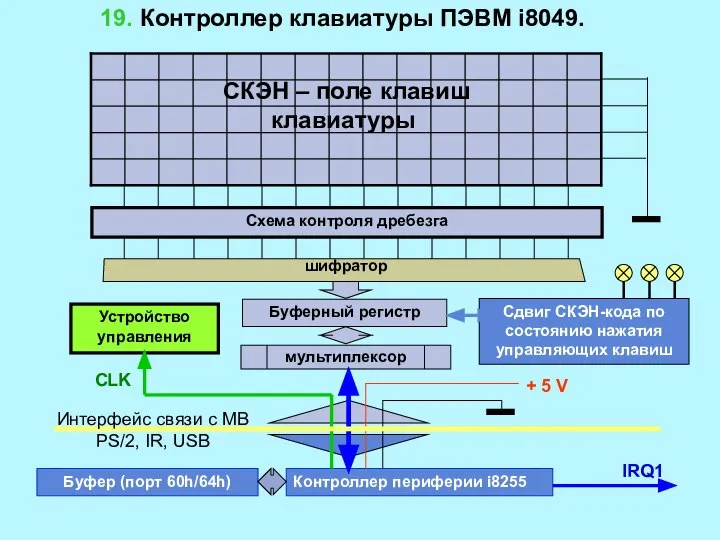

- 36. 19. Контроллер клавиатуры ПЭВМ i8049. шифратор Схема контроля дребезга Буферный регистр мультиплексор Контроллер периферии i8255 Буфер

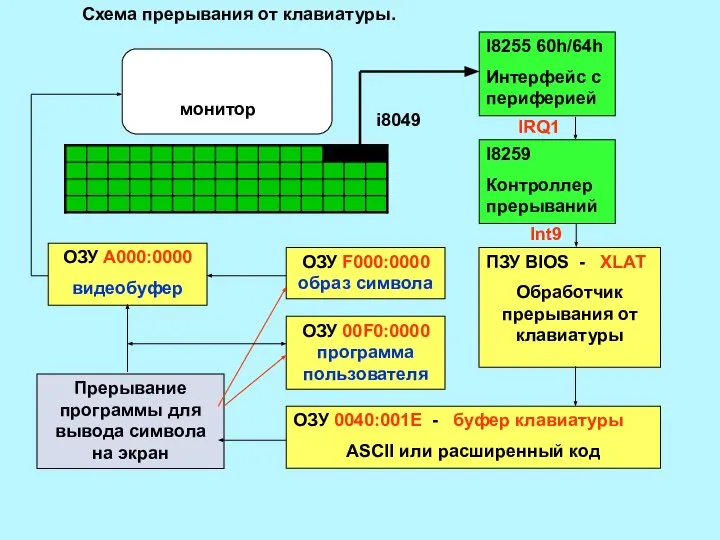

- 37. Схема прерывания от клавиатуры. i8049 I8255 60h/64h Интерфейс с периферией I8259 Контроллер прерываний IRQ1 ПЗУ BIOS

- 38. Процедура обработки СКЭН-кодов клавиатуры (XLAT) Получение скэн-кода Это клавиша Shift или переключатель ? Анализ статуса клавиш

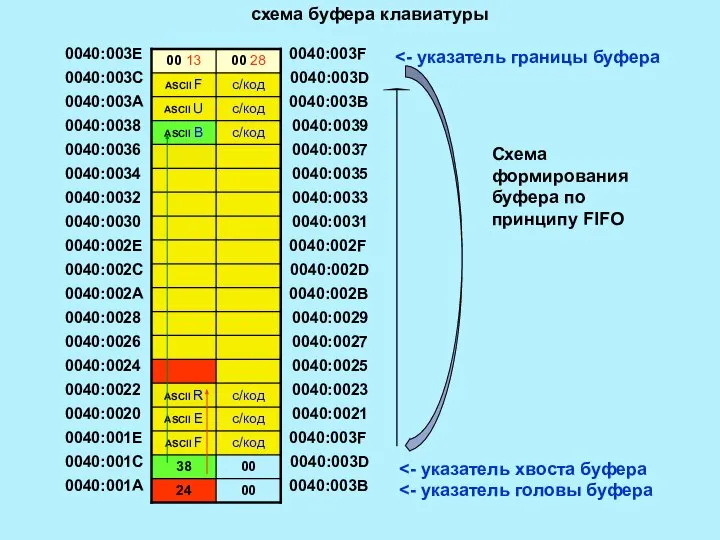

- 39. схема буфера клавиатуры 0040:003E 0040:003F 0040:003C 0040:003D 0040:003A 0040:003B 0040:0038 0040:0039 0040:0036 0040:0037 0040:0034 0040:0035 0040:0032

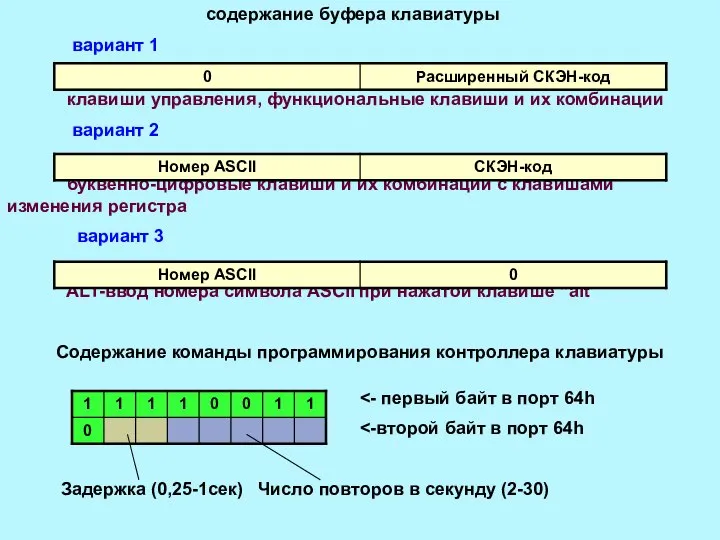

- 40. содержание буфера клавиатуры вариант 1 клавиши управления, функциональные клавиши и их комбинации вариант 2 буквенно-цифровые клавиши

- 42. Скачать презентацию

Разработка рабочего проекта, строительство, сдача и государственная регистрация объекта

Разработка рабочего проекта, строительство, сдача и государственная регистрация объекта Programmēšana pamati (speckurss)

Programmēšana pamati (speckurss) Політичний режим Бразилії

Політичний режим Бразилії Java3 (логика)

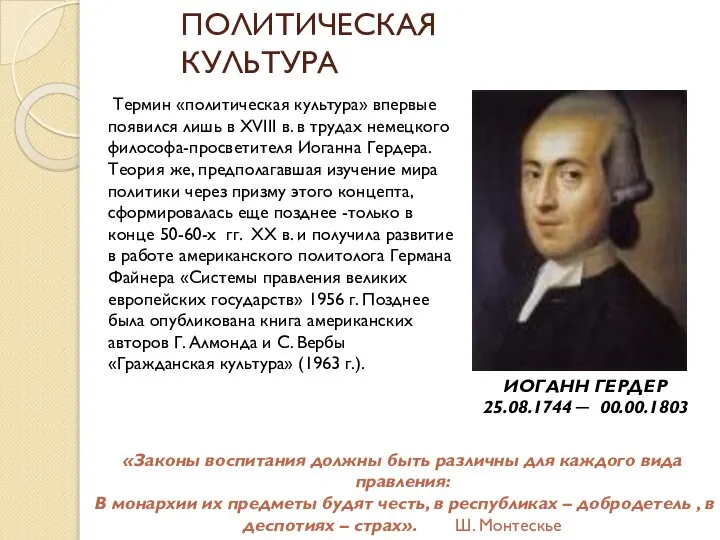

Java3 (логика) Политическая культура

Политическая культура Презентация МЕЖДУНАРОДНЫЕ СТАНДАРТЫ СОЦИАЛЬНОГО ОБЕСПЕЧЕНИЯ ЛАТВИИ

Презентация МЕЖДУНАРОДНЫЕ СТАНДАРТЫ СОЦИАЛЬНОГО ОБЕСПЕЧЕНИЯ ЛАТВИИ  Социальная политика государства. (Тема 15)

Социальная политика государства. (Тема 15) Презентация Ощущения и восприятия

Презентация Ощущения и восприятия Собственность. Имущественные отношения

Собственность. Имущественные отношения Энергоэффективные и экологические требования. Классификация жилых домов

Энергоэффективные и экологические требования. Классификация жилых домов e36a51c1

e36a51c1 Циклы Кондратьева Подготовил Столяров Е.С. Харевич М.А. группа Э-1303

Циклы Кондратьева Подготовил Столяров Е.С. Харевич М.А. группа Э-1303  Международный совет по гармонизации технических требований к регистрации лекарственных средств для человека

Международный совет по гармонизации технических требований к регистрации лекарственных средств для человека Cоставляющие стратегического управления

Cоставляющие стратегического управления  Перифериялық құралдары. Перифериялық құралдардың техникалық мүмкіндіктері, құрылымы, қолданылуы. Ақпаратты енгізу құралдары

Перифериялық құралдары. Перифериялық құралдардың техникалық мүмкіндіктері, құрылымы, қолданылуы. Ақпаратты енгізу құралдары КУЛЬТУРА ПЕРВОБЫТНОГО ОБЩЕСТВА

КУЛЬТУРА ПЕРВОБЫТНОГО ОБЩЕСТВА Формы и методы влияния идеологии на политическую активность человека. (Лекция 1)

Формы и методы влияния идеологии на политическую активность человека. (Лекция 1) Предмет науки История о государства и права России

Предмет науки История о государства и права России Бизнес-план компании «Монолит» - производство строительных материалов. Проект по экономике и экономической географии ученика

Бизнес-план компании «Монолит» - производство строительных материалов. Проект по экономике и экономической географии ученика  Вывод документов XML с использованием CSS и XSL

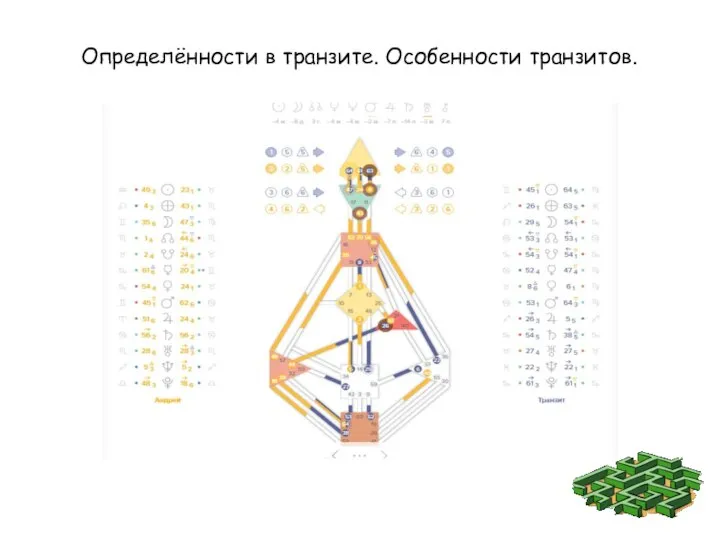

Вывод документов XML с использованием CSS и XSL Транзиты

Транзиты Посредники международной торговли и их виды Болтнева К. гр.6075

Посредники международной торговли и их виды Болтнева К. гр.6075 Леонард Эйлер (1707-1783)

Леонард Эйлер (1707-1783) Презентация "СДМ-Банк" - скачать презентации по Экономике

Презентация "СДМ-Банк" - скачать презентации по Экономике Соборы

Соборы Чуковский Корней Иванович

Чуковский Корней Иванович  Замена матрицы ноутбука

Замена матрицы ноутбука Қалқанша бездің обыры

Қалқанша бездің обыры