Содержание

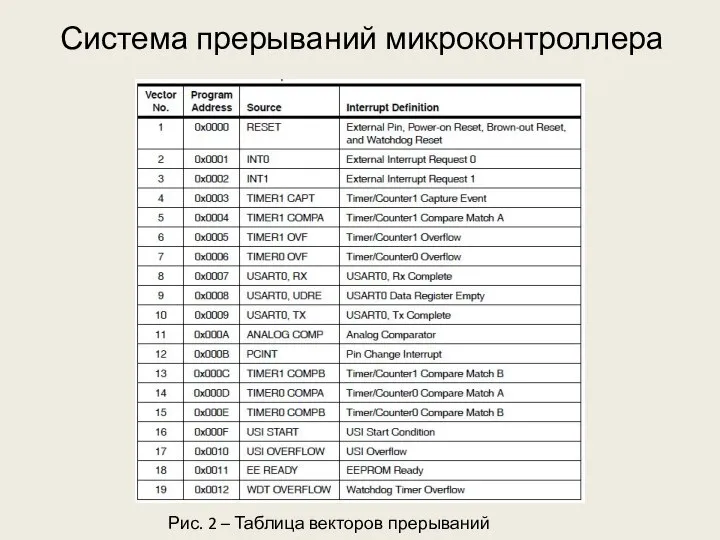

- 2. Система прерываний микроконтроллера Рис. 2 – Таблица векторов прерываний

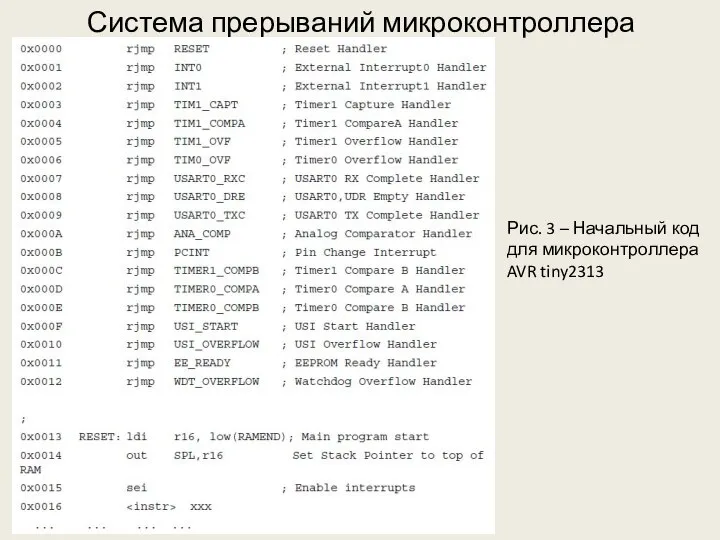

- 3. Система прерываний микроконтроллера Рис. 3 – Начальный код для микроконтроллера AVR tiny2313

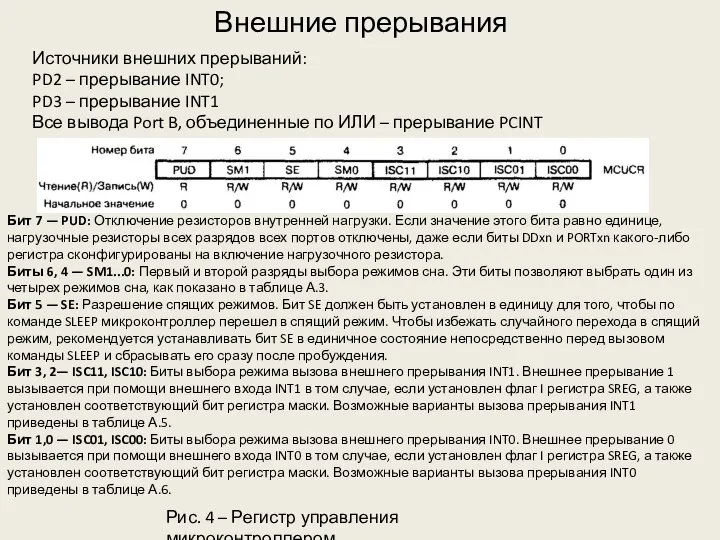

- 4. Внешние прерывания Рис. 4 – Регистр управления микроконтроллером Бит 7 — PUD: Отключение резисторов внутренней нагрузки.

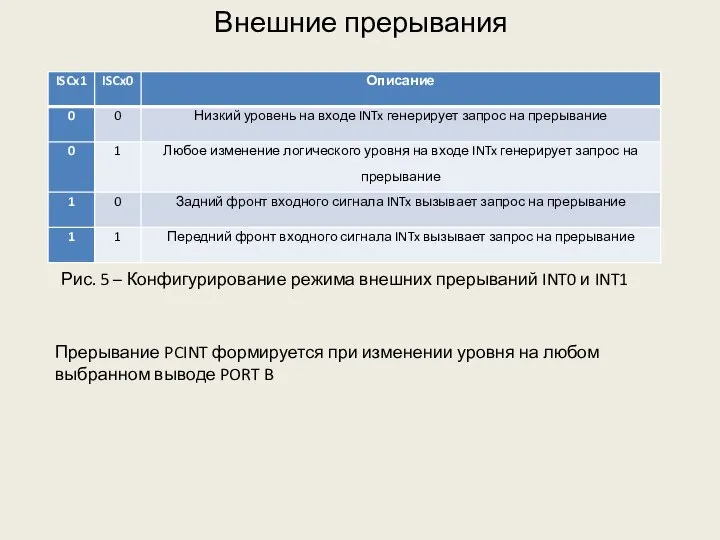

- 5. Внешние прерывания Рис. 5 – Конфигурирование режима внешних прерываний INT0 и INT1 Прерывание PCINT формируется при

- 6. Регистры для управления внешними прерываниями Рис. 6 – Регистр маски внешних прерываний GIMSK Бит 7— INT1:

- 7. Регистры для управления внешними прерываниями Рис. 7 – Регистр флагов внешних прерываний EIFR Бит 7 —

- 8. Регистры для управления внешними прерываниями Рис. 8 – Регистр маски вывода выводов Port B для прерывания

- 9. Порты ввода/вывода Типы портов в микроконтроллерах: только вход; только выход; двунаправленный вывод; вывод с альтернативными функциями

- 10. Порты ввода/вывода Рис. 10 – Функциональная схема вывода порта без учета альтернативных функций

- 12. Скачать презентацию

Система прерываний микроконтроллера

Рис. 2 – Таблица векторов прерываний

Система прерываний микроконтроллера

Рис. 2 – Таблица векторов прерываний

Система прерываний микроконтроллера

Рис. 3 – Начальный код для микроконтроллера AVR tiny2313

Система прерываний микроконтроллера

Рис. 3 – Начальный код для микроконтроллера AVR tiny2313

Внешние прерывания

Рис. 4 – Регистр управления микроконтроллером

Бит 7 — PUD: Отключение

Внешние прерывания

Рис. 4 – Регистр управления микроконтроллером

Бит 7 — PUD: Отключение

Биты 6, 4 — SM1...0: Первый и второй разряды выбора режимов сна. Эти биты позволяют выбрать один из четырех режимов сна, как показано в таблице А.3.

Бит 5 — SE: Разрешение спящих режимов. Бит SE должен быть установлен в единицу для того, чтобы по команде SLEEP микроконтроллер перешел в спящий режим. Чтобы избежать случайного перехода в спящий режим, рекомендуется устанавливать бит SE в единичное состояние непосредственно перед вызовом команды SLEEP и сбрасывать его сразу после пробуждения.

Бит 3, 2— ISC11, ISC10: Биты выбора режима вызова внешнего прерывания INT1. Внешнее прерывание 1 вызывается при помощи внешнего входа INT1 в том случае, если установлен флаг I регистра SREG, а также установлен соответствующий бит регистра маски. Возможные варианты вызова прерывания INT1 приведены в таблице А.5.

Бит 1,0 — ISC01, ISC00: Биты выбора режима вызова внешнего прерывания INT0. Внешнее прерывание 0 вызывается при помощи внешнего входа INT0 в том случае, если установлен флаг I регистра SREG, а также установлен соответствующий бит регистра маски. Возможные варианты вызова прерывания INT0 приведены в таблице А.6.

Источники внешних прерываний:

PD2 – прерывание INT0;

PD3 – прерывание INT1

Все вывода Port B, объединенные по ИЛИ – прерывание PCINT

Внешние прерывания

Рис. 5 – Конфигурирование режима внешних прерываний INT0 и INT1

Прерывание

Внешние прерывания

Рис. 5 – Конфигурирование режима внешних прерываний INT0 и INT1

Прерывание

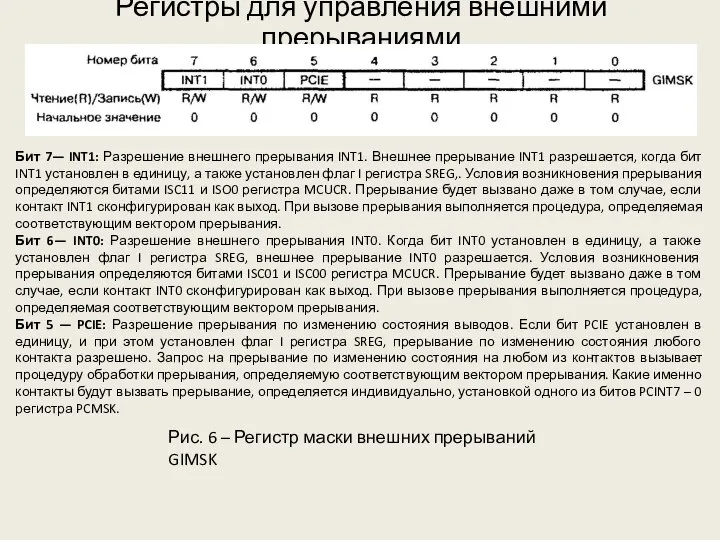

Регистры для управления внешними прерываниями

Рис. 6 – Регистр маски внешних прерываний

Регистры для управления внешними прерываниями

Рис. 6 – Регистр маски внешних прерываний

Бит 7— INT1: Разрешение внешнего прерывания INT1. Внешнее прерывание INT1 разрешается, когда бит INT1 установлен в единицу, а также установлен флаг I регистра SREG,. Условия возникновения прерывания определяются битами ISC11 и ISO0 регистра MCUCR. Прерывание будет вызвано даже в том случае, если контакт INT1 сконфигурирован как выход. При вызове прерывания выполняется процедура, определяемая соответствующим вектором прерывания.

Бит 6— INT0: Разрешение внешнего прерывания INT0. Когда бит INT0 установлен в единицу, а также установлен флаг I регистра SREG, внешнее прерывание INT0 разрешается. Условия возникновения прерывания определяются битами ISC01 и ISC00 регистра MCUCR. Прерывание будет вызвано даже в том случае, если контакт INT0 сконфигурирован как выход. При вызове прерывания выполняется процедура, определяемая соответствующим вектором прерывания.

Бит 5 — PCIE: Разрешение прерывания по изменению состояния выводов. Если бит PCIE установлен в единицу, и при этом установлен флаг I регистра SREG, прерывание по изменению состояния любого контакта разрешено. Запрос на прерывание по изменению состояния на любом из контактов вызывает процедуру обработки прерывания, определяемую соответствующим вектором прерывания. Какие именно контакты будут вызвать прерывание, определяется индивидуально, установкой одного из битов PCINT7 – 0 регистра PCMSK.

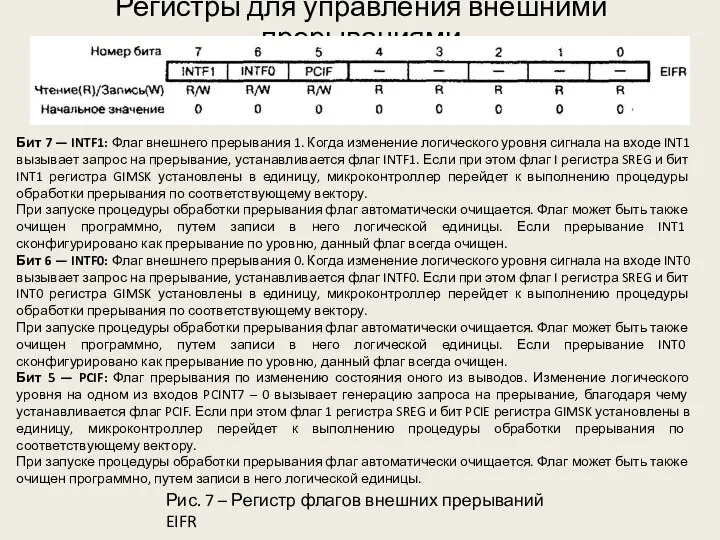

Регистры для управления внешними прерываниями

Рис. 7 – Регистр флагов внешних прерываний

Регистры для управления внешними прерываниями

Рис. 7 – Регистр флагов внешних прерываний

Бит 7 — INTF1: Флаг внешнего прерывания 1. Когда изменение логического уровня сигнала на входе INT1 вызывает запрос на прерывание, устанавливается флаг INTF1. Если при этом флаг I регистра SREG и бит INT1 регистра GIMSK установлены в единицу, микроконтроллер перейдет к выполнению процедуры обработки прерывания по соответствующему вектору.

При запуске процедуры обработки прерывания флаг автоматически очищается. Флаг может быть также очищен программно, путем записи в него логической единицы. Если прерывание INT1 сконфигурировано как прерывание по уровню, данный флаг всегда очищен.

Бит 6 — INTF0: Флаг внешнего прерывания 0. Когда изменение логического уровня сигнала на входе INT0 вызывает запрос на прерывание, устанавливается флаг INTF0. Если при этом флаг I регистра SREG и бит INT0 регистра GIMSK установлены в единицу, микроконтроллер перейдет к выполнению процедуры обработки прерывания по соответствующему вектору.

При запуске процедуры обработки прерывания флаг автоматически очищается. Флаг может быть также очищен программно, путем записи в него логической единицы. Если прерывание INT0 сконфигурировано как прерывание по уровню, данный флаг всегда очищен.

Бит 5 — PCIF: Флаг прерывания по изменению состояния оного из выводов. Изменение логического уровня на одном из входов PCINT7 – 0 вызывает генерацию запроса на прерывание, благодаря чему устанавливается флаг PCIF. Если при этом флаг 1 регистра SREG и бит PCIE регистра GIMSK установлены в единицу, микроконтроллер перейдет к выполнению процедуры обработки прерывания по соответствующему вектору.

При запуске процедуры обработки прерывания флаг автоматически очищается. Флаг может быть также очищен программно, путем записи в него логической единицы.

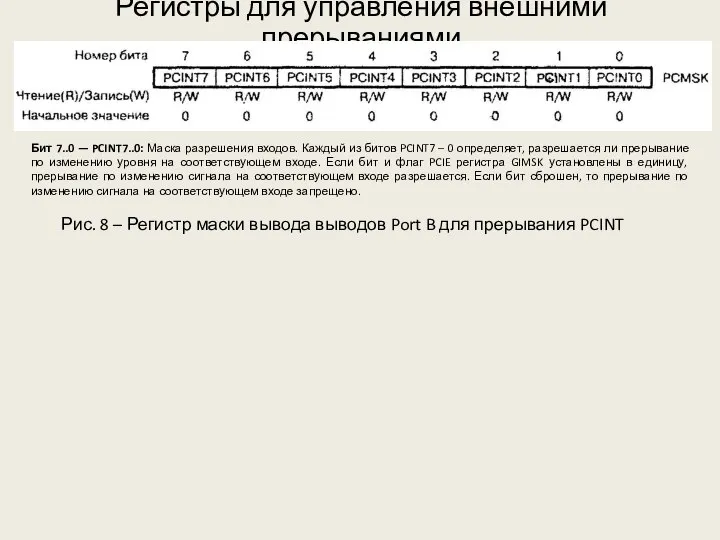

Регистры для управления внешними прерываниями

Рис. 8 – Регистр маски вывода выводов

Регистры для управления внешними прерываниями

Рис. 8 – Регистр маски вывода выводов

Бит 7..0 — PCINT7..0: Маска разрешения входов. Каждый из битов PCINT7 – 0 определяет, разрешается ли прерывание по изменению уровня на соответствующем входе. Если бит и флаг PCIE регистра GIMSK установлены в единицу, прерывание по изменению сигнала на соответствующем входе разрешается. Если бит сброшен, то прерывание по изменению сигнала на соответствующем входе запрещено.

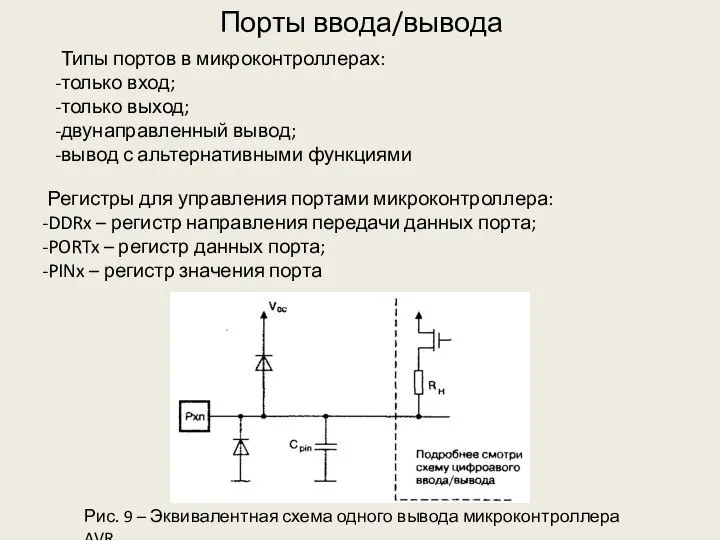

Порты ввода/вывода

Типы портов в микроконтроллерах:

только вход;

только выход;

двунаправленный вывод;

вывод с альтернативными функциями

Рис.

Порты ввода/вывода

Типы портов в микроконтроллерах:

только вход;

только выход;

двунаправленный вывод;

вывод с альтернативными функциями

Рис.

Регистры для управления портами микроконтроллера:

DDRx – регистр направления передачи данных порта;

PORTx – регистр данных порта;

PINx – регистр значения порта

Порты ввода/вывода

Рис. 10 – Функциональная схема вывода порта без учета альтернативных

Порты ввода/вывода

Рис. 10 – Функциональная схема вывода порта без учета альтернативных

Воспитание чувства патриотизма на уроках русского языка и литературы

Воспитание чувства патриотизма на уроках русского языка и литературы  Игра по правилам дорожного движения Колесо истории

Игра по правилам дорожного движения Колесо истории  Распределительный закон умножения 5 класс

Распределительный закон умножения 5 класс Тайны грибного царства - презентация для начальной школы_

Тайны грибного царства - презентация для начальной школы_ БД, принципы построения, соответствие БД действительности

БД, принципы построения, соответствие БД действительности Трансмиссия автомобиля. Коробка передач

Трансмиссия автомобиля. Коробка передач Прыжок в высоту с разбега. Легкая атлетика. Анализ техники и методика обучения

Прыжок в высоту с разбега. Легкая атлетика. Анализ техники и методика обучения Изгибаемые элементы. Расчет прочности нормальных сечений. Тема 7

Изгибаемые элементы. Расчет прочности нормальных сечений. Тема 7 Дороги и дорожное строительство в городе. Проблема отходов. Особенности среды обитания в сельской местности

Дороги и дорожное строительство в городе. Проблема отходов. Особенности среды обитания в сельской местности Личный кабинет клиента my.ponyexpress.ru

Личный кабинет клиента my.ponyexpress.ru Великие Капподокийцы. Святитель Василий Великий (Кесарийский) (ок. 329-379)

Великие Капподокийцы. Святитель Василий Великий (Кесарийский) (ок. 329-379) Техника безопасности при эксплуатации ПСГ

Техника безопасности при эксплуатации ПСГ Современные культурологические теории (часть 2)

Современные культурологические теории (часть 2) Логическое мышление

Логическое мышление  Магнітний запис інформації

Магнітний запис інформації Błogosławiony Edmund Bojanowski

Błogosławiony Edmund Bojanowski ХиТРРЭ.pptx

ХиТРРЭ.pptx Искусственный интеллект и профессии будущего

Искусственный интеллект и профессии будущего История религии

История религии Объектно-ориентированное программирование. Введение в язык C#

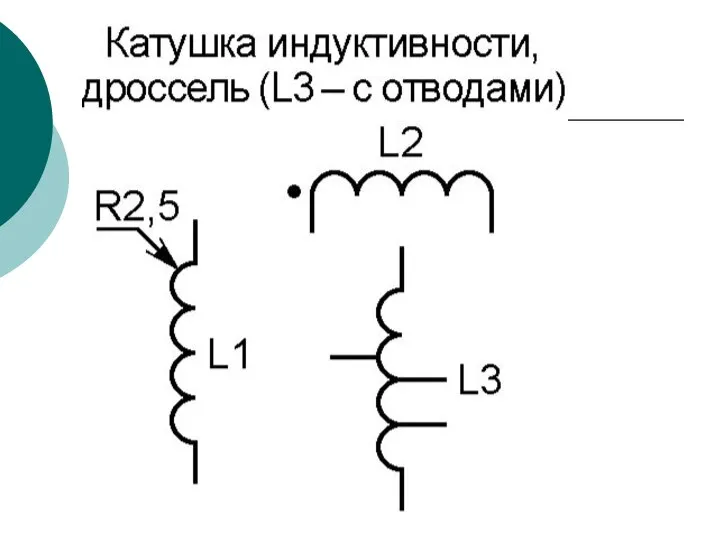

Объектно-ориентированное программирование. Введение в язык C# Катушка индуктивности, дроссель

Катушка индуктивности, дроссель Муниципальные выборы. Выдвижение начинается

Муниципальные выборы. Выдвижение начинается Анализ туристско-рекреационного потенциала национального парка «Нарочанский»

Анализ туристско-рекреационного потенциала национального парка «Нарочанский» Гастрономический туризм

Гастрономический туризм Поршеньді компрессорларды жөндеу

Поршеньді компрессорларды жөндеу теоретич основы МТ 1.ppt

теоретич основы МТ 1.ppt Chesapeake Bay Bridge-Tunnel

Chesapeake Bay Bridge-Tunnel МХК 5 класс Зачет по теме: «Аполлон и музы Парнаса»

МХК 5 класс Зачет по теме: «Аполлон и музы Парнаса»