Содержание

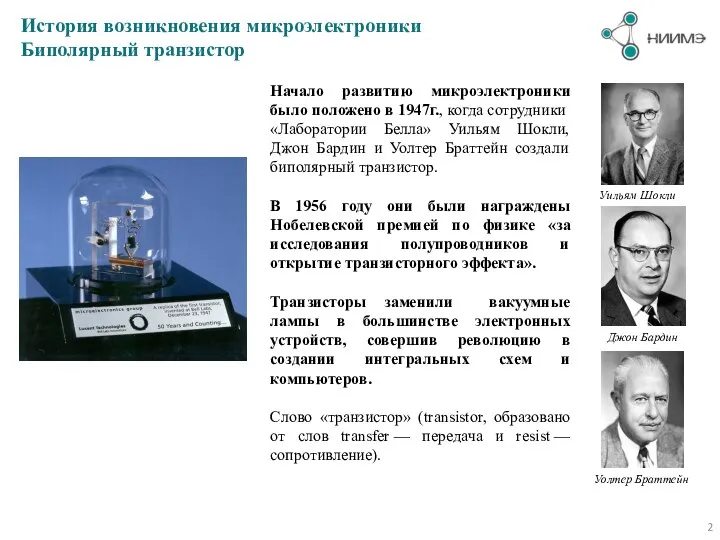

- 2. История возникновения микроэлектроники Биполярный транзистор Начало развитию микроэлектроники было положено в 1947г., когда сотрудники «Лаборатории Белла»

- 3. История возникновения микроэлектроники Полевой транзистор Первые патенты на принцип работы полевых транзисторов были зарегистрированы в Германии

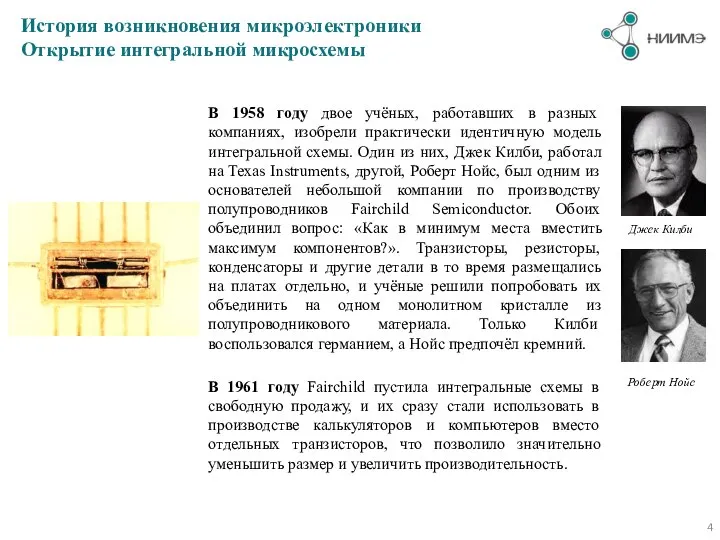

- 4. История возникновения микроэлектроники Открытие интегральной микросхемы В 1958 году двое учёных, работавших в разных компаниях, изобрели

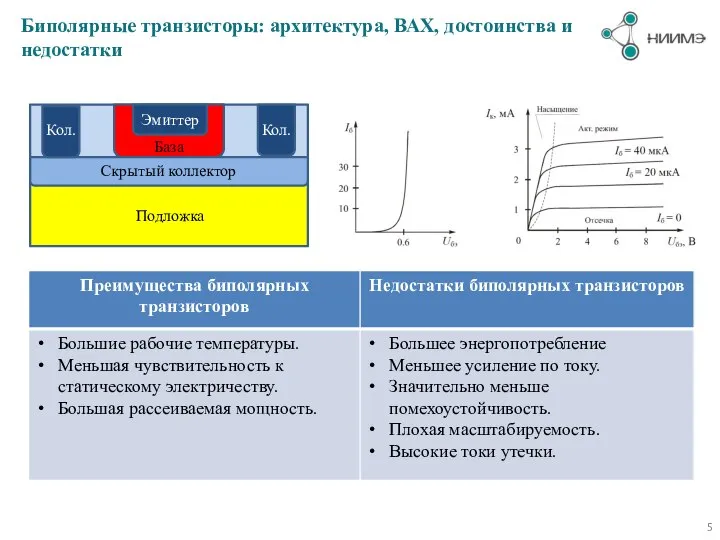

- 5. Биполярные транзисторы: архитектура, ВАХ, достоинства и недостатки

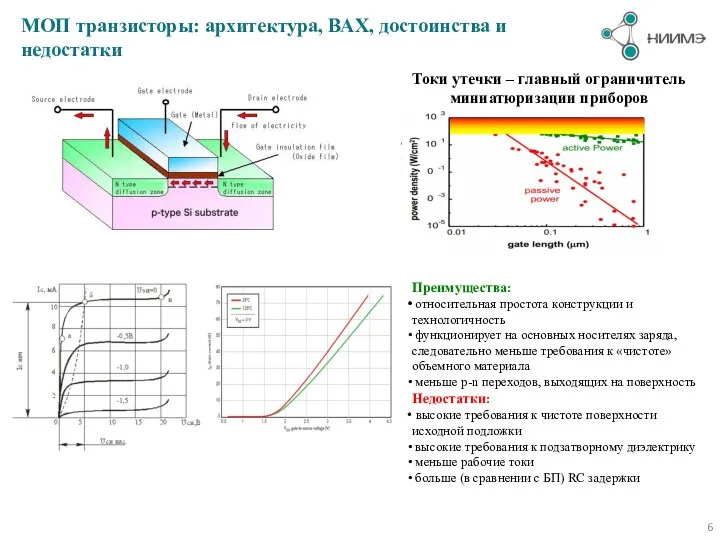

- 6. МОП транзисторы: архитектура, ВАХ, достоинства и недостатки Токи утечки – главный ограничитель миниатюризации приборов Преимущества: относительная

- 7. Межтранзисторная изоляция биполярных транзисторов Изоляция обратносмещенным p-n переходом Диэлектрическая изоляция n+ n+ SiO2 n n Si

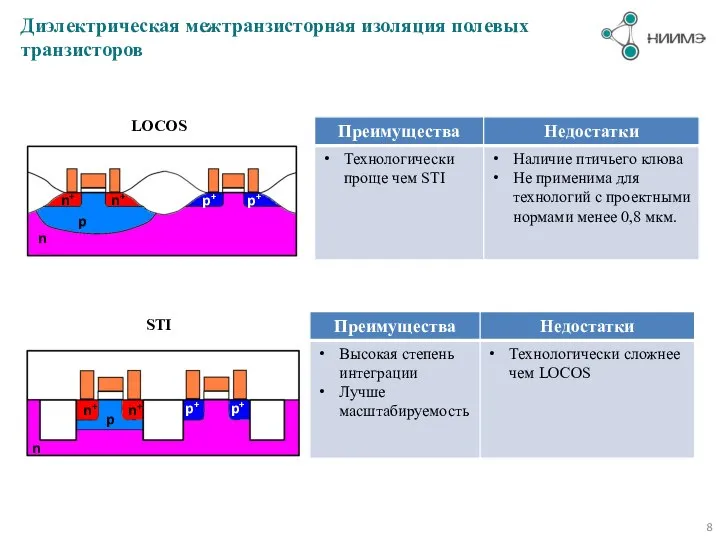

- 8. Диэлектрическая межтранзисторная изоляция полевых транзисторов LOCOS STI n n n+ n+ p p n+ n+ p+

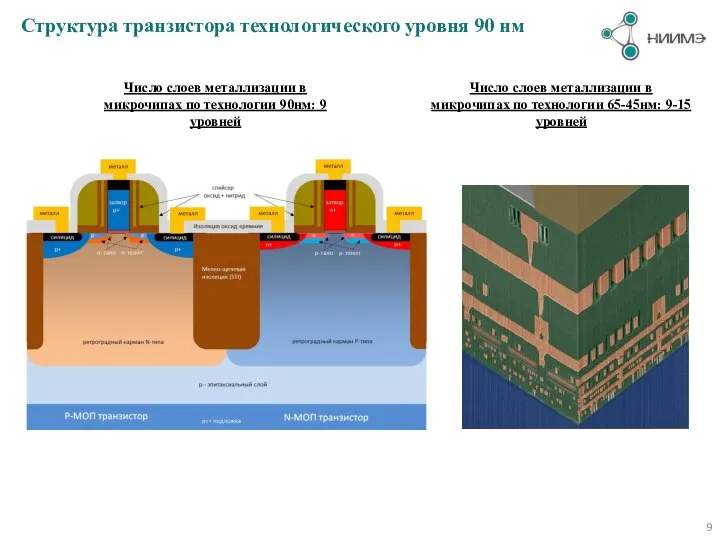

- 9. Структура транзистора технологического уровня 90 нм Число слоев металлизации в микрочипах по технологии 65-45нм: 9-15 уровней

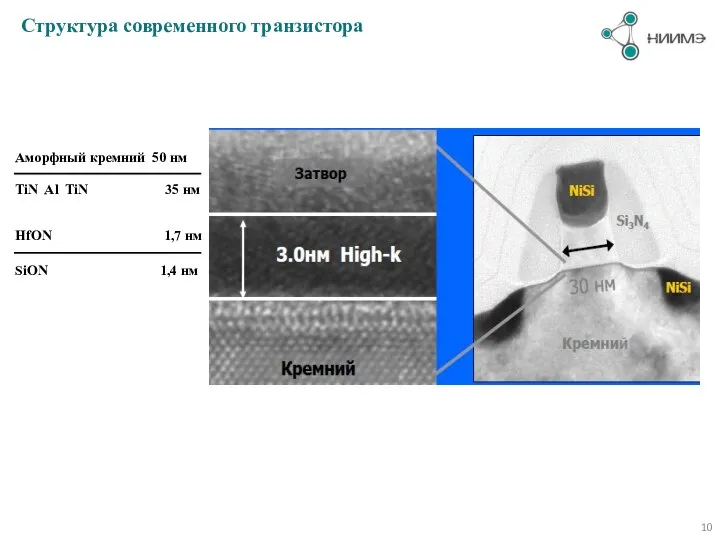

- 10. Структура современного транзистора Аморфный кремний 50 нм TiN Al TiN 35 нм HfON 1,7 нм SiON

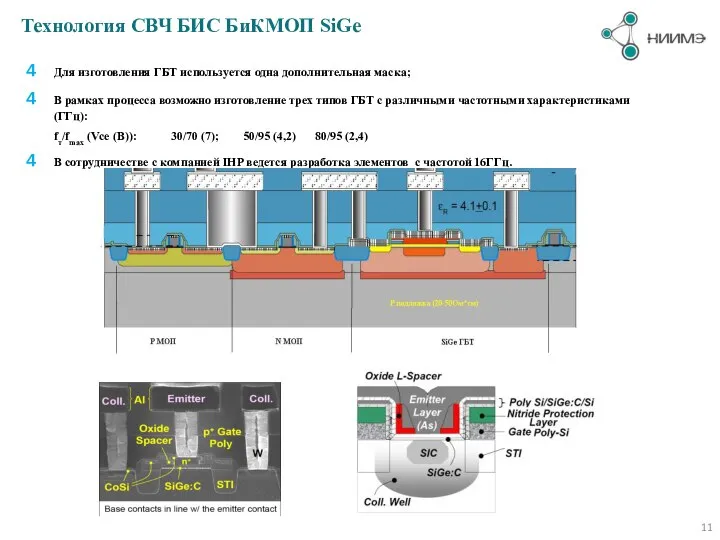

- 11. Технология СВЧ БИС БиКМОП SiGe Для изготовления ГБТ используется одна дополнительная маска; В рамках процесса возможно

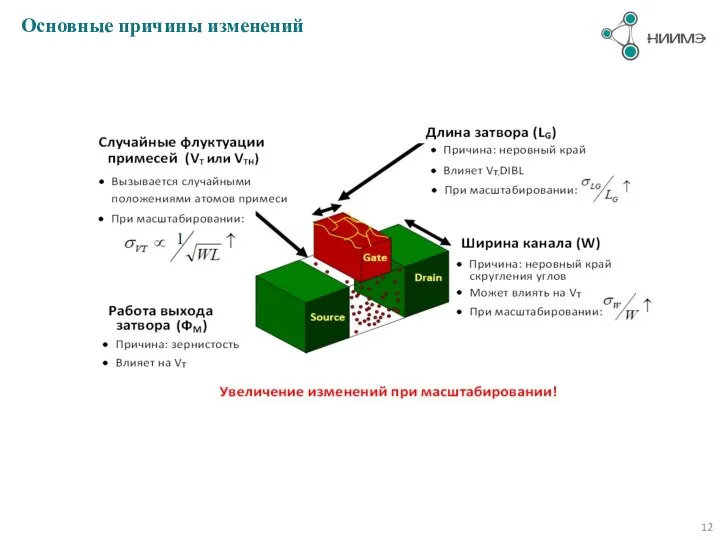

- 12. Основные причины изменений

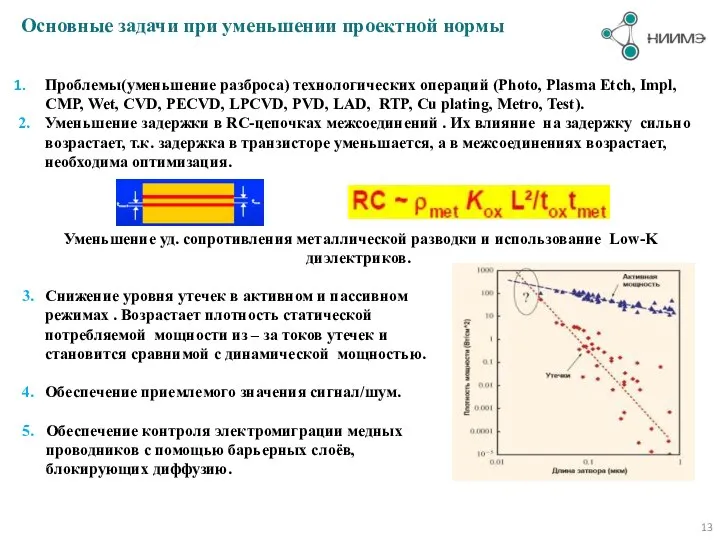

- 13. Основные задачи при уменьшении проектной нормы Проблемы(уменьшение разброса) технологических операций (Photo, Plasma Etch, Impl, CMP, Wet,

- 14. С каждым следующим поколением технологический рост производительности чипов все сильнее определяется новыми материалами, а не только

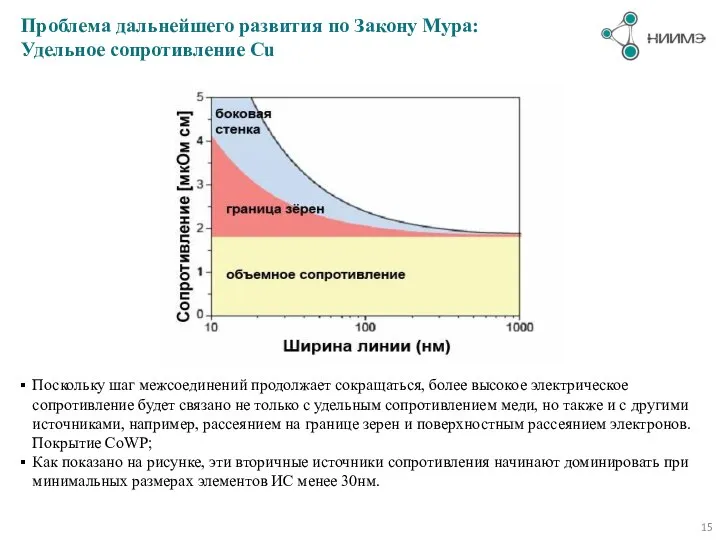

- 15. Проблема дальнейшего развития по Закону Мура: Удельное сопротивление Cu Поскольку шаг межсоединений продолжает сокращаться, более высокое

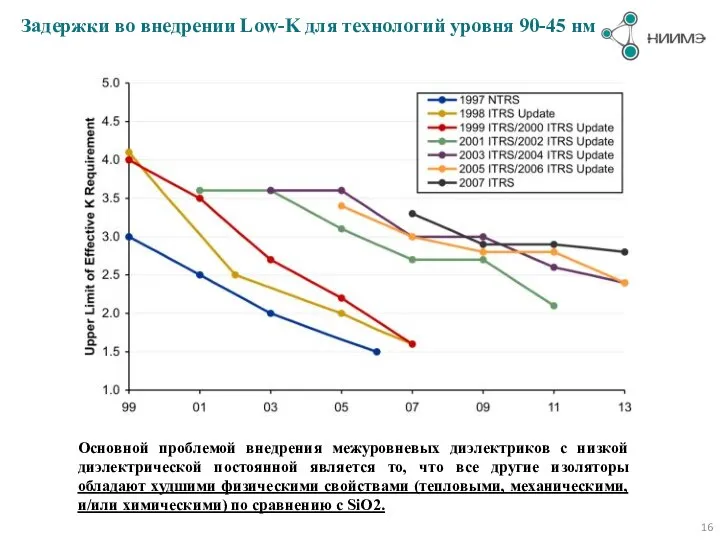

- 16. Задержки во внедрении Low-K для технологий уровня 90-45 нм Основной проблемой внедрения межуровневых диэлектриков с низкой

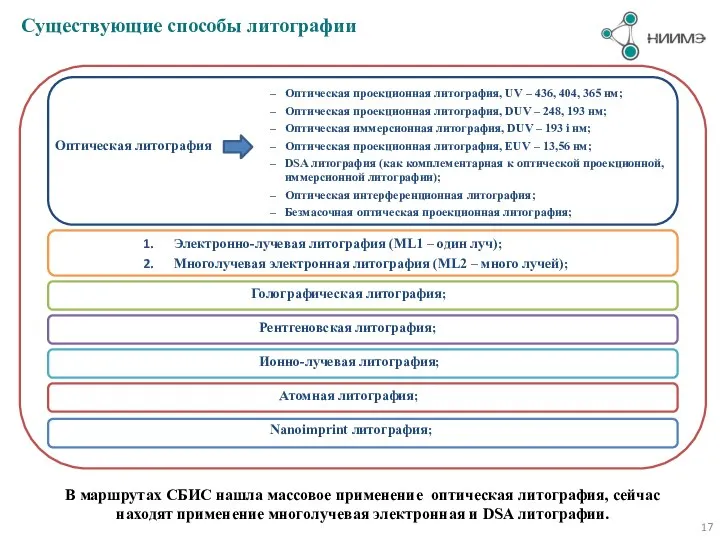

- 17. Оптическая литография Существующие способы литографии Оптическая проекционная литография, UV – 436, 404, 365 нм; Оптическая проекционная

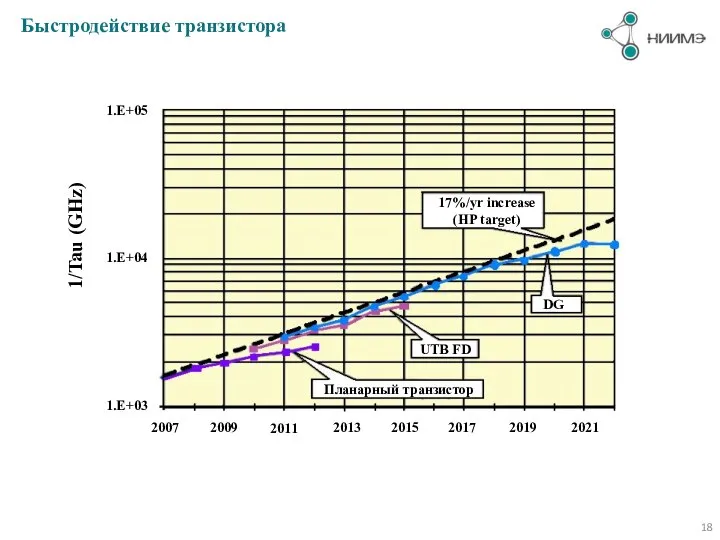

- 18. Быстродействие транзистора

- 19. Транзисторные структуры с увеличенной подвижностью µ-enhanced Напряжения сжатия или растяжения Si3N4 в зависимости от параметров нанесения

- 20. Транзистор с полностью обедненным каналом (FD-SOI) 28-10 нм Основные производители: STMicroelectronics, Global Foundries, IBM Мировой технологический

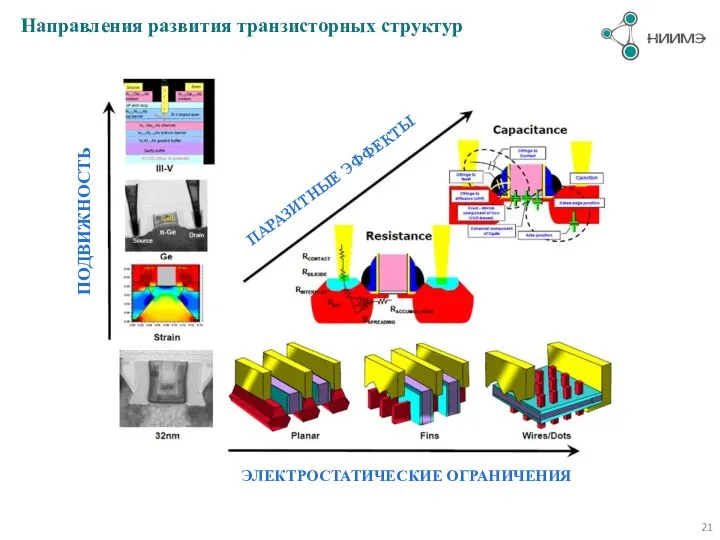

- 21. Направления развития транзисторных структур ПОДВИЖНОСТЬ ПАРАЗИТНЫЕ ЭФФЕКТЫ ЭЛЕКТРОСТАТИЧЕСКИЕ ОГРАНИЧЕНИЯ

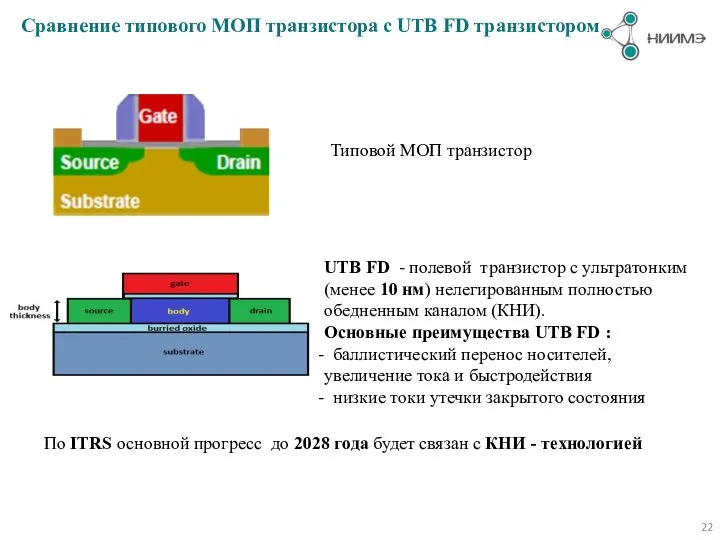

- 22. Сравнение типового МОП транзистора с UTB FD транзистором По ITRS основной прогресс до 2028 года будет

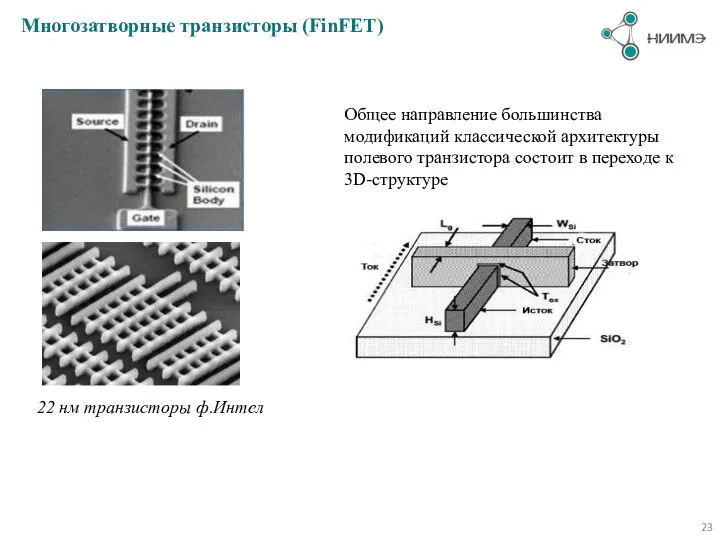

- 23. Многозатворные транзисторы (FinFET) Общее направление большинства модификаций классической архитектуры полевого транзистора состоит в переходе к 3D-структуре

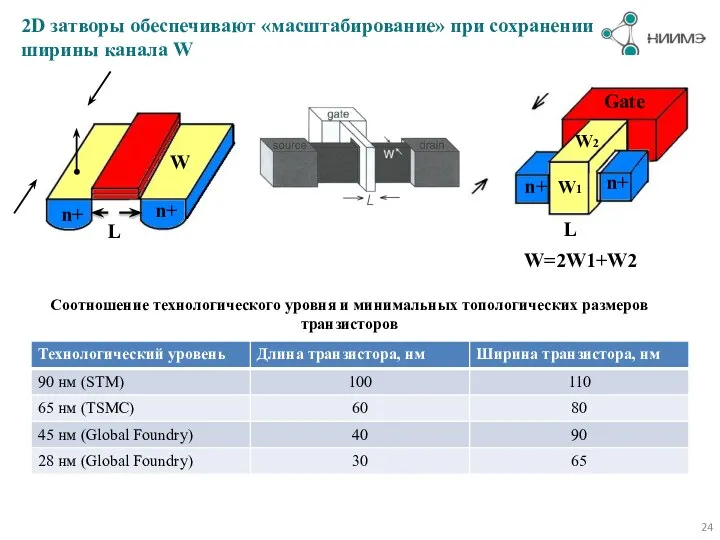

- 24. 2D затворы обеспечивают «масштабирование» при сохранении ширины канала W W n+ L Gate W2 W1 n+

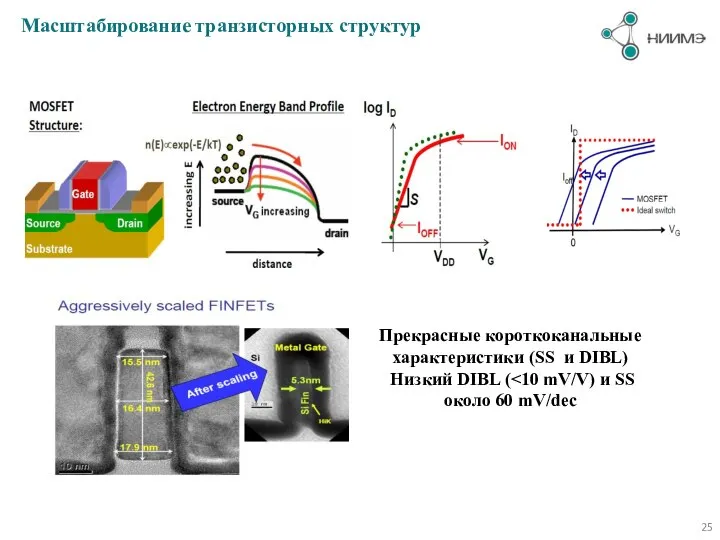

- 25. Масштабирование транзисторных структур Прекрасные короткоканальные характеристики (SS и DIBL) Низкий DIBL (

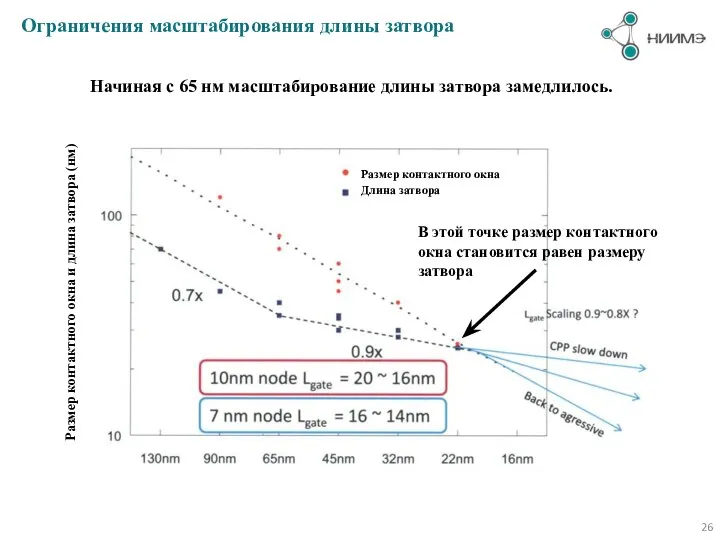

- 26. Ограничения масштабирования длины затвора Начиная с 65 нм масштабирование длины затвора замедлилось. Размер контактного окна и

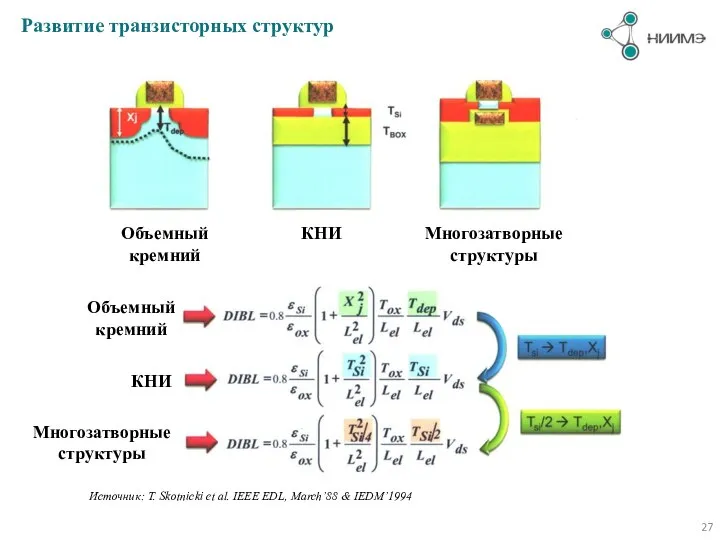

- 27. Развитие транзисторных структур Источник: T. Skotnicki et al. IEEE EDL, March’88 & IEDM’1994 Объемный кремний КНИ

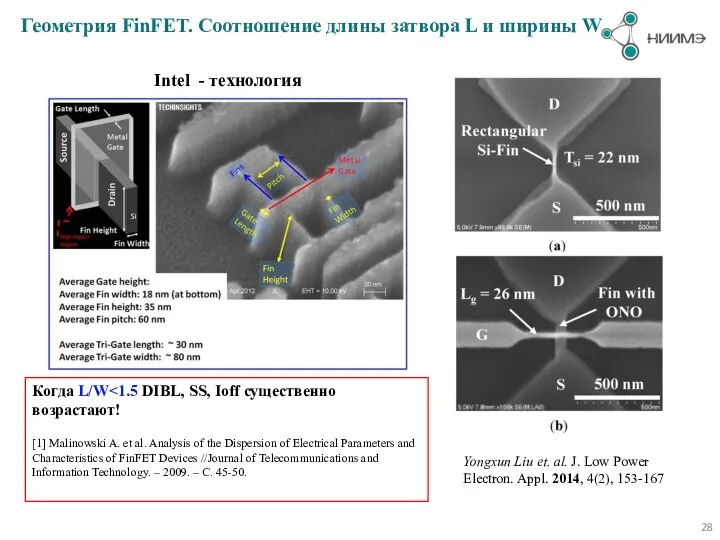

- 28. Геометрия FinFET. Соотношение длины затвора L и ширины W Intel - технология Когда L/W [1] Malinowski

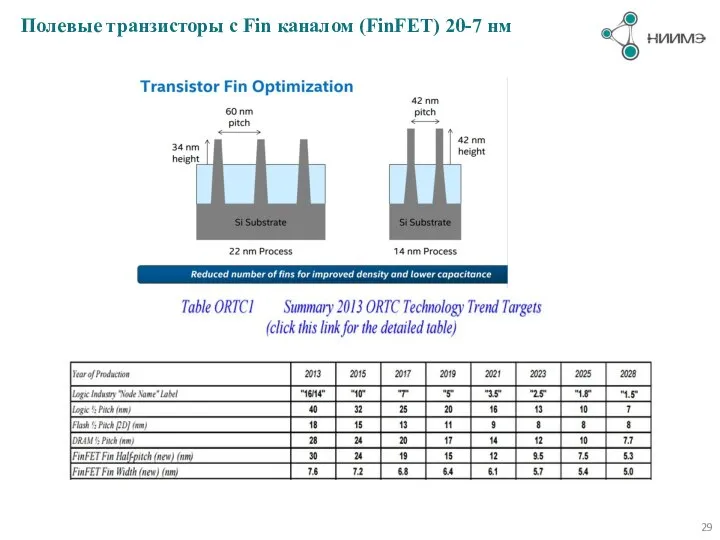

- 29. Полевые транзисторы с Fin каналом (FinFET) 20-7 нм

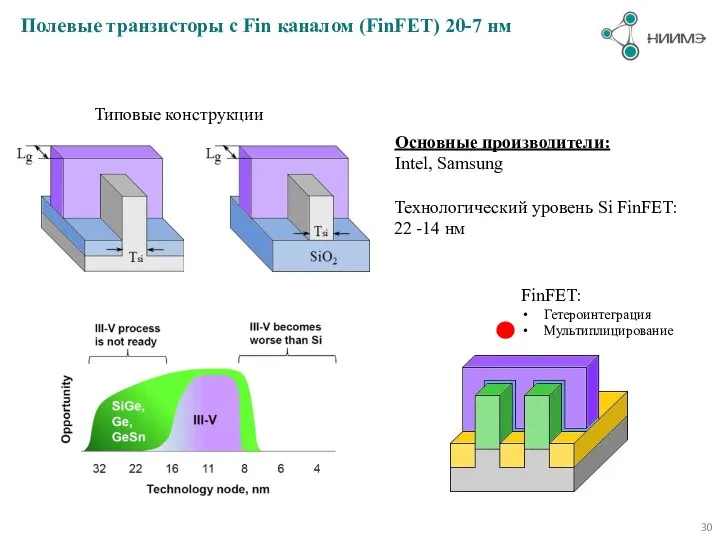

- 30. Полевые транзисторы с Fin каналом (FinFET) 20-7 нм Типовые конструкции Основные производители: Intel, Samsung Технологический уровень

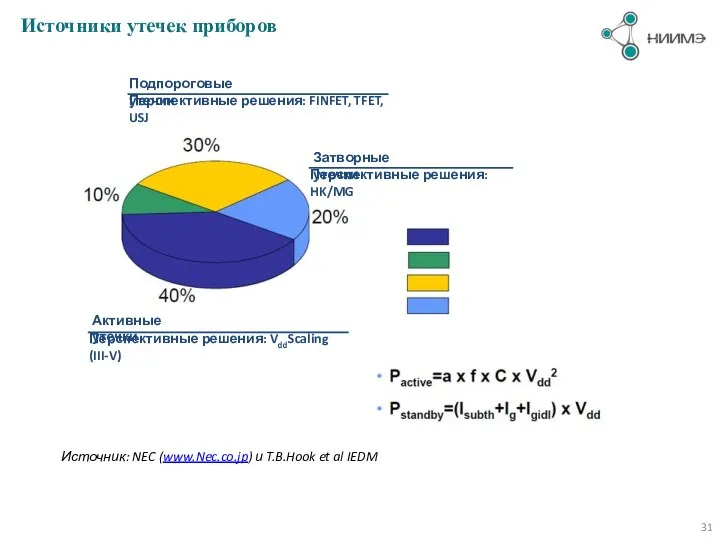

- 31. Источники утечек приборов Источник: NEC (www.Nec.co.jp) и T.B.Hook et al IEDM Подпороговые утечки Перспективные решения: FINFET,

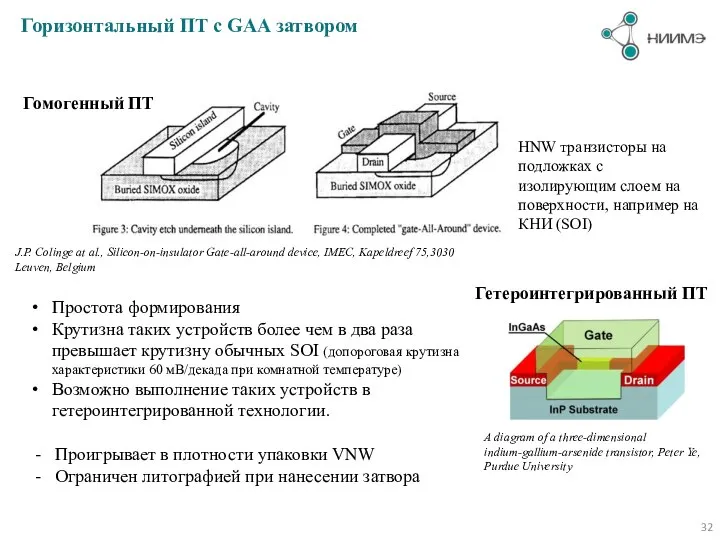

- 32. Горизонтальный ПТ с GAA затвором HNW транзисторы на подложках с изолирующим слоем на поверхности, например на

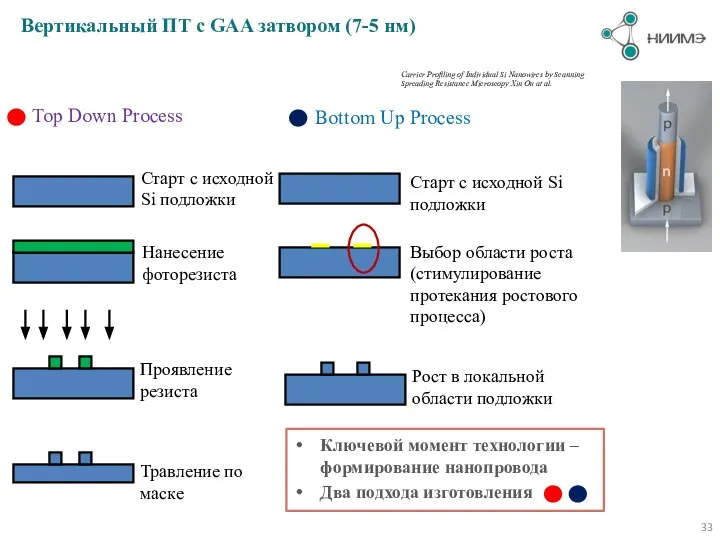

- 33. Вертикальный ПТ с GAA затвором (7-5 нм) Ключевой момент технологии – формирование нанопровода Два подхода изготовления

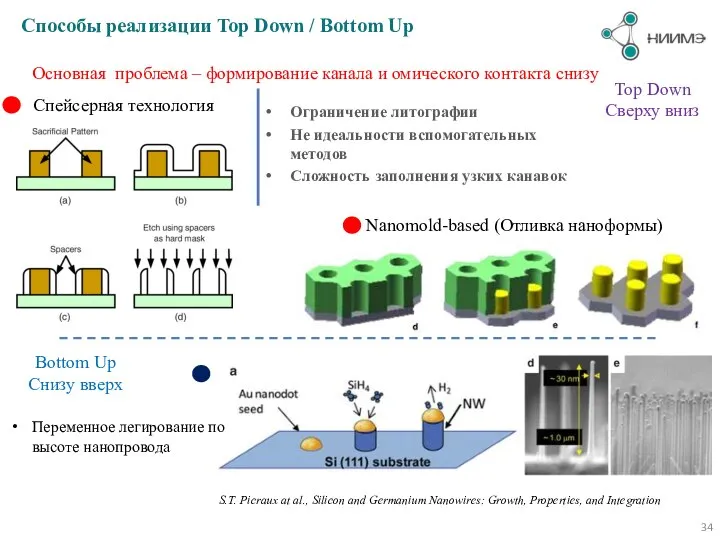

- 34. Способы реализации Top Down / Bottom Up Ограничение литографии Не идеальности вспомогательных методов Сложность заполнения узких

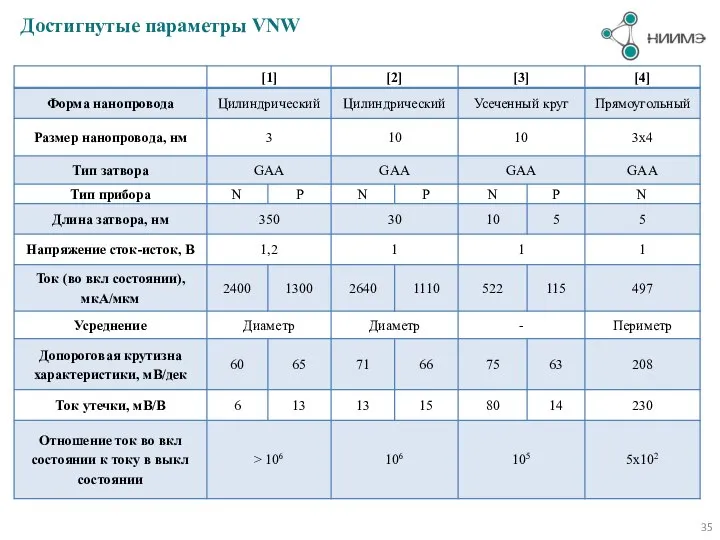

- 35. Достигнутые параметры VNW

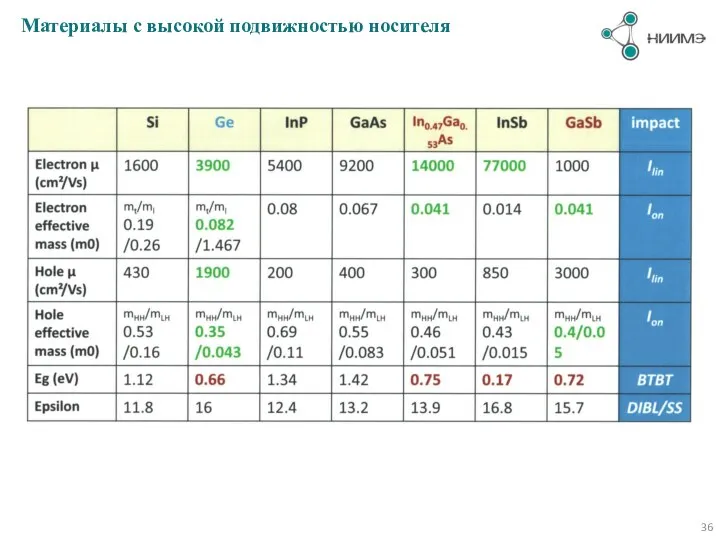

- 36. Материалы с высокой подвижностью носителя

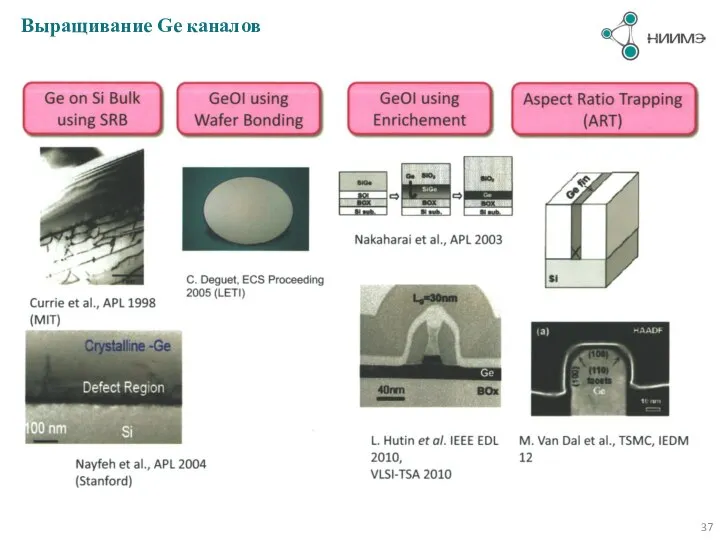

- 37. Выращивание Ge каналов

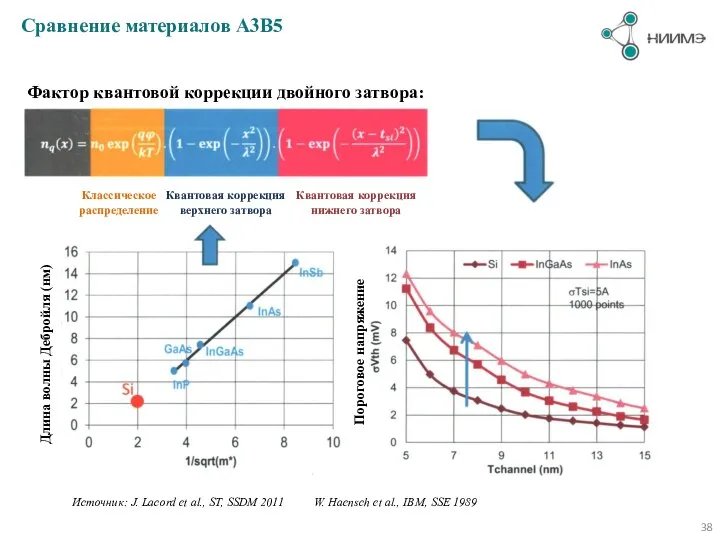

- 38. Сравнение материалов A3B5 Длина волны Дебройля (нм) Фактор квантовой коррекции двойного затвора: Классическое распределение Квантовая коррекция

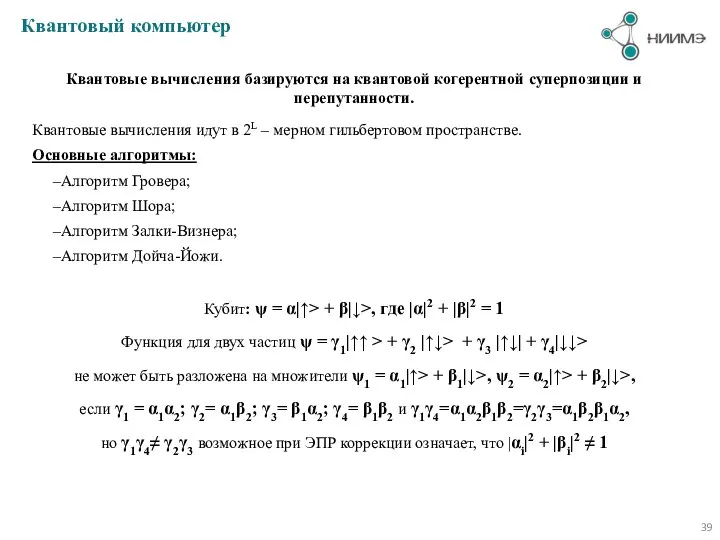

- 39. Квантовый компьютер Квантовые вычисления базируются на квантовой когерентной суперпозиции и перепутанности. Квантовые вычисления идут в 2L

- 40. Технологический уровень 7 нм? Возможные варианты реализации транзисторных структур:

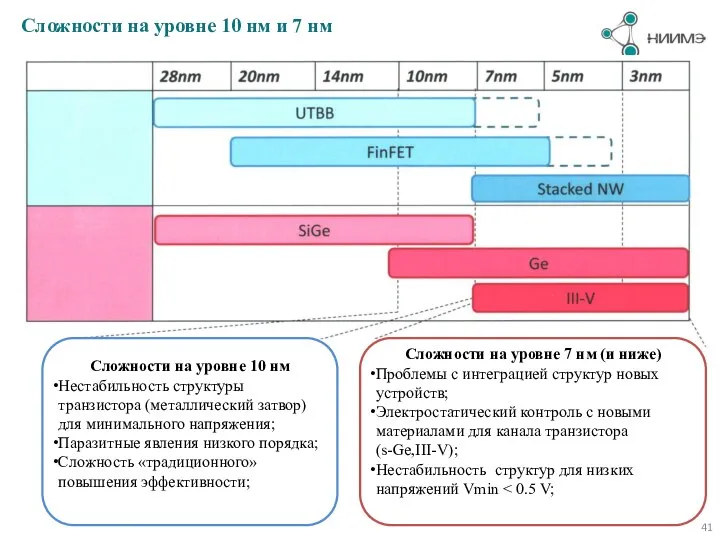

- 41. Сложности на уровне 10 нм и 7 нм Сложности на уровне 10 нм Нестабильность структуры транзистора

- 42. Вертикальный транзистор с поликремниевым затвором для 3D микросхем SONOS памяти Поперечное сечение

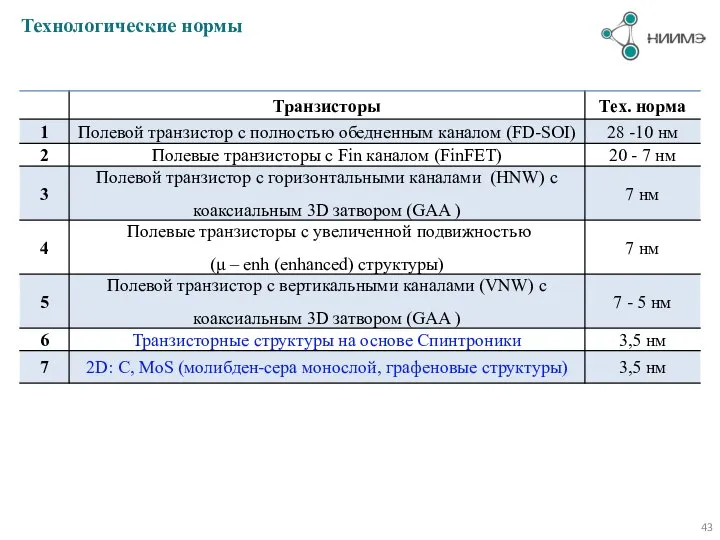

- 43. Технологические нормы

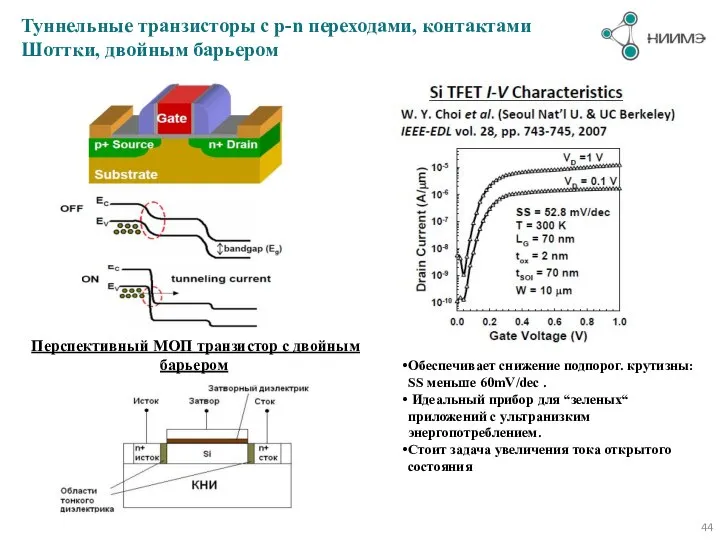

- 44. Туннельные транзисторы с p-n переходами, контактами Шоттки, двойным барьером Обеспечивает снижение подпорог. крутизны: SS меньше 60mV/dec

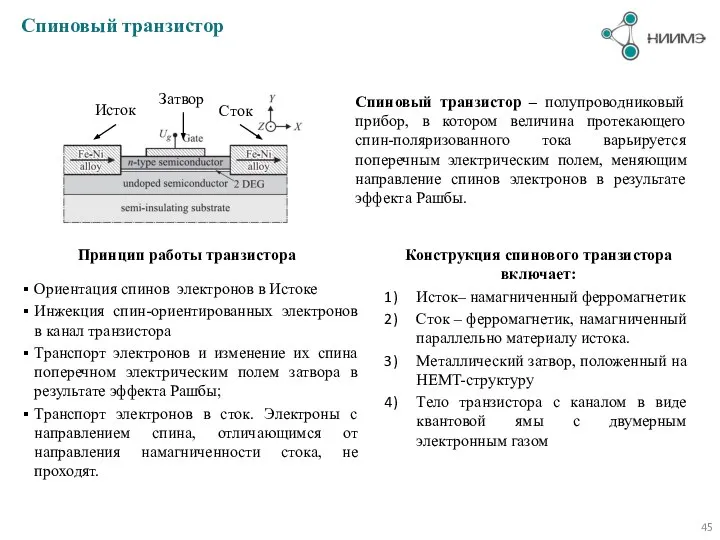

- 45. Спиновый транзистор Спиновый транзистор – полупроводниковый прибор, в котором величина протекающего спин-поляризованного тока варьируется поперечным электрическим

- 46. Одноэлектронный транзистор Источник: Песнов Д.Е., МГУ, 2010г. Идея транзистора предложена К. Лихаревым в 1986г., но до

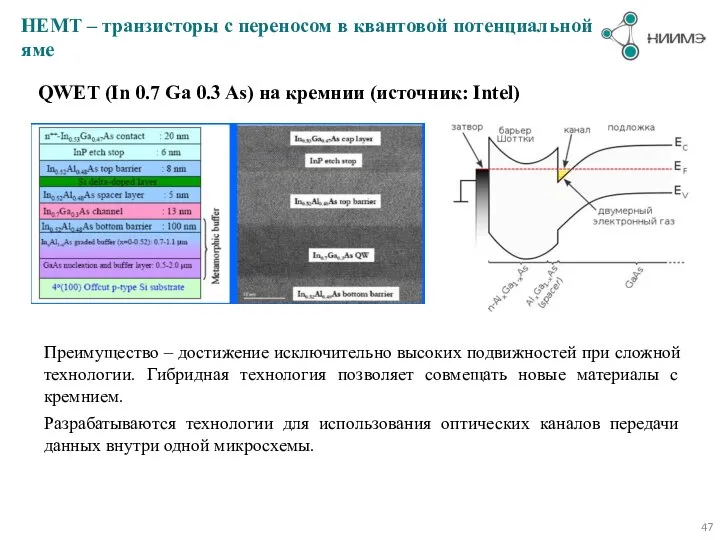

- 47. HEMT – транзисторы с переносом в квантовой потенциальной яме QWET (In 0.7 Ga 0.3 As) на

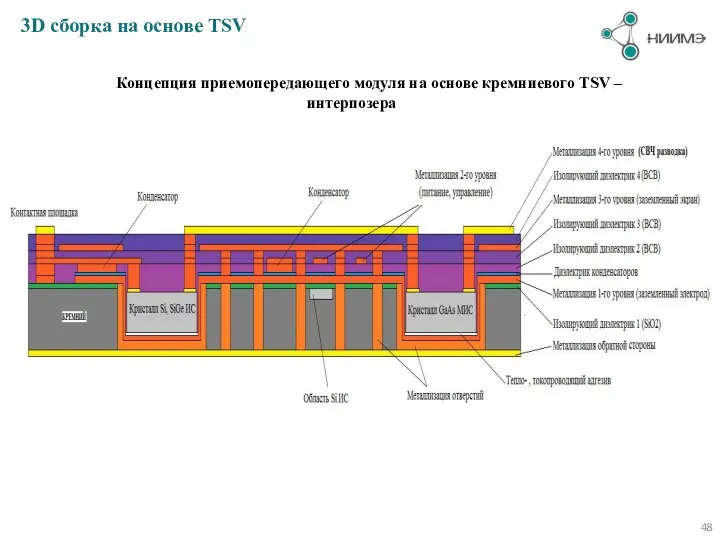

- 48. 3D сборка на основе TSV Концепция приемопередающего модуля на основе кремниевого TSV – интерпозера

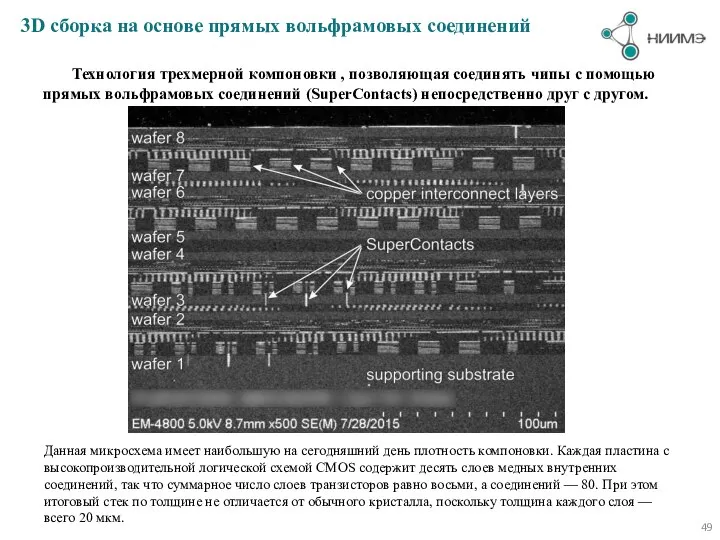

- 49. 3D сборка на основе прямых вольфрамовых соединений Технология трехмерной компоновки , позволяющая соединять чипы с помощью

- 51. Скачать презентацию

Ручная набойка на ткани

Ручная набойка на ткани Задачи по теме: «Обыкновенные дроби» 5 класс Учитель математики Артамонова Л.В., МКОУ «Москаленский лицей»

Задачи по теме: «Обыкновенные дроби» 5 класс Учитель математики Артамонова Л.В., МКОУ «Москаленский лицей»  Разработка комплекса маркетинга товара

Разработка комплекса маркетинга товара Дискретное преобразование Фурье Обратное пространство. Фурье-преобразование. Быстрое фурье-преобразование

Дискретное преобразование Фурье Обратное пространство. Фурье-преобразование. Быстрое фурье-преобразование MS Access vs MS Excel. Құжат типін анықтау

MS Access vs MS Excel. Құжат типін анықтау Рисунок головы

Рисунок головы Основы оказания первой помощи на поиске, юридические аспекты, базовые алгоритмы. ПО «Лиза Алерт»

Основы оказания первой помощи на поиске, юридические аспекты, базовые алгоритмы. ПО «Лиза Алерт» Начертательная геометрия

Начертательная геометрия Политическая система общества

Политическая система общества Презентация "Светлая Пасхальная Седмица: традиции и обычаи" - скачать презентации по МХК

Презентация "Светлая Пасхальная Седмица: традиции и обычаи" - скачать презентации по МХК Выставочнй зал "Романтичное Болдино". Парк "Четыре времени года"

Выставочнй зал "Романтичное Болдино". Парк "Четыре времени года" Общие сведения о деталях машин

Общие сведения о деталях машин Системы менеджмента качества

Системы менеджмента качества Конный завод «Ахалтекинец»

Конный завод «Ахалтекинец» Содержание права собственности на землю Выполнили студентки группы Ю-103 Пустовая Анастасия и Мятлик Елена.

Содержание права собственности на землю Выполнили студентки группы Ю-103 Пустовая Анастасия и Мятлик Елена. Особенности празднования Нового Года

Особенности празднования Нового Года Преимущества и недостатки объектно-ориентированного программирования (ООП)

Преимущества и недостатки объектно-ориентированного программирования (ООП) Қазақстан Республикасының ішкі саясаты

Қазақстан Республикасының ішкі саясаты вывеска

вывеска Проект реконструкции сервисного центра по обслуживанию автовладельцев г. Великий Новгород. Разработка услуги по тюнингу салона

Проект реконструкции сервисного центра по обслуживанию автовладельцев г. Великий Новгород. Разработка услуги по тюнингу салона Женщина и карьера

Женщина и карьера Общие сведения о TCP/IP

Общие сведения о TCP/IP Презентация "Декоративно-прикладное искусство" - скачать презентации по МХК_

Презентация "Декоративно-прикладное искусство" - скачать презентации по МХК_ Городская культура Токио

Городская культура Токио Предварительная подготовка к выезду

Предварительная подготовка к выезду Зонты Выполнила: Митюшова, Александра Реклама, 303 группа

Зонты Выполнила: Митюшова, Александра Реклама, 303 группа ЛЕКЦИЯ № 3 ТЕМА: АНТРОПОЛОГИЧЕСКИЕ ПРИЗНАКИ ЧЕЛОВЕКА

ЛЕКЦИЯ № 3 ТЕМА: АНТРОПОЛОГИЧЕСКИЕ ПРИЗНАКИ ЧЕЛОВЕКА  ОРГАНИЗАЦИЯ ВОСПИТАТЕЛЬНОГО ПРОСТРАНСТВА В ШКОЛЕ-ИНТЕРНАТЕ

ОРГАНИЗАЦИЯ ВОСПИТАТЕЛЬНОГО ПРОСТРАНСТВА В ШКОЛЕ-ИНТЕРНАТЕ