Содержание

- 2. 4096tb@gmail.com Тема письма: БГУИР. … . Ковалевский Вячеслав Викторович

- 3. Лекция 5. Структура процессора. Архитектуры CISC и RISC. Архитектура процессора Intel . План лекции: Структура процессора.

- 4. Лекция 6. Адресация. Режимы работы процессора. Управление памятью. План лекции: Адресация памяти. Непосредственная, прямая и косвенная

- 5. Общие сведения о микропроцессорах

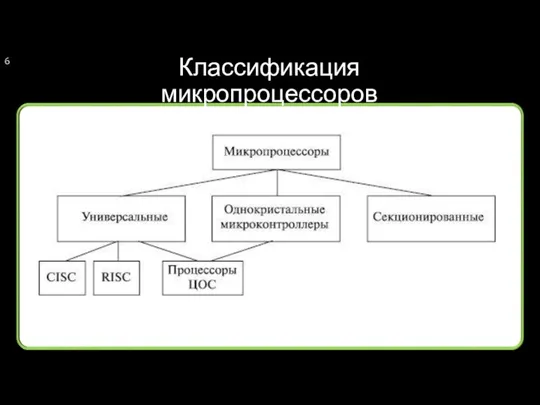

- 6. Классификация микропроцессоров

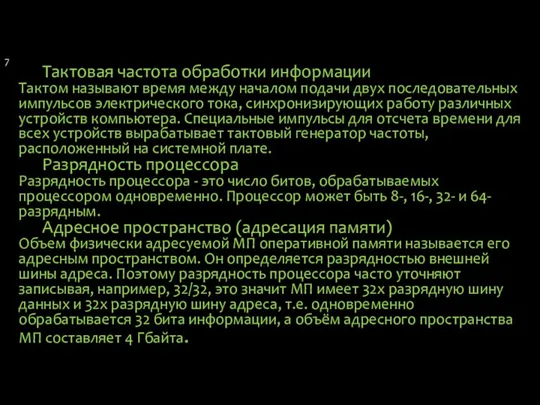

- 7. Тактовая частота обработки информации Тактом называют время между началом подачи двух последовательных импульсов электрического тока, синхронизирующих

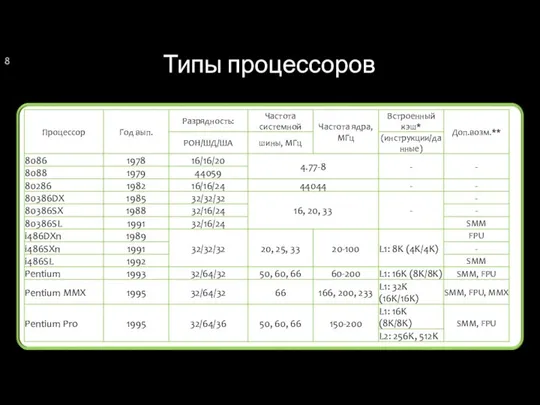

- 8. Типы процессоров

- 9. Типы процессоров * Pentium II/III Xeon выпускаются с L2 кэшем до 2M. У Pentium 4: вместо

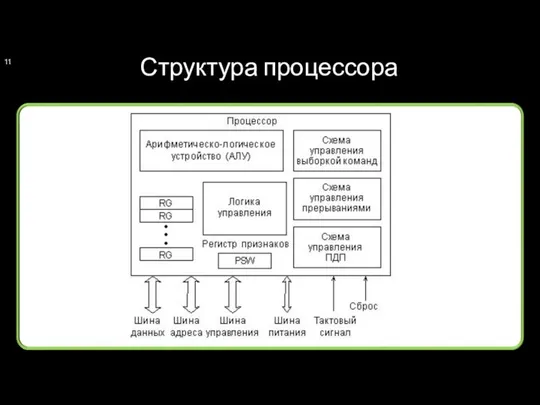

- 10. Структура процессора

- 11. Структура процессора

- 12. Структура процессора Intel 4004

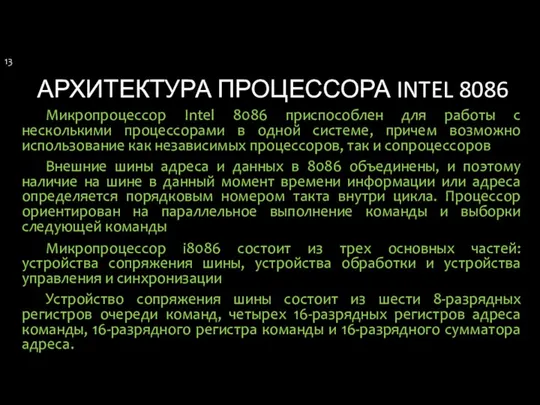

- 13. АРХИТЕКТУРА ПРОЦЕССОРА INTEL 8086 Микропроцессор Intel 8086 приспособлен для работы с несколькими процессорами в одной системе,

- 14. Структура процессора Intel 8086

- 15. ПРОГРАММНАЯ МОДЕЛЬ ПРОЦЕССОРА 8086 Программная модель процессора - это функциональная модель, используемая программистом при разработке программ

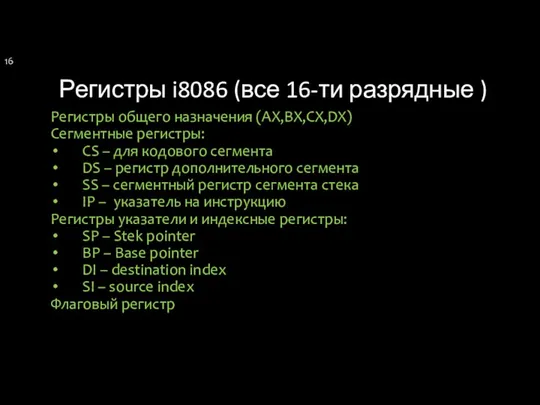

- 16. Регистры i8086 (все 16-ти разрядные ) Регистры общего назначения (AX,BX,CX,DX) Сегментные регистры: CS – для кодового

- 17. Регистры i8086 Регистры общего назначения Восемь регистров общего назначения процессора 8086 (каждый разрядностью 16 бит) используются

- 18. Регистр AX всегда используется в операциях умножения или деления и является также одним из тех регистров,

- 19. Регистр SI может использоваться, как указатель на ячейку памяти. Регистр DI его можно использовать в качестве

- 20. Сегментные регистры. Основной предпосылкой сегментации является следующее: процессор 8086 может адресоваться к 1 мегабайту памяти. Для

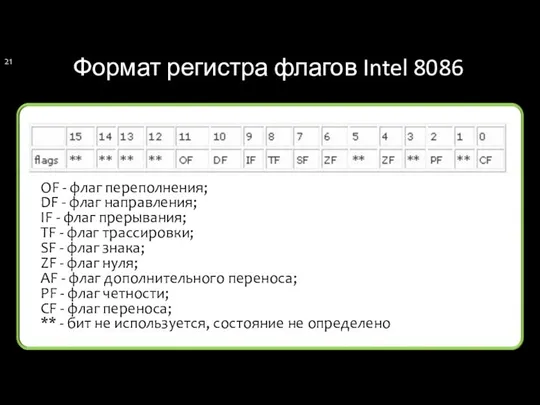

- 21. Формат регистра флагов Intel 8086 OF - флаг переполнения; DF - флаг направления; IF - флаг

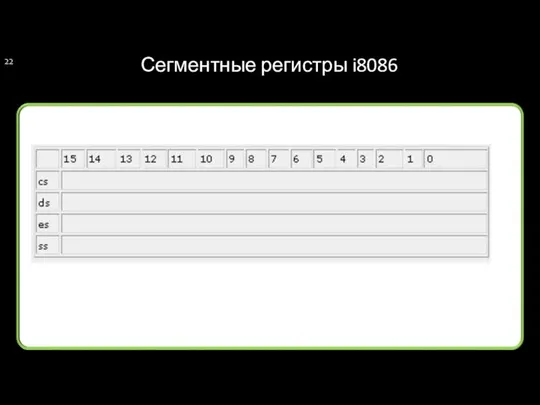

- 22. Сегментные регистры i8086

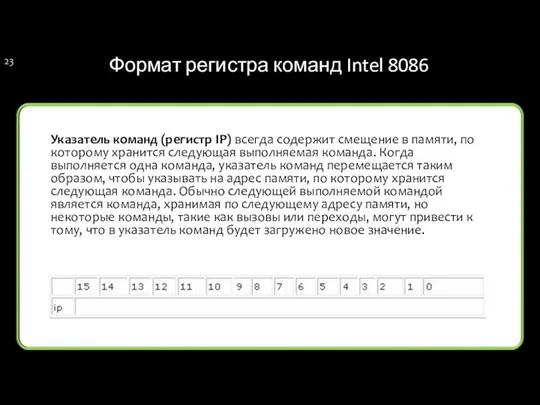

- 23. Формат регистра команд Intel 8086 Указатель команд (регистр IP) всегда содержит смещение в памяти, по которому

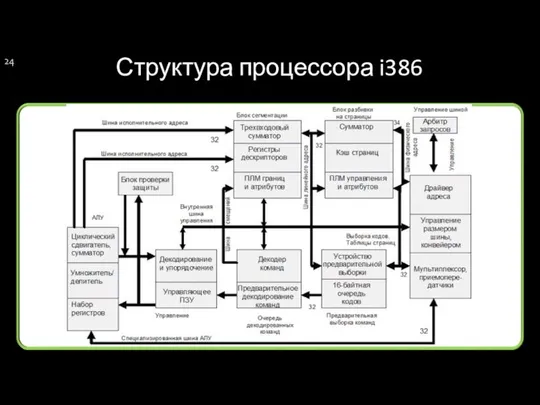

- 24. Структура процессора i386

- 25. Регистры процессора i386

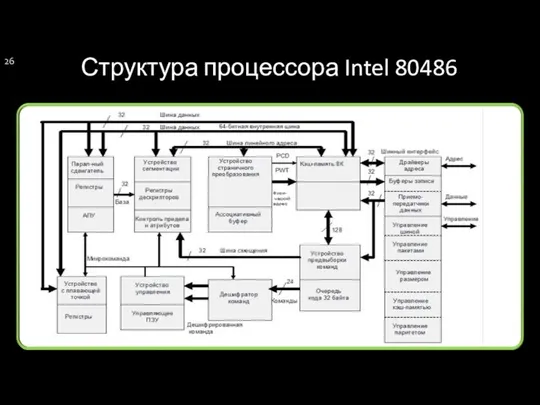

- 26. Структура процессора Intel 80486

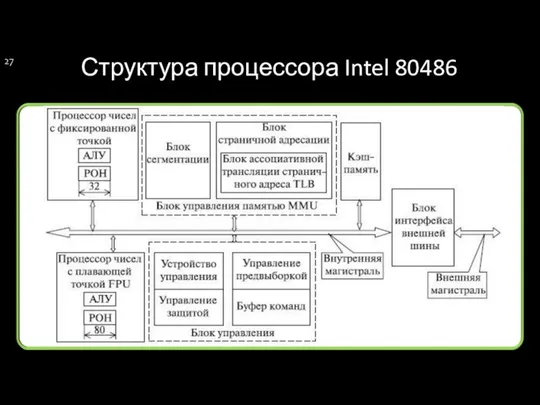

- 27. Структура процессора Intel 80486

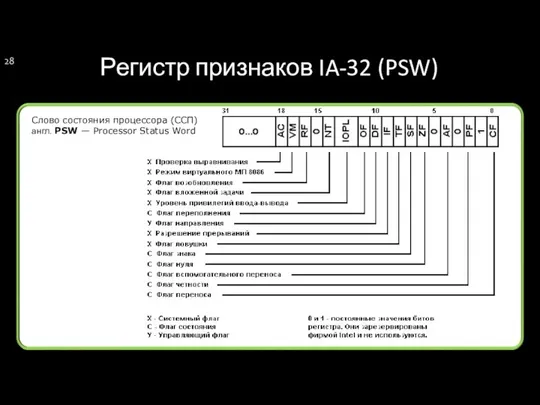

- 28. Регистр признаков IA-32 (PSW) Cлово состояния процессора (ССП) англ. PSW — Processor Status Word

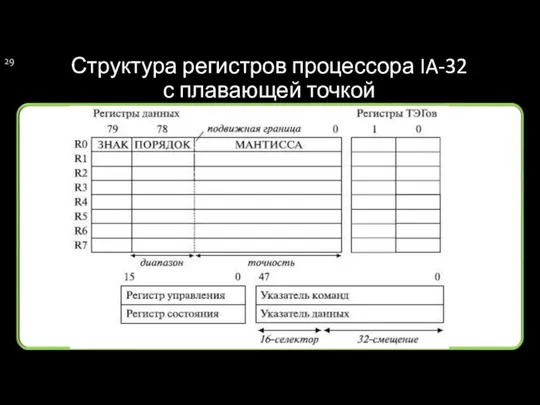

- 29. Структура регистров процессора IA-32 с плавающей точкой

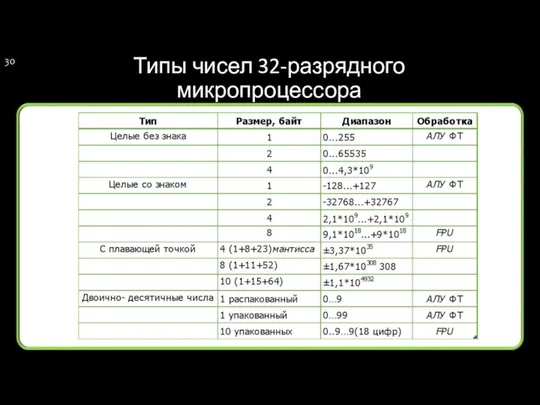

- 30. Типы чисел 32-разрядного микропроцессора

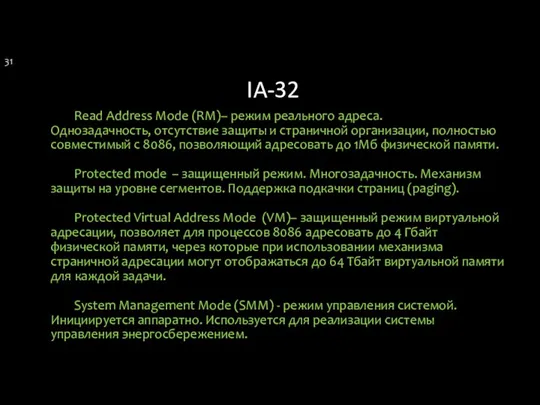

- 31. IA-32 Read Address Mode (RM)– режим реального адреса. Однозадачность, отсутствие защиты и страничной организации, полностью совместимый

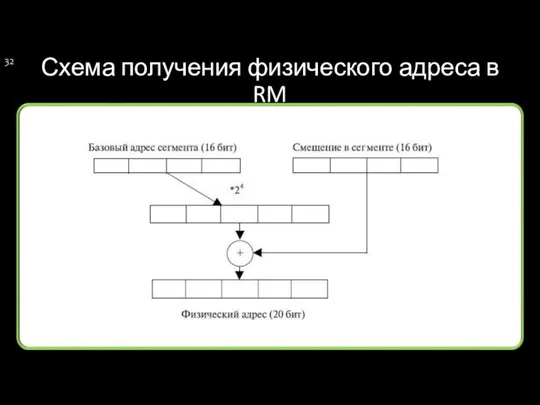

- 32. Схема получения физического адреса в RM

- 33. Структура регистров системных адресов и системных сегментов (PM)

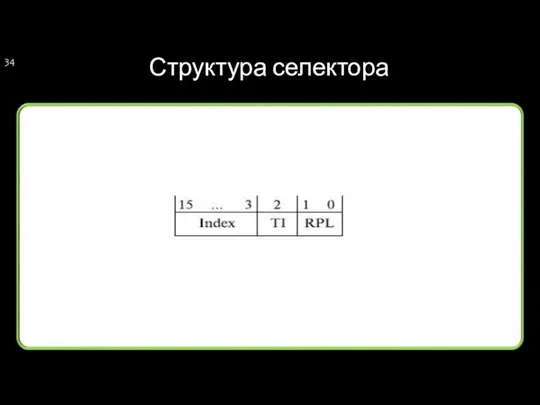

- 34. Структура селектора

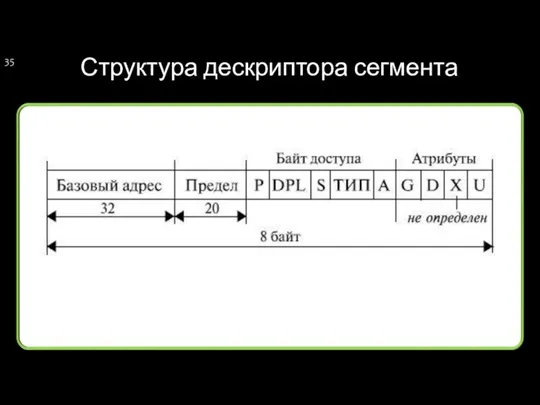

- 35. Структура дескриптора сегмента

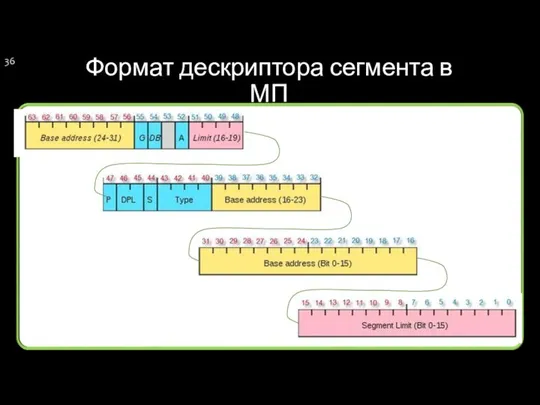

- 36. Формат дескриптора сегмента в МП

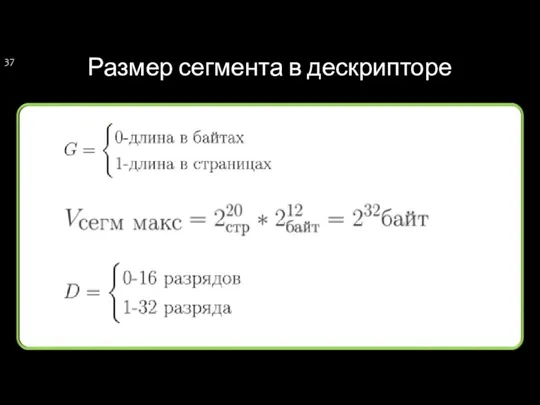

- 37. Размер сегмента в дескрипторе

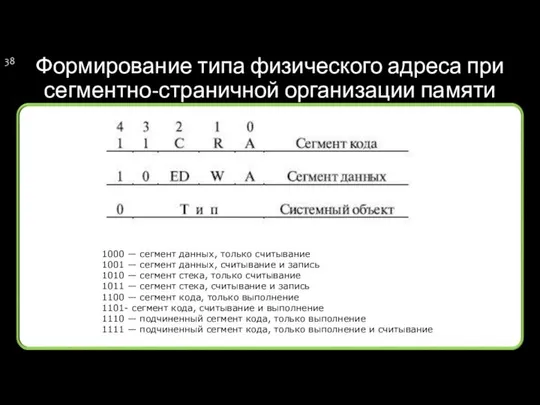

- 38. Формирование типа физического адреса при сегментно-страничной организации памяти 1000 — сегмент данных, только считывание 1001 —

- 39. Формат команды микропроцессора IA-32

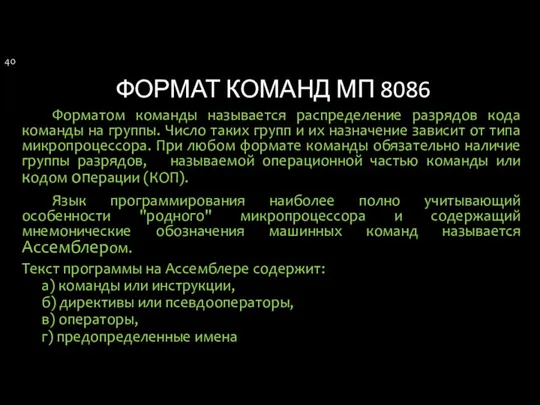

- 40. ФОРМАТ КОМАНД МП 8086 Форматом команды называется распределение разрядов кода команды на группы. Число таких групп

- 41. ФОРМАТ КОМАНД МП 8086 Действия обусловленные операциями перечисленными в пп. б),в),г) предыдущего слайда выполняются на этапе

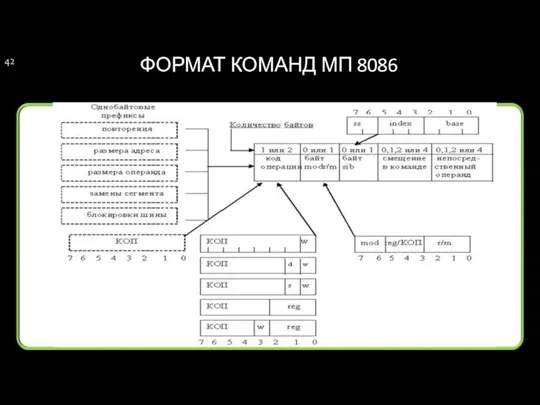

- 42. ФОРМАТ КОМАНД МП 8086

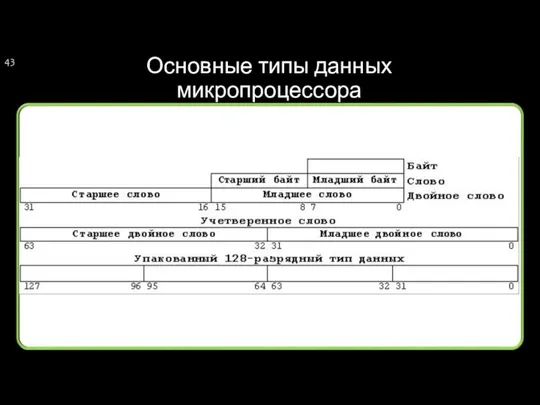

- 43. Основные типы данных микропроцессора

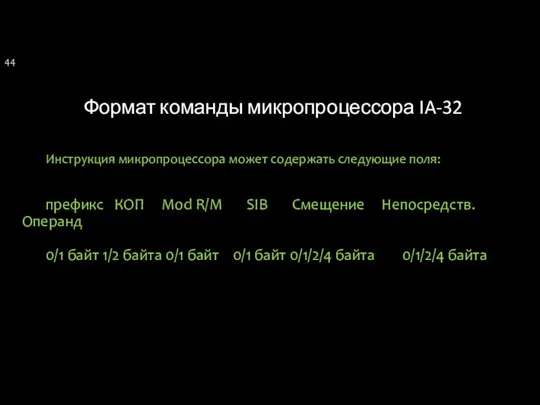

- 44. Формат команды микропроцессора IA-32 Инструкция микропроцессора может содержать следующие поля: префикс КОП Mod R/M SIB Смещение

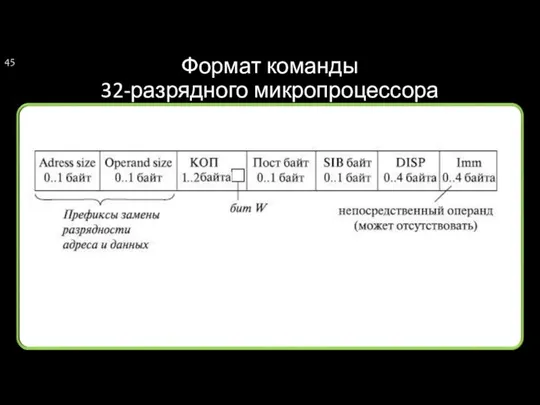

- 45. Формат команды 32-разрядного микропроцессора

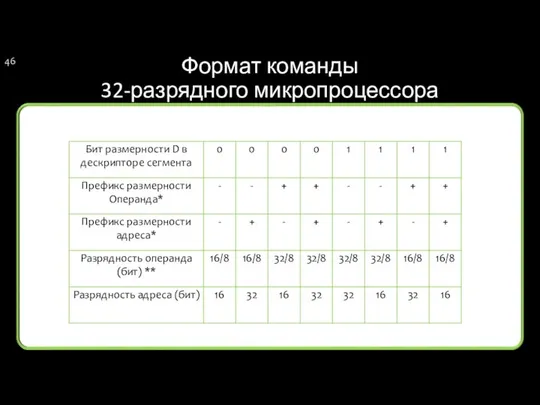

- 46. Формат команды 32-разрядного микропроцессора

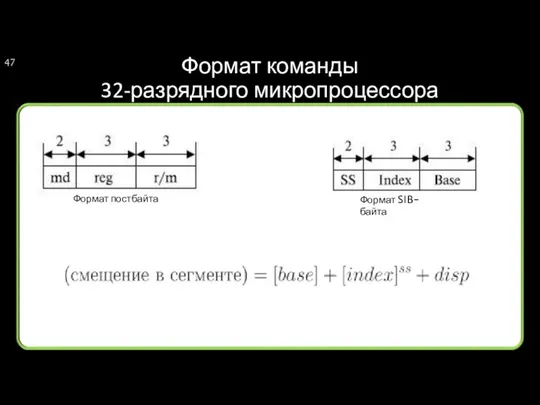

- 47. Формат команды 32-разрядного микропроцессора Формат постбайта Формат SIB-байта

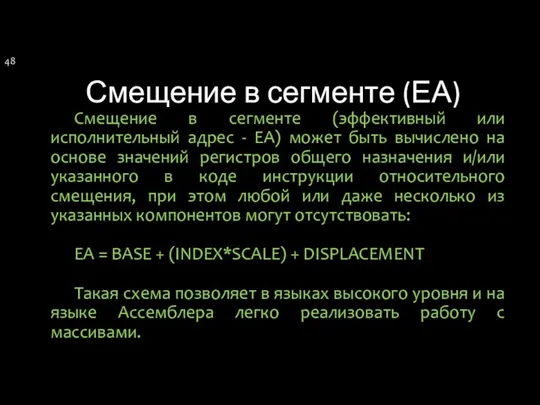

- 48. Смещение в сегменте (ЕА) Смещение в сегменте (эффективный или исполнительный адрес - ЕА) может быть вычислено

- 49. Методы адресации

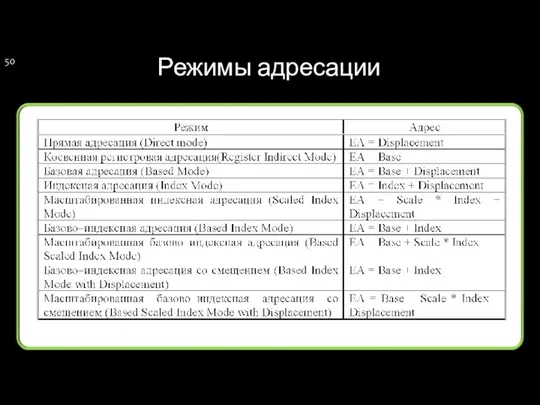

- 50. Режимы адресации

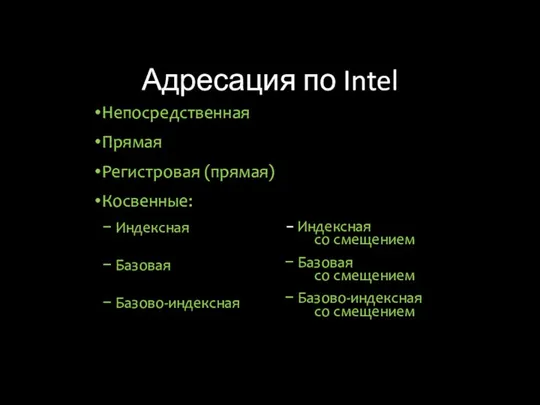

- 51. Адресация по Intel Непосредственная Прямая Регистровая (прямая) Косвенные: Индексная Базовая Базово-индексная Индексная со смещением Базовая со

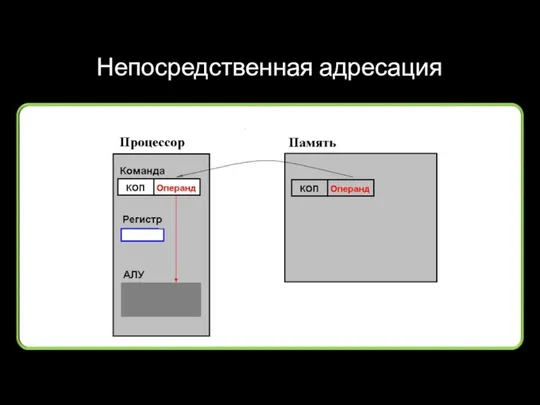

- 52. Непосредственная адресация

- 53. Прямая адресация

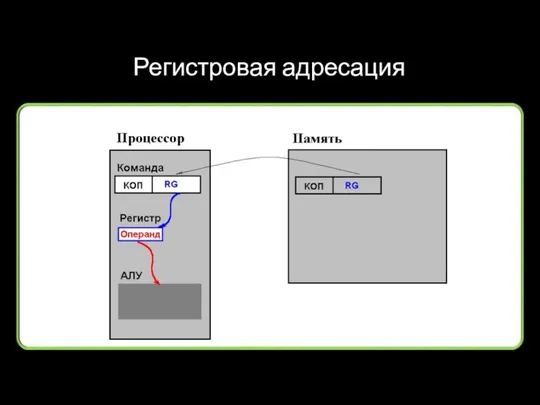

- 54. Регистровая адресация

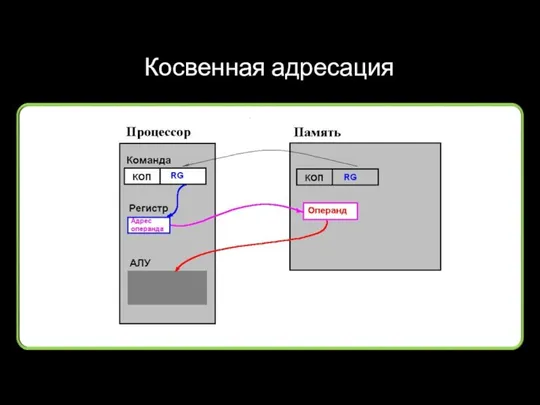

- 55. Косвенная адресация

- 56. Сегментная адресация памяти

- 57. Описание сегментов в таблицах дескрипторов Формат селектора

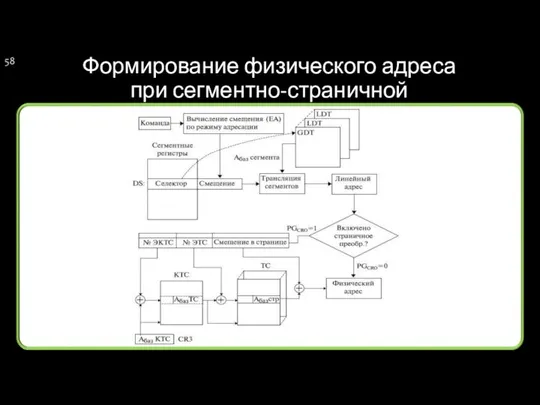

- 58. Формирование физического адреса при сегментно-страничной организации памяти

- 59. Формирование физического адреса при сегментно-страничной организации (Часть 1) памяти

- 60. Формирование физического адреса при сегментно-страничной организации (Часть 2) памяти

- 61. Получение дескриптора, находящегося в глобальной таблице дескрипторов GDT Формат селектора

- 62. Получение дескриптора, находящегося в локальной таблице дескрипторов LDT Формат селектора

- 63. получения адреса операнда на примере команды MOV EAX, [ECX+ESI+20h] селектор по умолчанию находится в сегментном регистре

- 64. Виртуальная адресация памяти

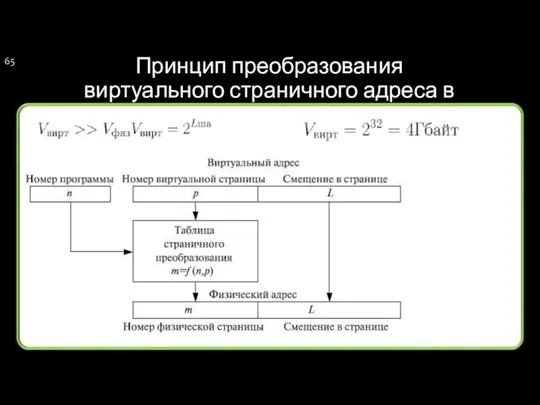

- 65. Принцип преобразования виртуального страничного адреса в физический

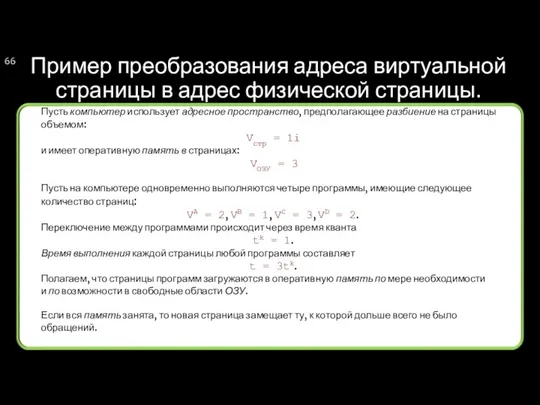

- 66. Пример преобразования адреса виртуальной страницы в адрес физической страницы. Пусть компьютер использует адресное пространство, предполагающее разбиение

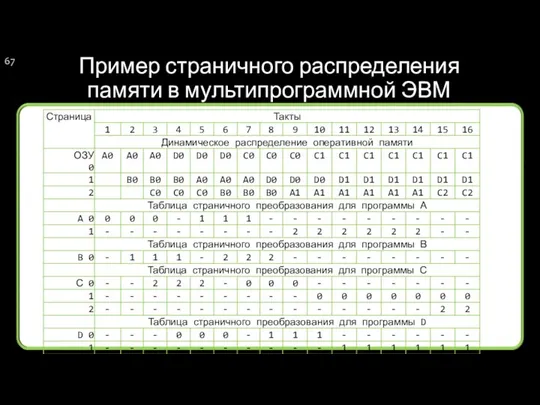

- 67. Пример страничного распределения памяти в мультипрограммной ЭВМ

- 68. Страничное преобразование линейного адреса в физический

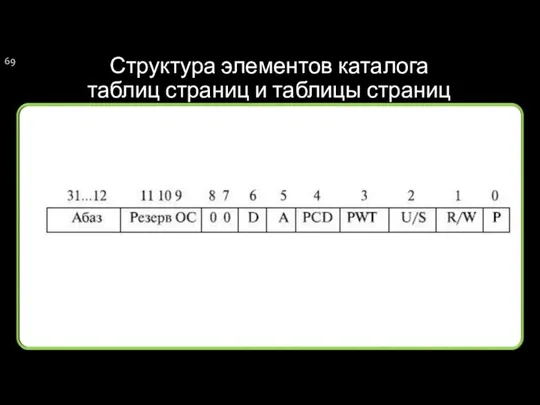

- 69. Структура элементов каталога таблиц страниц и таблицы страниц

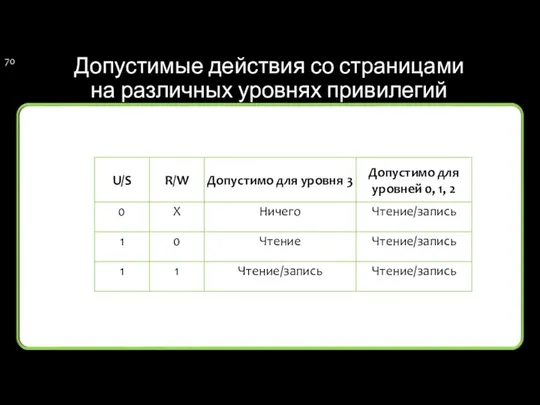

- 70. Допустимые действия со страницами на различных уровнях привилегий

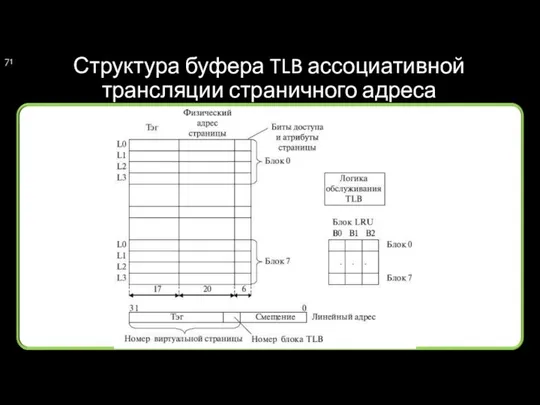

- 71. Структура буфера TLB ассоциативной трансляции страничного адреса

- 72. Формат строки модуля основной памяти TLB

- 73. Порядок изменения бит в строке LRU

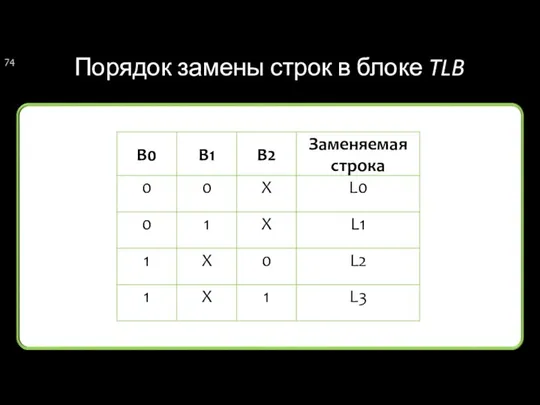

- 74. Порядок замены строк в блоке TLB

- 75. Механизмы защиты памяти

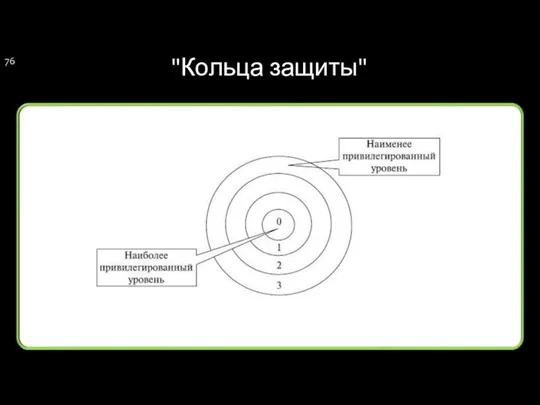

- 76. "Кольца защиты"

- 77. Порядок взаимодействия программ и данных на разных уровнях привилегий

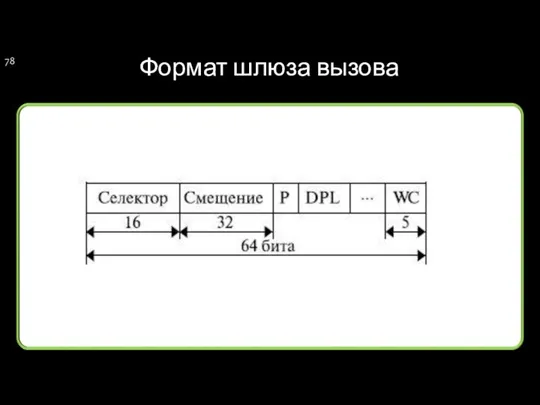

- 78. Формат шлюза вызова

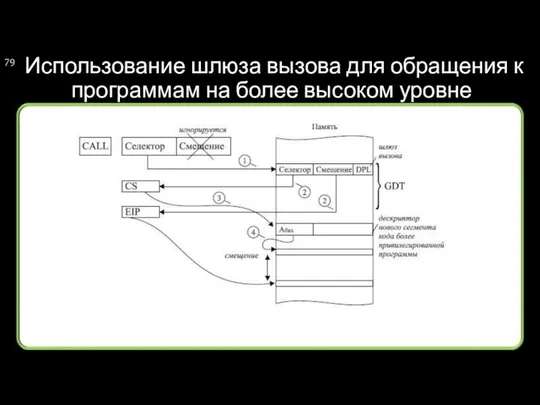

- 79. Использование шлюза вызова для обращения к программам на более высоком уровне привилегий

- 80. Последовательное обращение к более привилегированным программам

- 81. Литература: 1. https://www.dropbox.com/s/gmebqjp8sc3jbfj/Arkhitektura_kompyutera_6-e_izdanie.djvu?dl=0 2. https://www.dropbox.com/s/7sescv0sx9nggqj/Lit.Lec.6.docx?dl=0

- 83. Скачать презентацию

![получения адреса операнда на примере команды MOV EAX, [ECX+ESI+20h] селектор по](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/621712/slide-62.jpg)

Операционные системы

Операционные системы База контактов экспертов

База контактов экспертов Презентация "«Информационные системы»" - скачать презентации по Информатике

Презентация "«Информационные системы»" - скачать презентации по Информатике Интернет-Олимпиады по программированию подготовила Савина Елена Геннадьевна, учитель МОУ « Березовская СОШ» П Канифольный, Ни

Интернет-Олимпиады по программированию подготовила Савина Елена Геннадьевна, учитель МОУ « Березовская СОШ» П Канифольный, Ни Переход на межведомственное электронное взаимодействие на территории Ямало-ненецкого автономного округа

Переход на межведомственное электронное взаимодействие на территории Ямало-ненецкого автономного округа Программная инженерия. Лекция 2

Программная инженерия. Лекция 2 Форматирование абзацев (выравнивание, отступ первой строки и др.). Создание и форматирование списков

Форматирование абзацев (выравнивание, отступ первой строки и др.). Создание и форматирование списков Объектно-ориентированное программирование в С++. Классы

Объектно-ориентированное программирование в С++. Классы Библиотека имени М.Горького

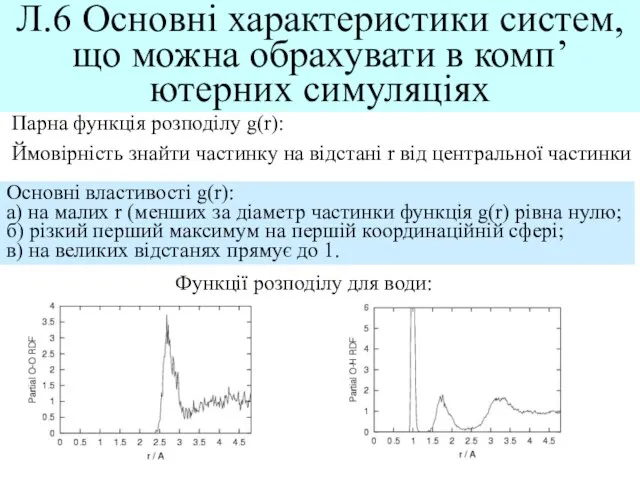

Библиотека имени М.Горького Основні характеристики систем, що можна обрахувати в комп’ютерних симуляціях

Основні характеристики систем, що можна обрахувати в комп’ютерних симуляціях Разработка программного модуля электронной подписи файлов

Разработка программного модуля электронной подписи файлов Преобразование двумерных массивов: обмен, удаление, вставка строк и столбцов Учитель информатики: Никишева Анастасия Витальев

Преобразование двумерных массивов: обмен, удаление, вставка строк и столбцов Учитель информатики: Никишева Анастасия Витальев Презентация "Печатающие устройства." - скачать презентации по Информатике_

Презентация "Печатающие устройства." - скачать презентации по Информатике_ Рассмотрение проектной документации по объекту: Строительство низконапорного водовода сточной воды

Рассмотрение проектной документации по объекту: Строительство низконапорного водовода сточной воды Создание и продвижение Интернетпредставительства организации

Создание и продвижение Интернетпредставительства организации Разработка утилит для скрытой периодической процедуры очистки персональных компьютеров от ненужных данных

Разработка утилит для скрытой периодической процедуры очистки персональных компьютеров от ненужных данных Теория автоматов. Определение конечного автомата

Теория автоматов. Определение конечного автомата Разработка интернет-магазина компьютерной и электронной техники

Разработка интернет-магазина компьютерной и электронной техники В мире кодов QR код

В мире кодов QR код Физическая модель базы данных

Физическая модель базы данных Биты и байты

Биты и байты Государственная информационная политика Германии

Государственная информационная политика Германии Разработка сайтов

Разработка сайтов Построение запросов. Язык SQL. 2

Построение запросов. Язык SQL. 2 Программирование на языке Python

Программирование на языке Python Информационные ресурсы корпоративных информационных систем

Информационные ресурсы корпоративных информационных систем Создание библиотеки сайта. Урок №21

Создание библиотеки сайта. Урок №21 Обработка числовых данных. Электронные таблицы

Обработка числовых данных. Электронные таблицы