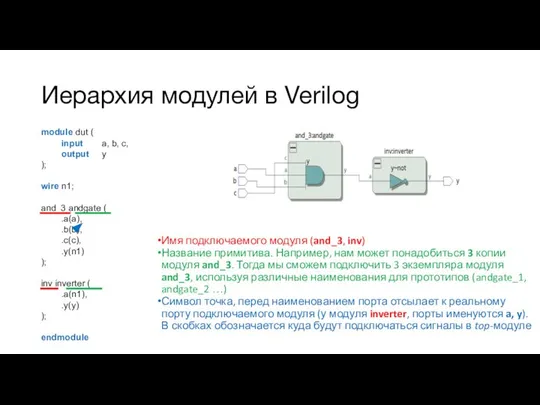

module dut (

input a, b, c,

output y

);

wire n1;

and_3 andgate (

.a(a),

.b(b),

.c(c),

.y(n1)

);

inv inverter (

.a(n1),

.y(y)

);

endmodule

Иерархия

модулей в Verilog

Имя подключаемого модуля (and_3, inv)

Название примитива. Например, нам может понадобиться 3 копии модуля and_3. Тогда мы сможем подключить 3 экземпляра модуля and_3, используя различные наименования для прототипов (andgate_1, andgate_2 …)

Символ точка, перед наименованием порта отсылает к реальному порту подключаемого модуля (у модуля inverter, порты именуются a, y). В скобках обозначается куда будут подключаться сигналы в top-модуле

![module ALU_RISCV ( input [4:0] ALUOp, input [31:0] A, input [31:0]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/791826/slide-15.jpg)

![CASE module mux ( input [3:0] d0, d1, d2, d3, input](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/791826/slide-19.jpg)

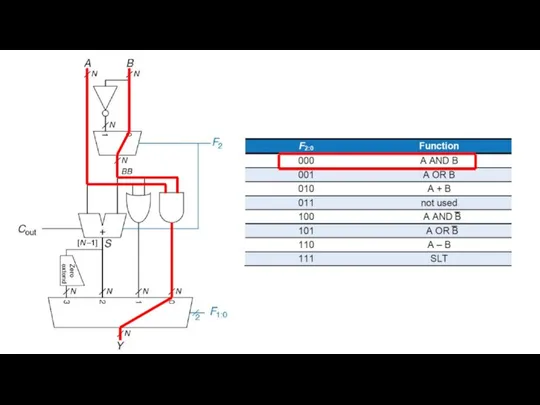

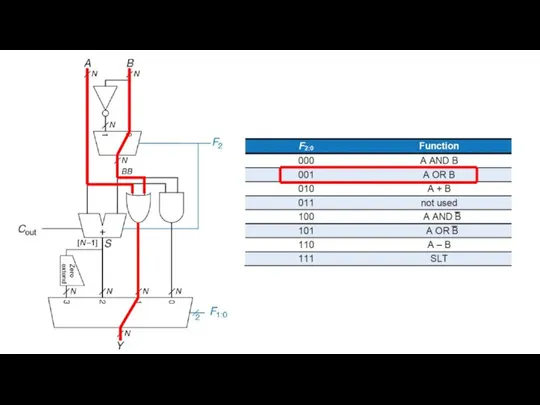

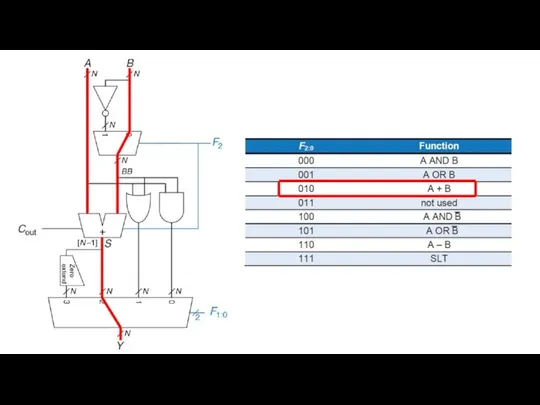

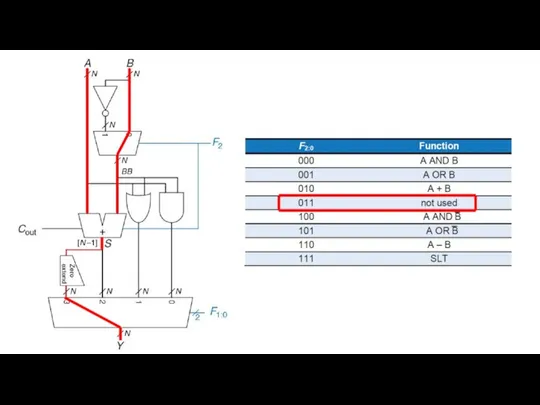

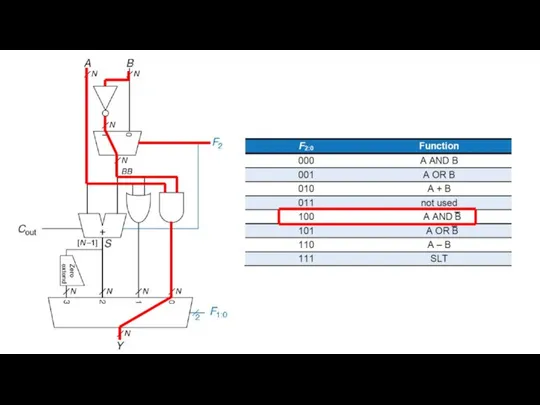

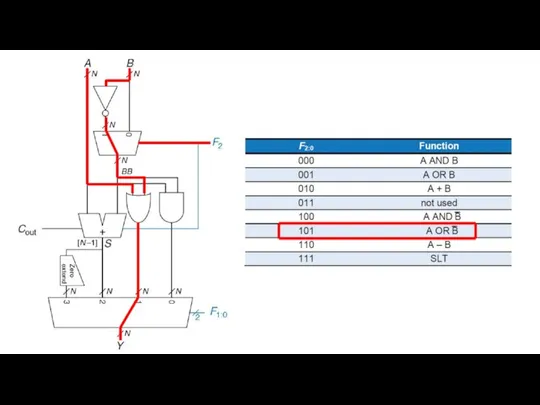

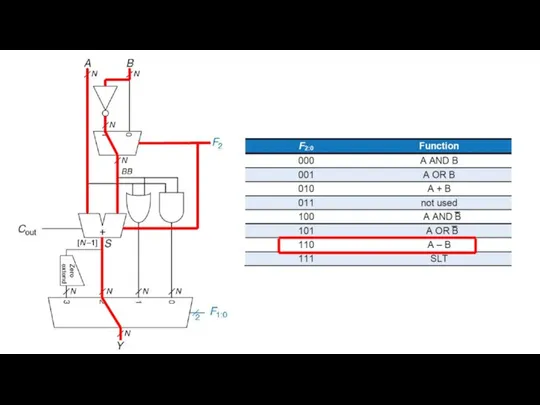

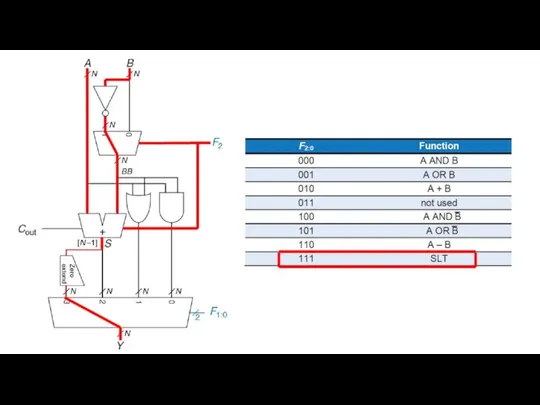

Открытая архитектура и экосистема RISC-V

Открытая архитектура и экосистема RISC-V Информационные технологии

Информационные технологии Чарльз Бэббидж

Чарльз Бэббидж Презентация "Кодирование информации" - скачать презентации по Информатике

Презентация "Кодирование информации" - скачать презентации по Информатике Электронная почта и другие сервисы компьютерных сетей

Электронная почта и другие сервисы компьютерных сетей Регистрация. ИСТИНА. Интеллектуальная система тематического исследования научно-технической информации

Регистрация. ИСТИНА. Интеллектуальная система тематического исследования научно-технической информации Подготовка к ЕГЭ-2013 по теме: «Перебор слов и системы счисления»

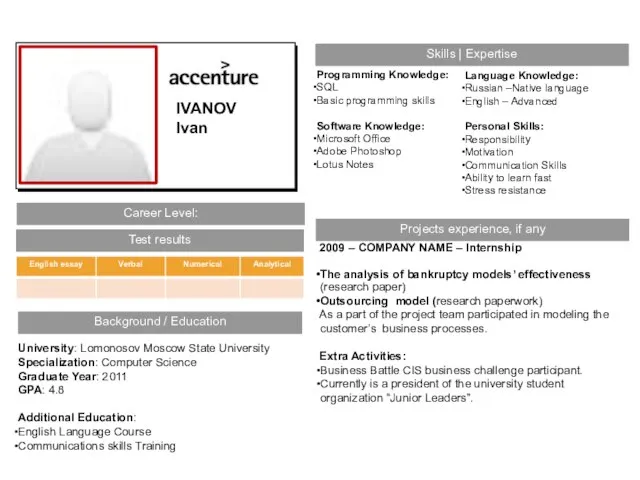

Подготовка к ЕГЭ-2013 по теме: «Перебор слов и системы счисления» Basic programming skills

Basic programming skills Работа с Power Point

Работа с Power Point Тарифный модификатор по подбору организаций

Тарифный модификатор по подбору организаций Хмарна АТС (V-PBX). Найсучасна послуга від ПАТ Укртелеком

Хмарна АТС (V-PBX). Найсучасна послуга від ПАТ Укртелеком Системная среда Windows Презентация подготовлена ученицей 7 «Б» класса МБ ОУО гимназии №30 Михайловой Ксении

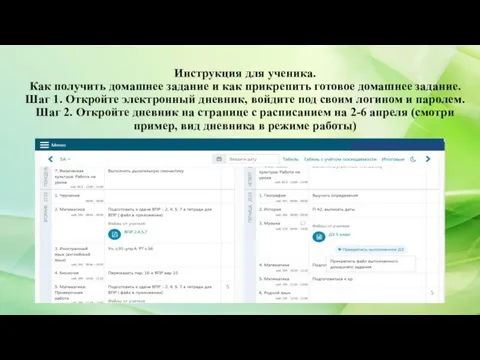

Системная среда Windows Презентация подготовлена ученицей 7 «Б» класса МБ ОУО гимназии №30 Михайловой Ксении  Инструкция для ученика. Как получить домашнее задание и как прикрепить готовое домашнее задание. Шаг 1

Инструкция для ученика. Как получить домашнее задание и как прикрепить готовое домашнее задание. Шаг 1 К/р №4 ИНФО-9 по теме «Редакторы, таблицы, базы данных» 4

К/р №4 ИНФО-9 по теме «Редакторы, таблицы, базы данных» 4 Презентация "ОРГАНИЗАЦИЯ ЛОКАЛЬНЫХ СЕТЕЙ" - скачать презентации по Информатике

Презентация "ОРГАНИЗАЦИЯ ЛОКАЛЬНЫХ СЕТЕЙ" - скачать презентации по Информатике Измерение объёма текстовой информации

Измерение объёма текстовой информации Электронные таблицы. Урок № 4 - 5

Электронные таблицы. Урок № 4 - 5 Основные понятия алгебры логики. Логические операции

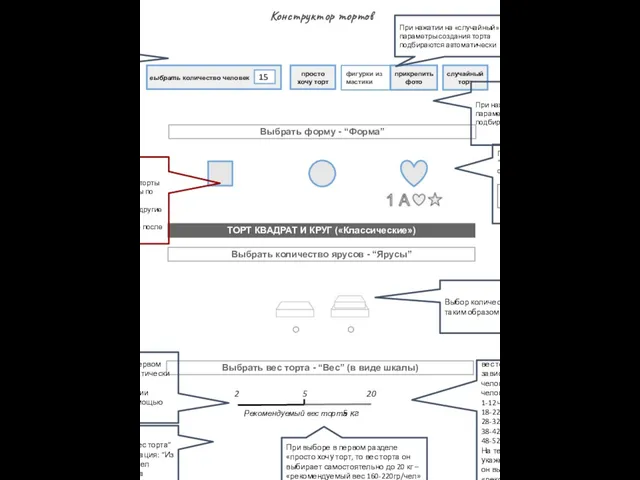

Основные понятия алгебры логики. Логические операции Конструктор тортов

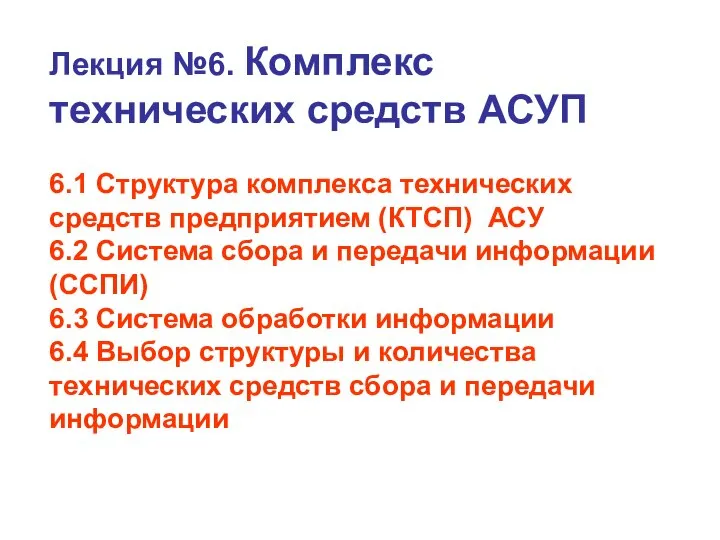

Конструктор тортов Лекция №6. Комплекс технических средств АСУП 6.1 Структура комплекса технических средств предприятием (КТСП) АСУ 6.2 Система сбо

Лекция №6. Комплекс технических средств АСУП 6.1 Структура комплекса технических средств предприятием (КТСП) АСУ 6.2 Система сбо Презентацию выполняла Ученица 8«В» класса Демященкова Анастасия

Презентацию выполняла Ученица 8«В» класса Демященкова Анастасия  Проектирование компьютерной сети для ООО СТЭЛС

Проектирование компьютерной сети для ООО СТЭЛС Правила регистрации доменов

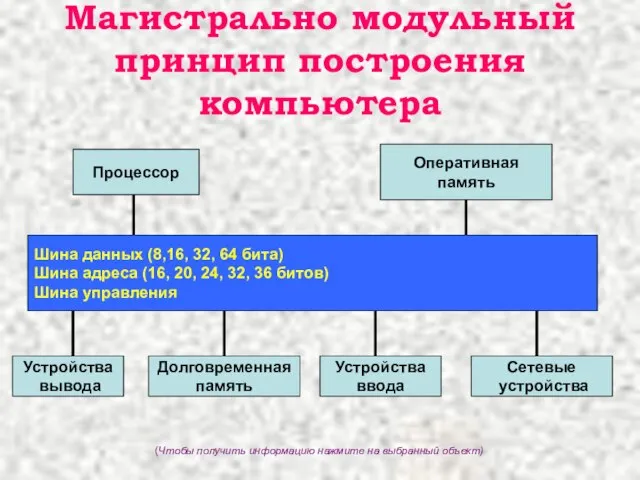

Правила регистрации доменов Магистрально модульный принцип построения компьютера

Магистрально модульный принцип построения компьютера Отношения тождества, подчинения, пересечения

Отношения тождества, подчинения, пересечения Сетевой уровень как средство построения больших сетей

Сетевой уровень как средство построения больших сетей Системы счисления

Системы счисления Computer Architecture

Computer Architecture