Содержание

- 2. Существующие шины ISA – industrial serial architecture EISA PCI - Peripheral Component Interconnect Mini-PCI PCI-X PCI-64

- 3. Определение Системная шина – это критический компонент компьютерной системы, способный соединять другие компоненты в количестве более

- 4. Термины Линия – физический или логический проводник присутствующий в шине Транзакция – цикл передачи данных по

- 5. Типы системных шин: по устройствам Шина процессор-память (северный мост) Маленькая(физически), быстрая По скорость оптимизирована под память

- 6. Типы шин: по организации Выделенные Разные физические линии для данных и адреса Мультиплексированные Физические провода используются

- 7. Объединительные шины

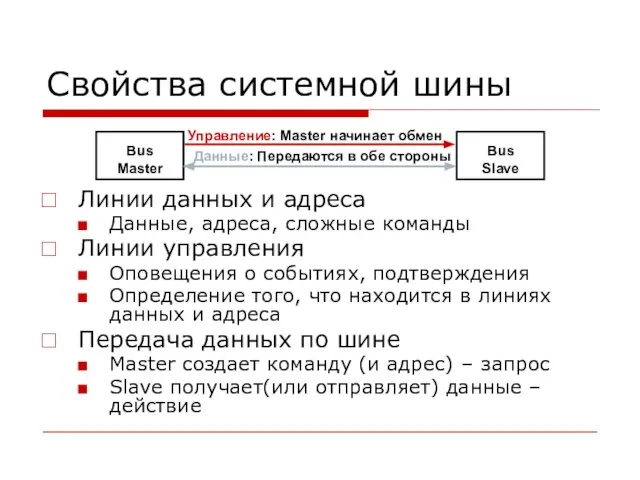

- 8. Свойства системной шины Линии данных и адреса Данные, адреса, сложные команды Линии управления Оповещения о событиях,

- 9. Требования к системной шине Доступность Скорость Надежность Расширяемость Отсутствие узких мест Отсутствие электрического шума Гибкость Легкость

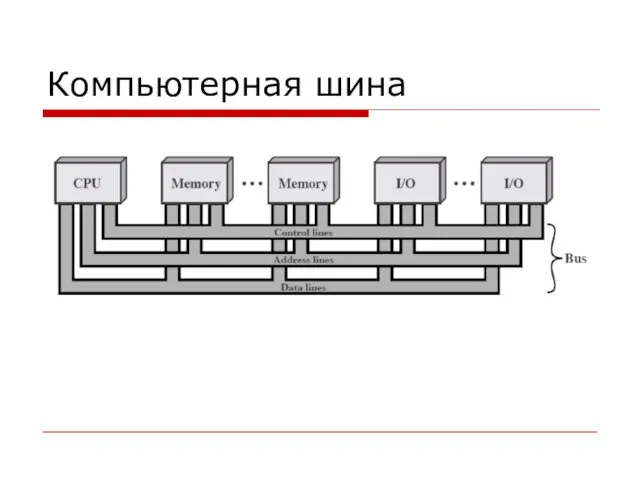

- 10. Компьютерная шина

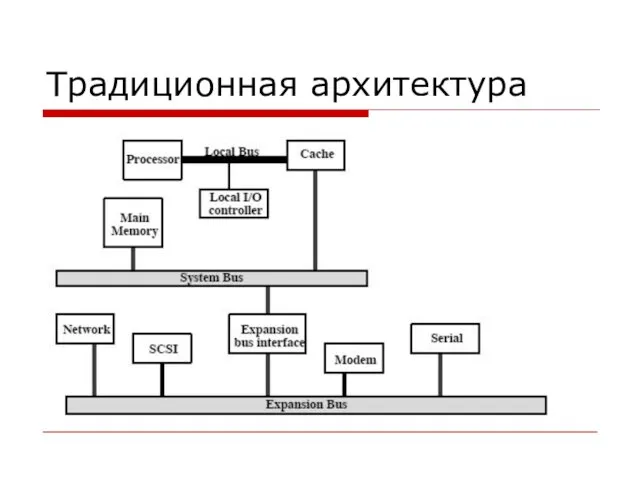

- 11. Традиционная архитектура

- 12. Производительная архитектура

- 13. Рабочая станция

- 14. Серверная система

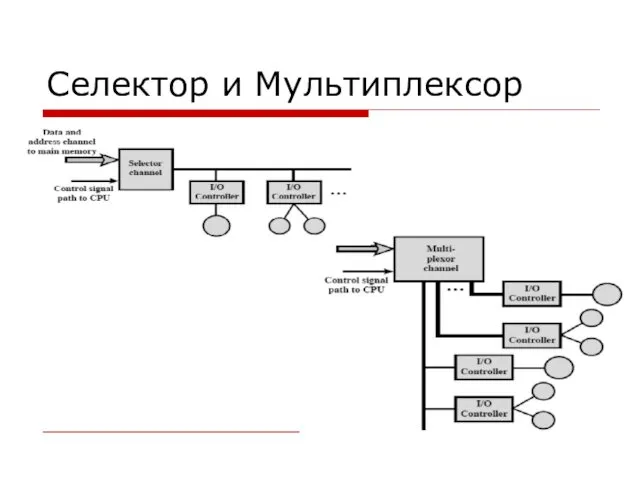

- 15. Селектор и Мультиплексор

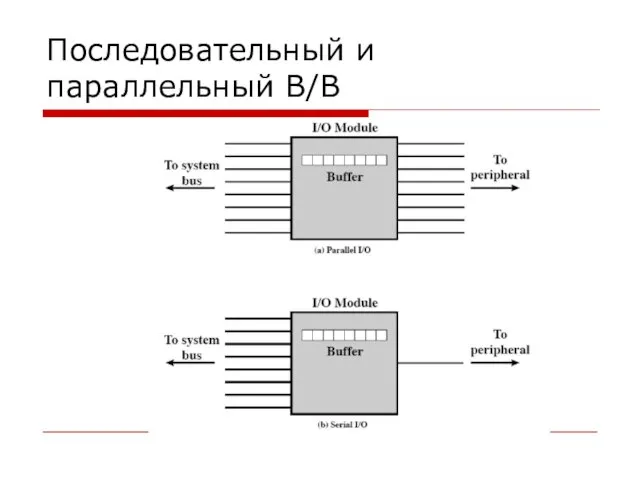

- 16. Последовательный и параллельный В/В

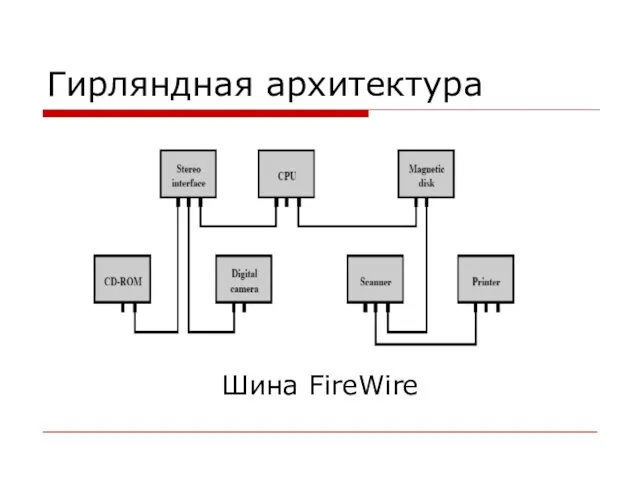

- 17. Гирляндная архитектура Шина FireWire

- 18. Архитектура шины USB: дерево

- 19. Свойства шины Тип работы по времени Асинхронная Синхронная Наличие выделенного DMA Memory Read / Writes I/O

- 20. Синхронные VS. асинхронные Синхронная шина (процессор-память) В линиях управления есть таймер и протокол привязан к таймеру

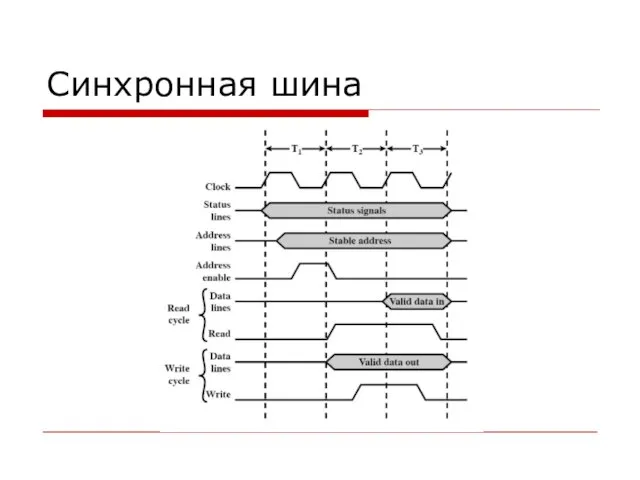

- 21. Синхронная шина

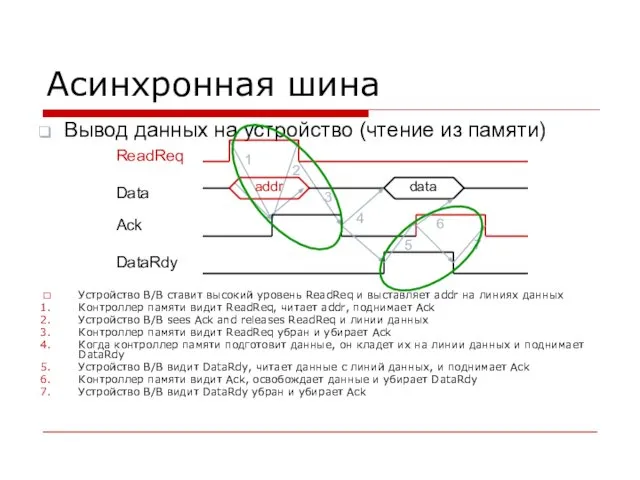

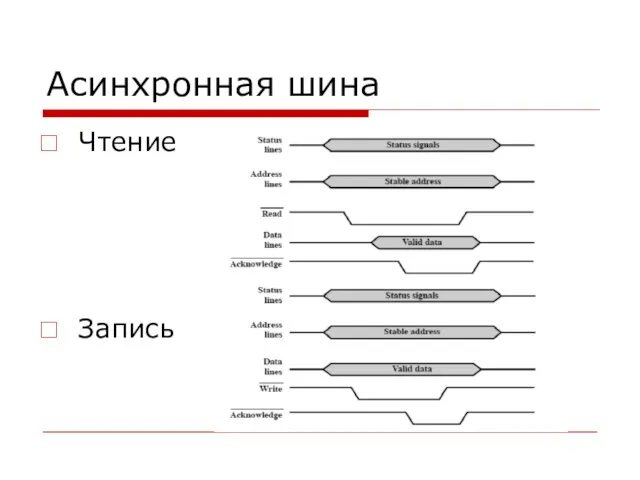

- 22. Асинхронная шина Вывод данных на устройство (чтение из памяти) Устройство В/В ставит высокий уровень ReadReq и

- 23. Асинхронная шина Чтение Запись

- 24. Bus Master Bus Master управляет шиной Чтением Записью Прерываниями запрос/ подтверждение Запрос управления запрос/ подтверждение Зачем

- 25. Как Bus Master работает Нужно передать данные Потенциальный Bus Master может запросить контроль шины На подтверждение

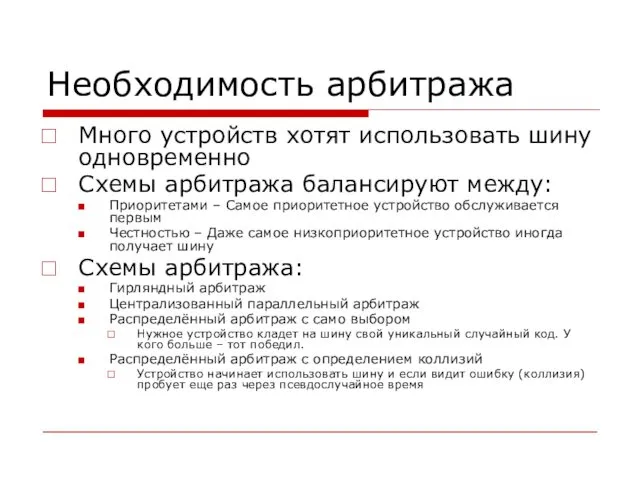

- 26. Необходимость арбитража Много устройств хотят использовать шину одновременно Схемы арбитража балансируют между: Приоритетами – Самое приоритетное

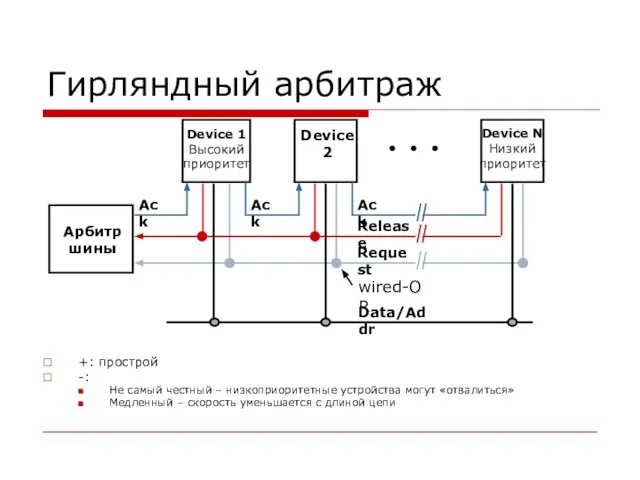

- 27. Гирляндный арбитраж Арбитр шины Device 1 Высокий приоритет Device N Низкий приоритет Device 2 Ack Ack

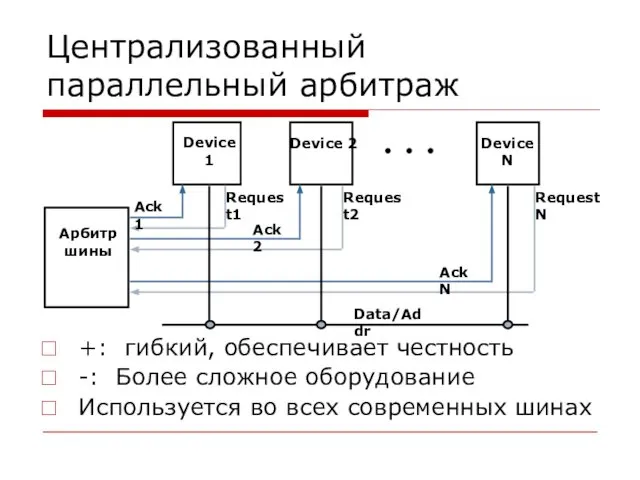

- 28. Централизованный параллельный арбитраж +: гибкий, обеспечивает честность -: Более сложное оборудование Используется во всех современных шинах

- 29. DMA (direct memory access) DMA используется как альтернатива Bus Master для быстрой передачи данных Как работает

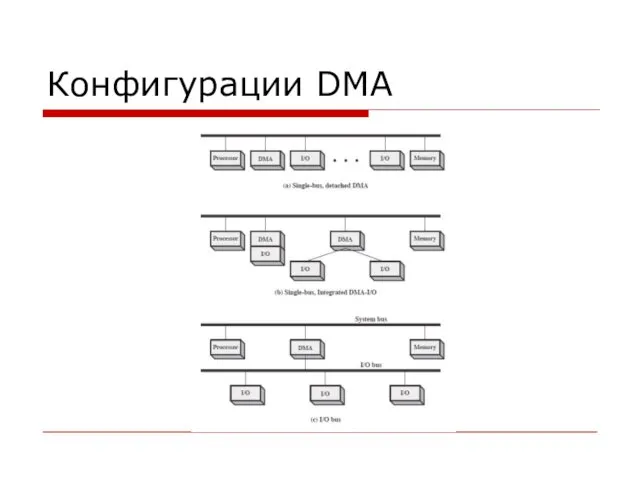

- 30. Конфигурации DMA

- 32. Скачать презентацию

Кодирование информации

Кодирование информации Рост сложности проектов ИС. Предпосылки появления средств автоматизации разработки ИС. Термин CASE

Рост сложности проектов ИС. Предпосылки появления средств автоматизации разработки ИС. Термин CASE Введение в медицинскую информатику. Основы информационных технологий

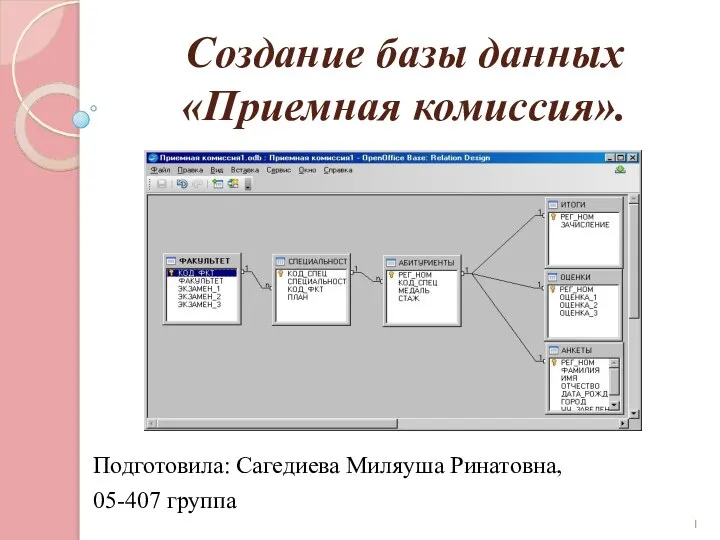

Введение в медицинскую информатику. Основы информационных технологий Создание базы данных «Приемная комиссия»

Создание базы данных «Приемная комиссия» Сравнение видов звукозаписи

Сравнение видов звукозаписи Расчет параметров координированного управления светофорными объектами

Расчет параметров координированного управления светофорными объектами JavaScript - dynamic computer programming language

JavaScript - dynamic computer programming language Основні концепції реляційної бази даних

Основні концепції реляційної бази даних «Базы данных и информационные системы. Основные понятия» Prezentacii.com Портал готовых презентаций PowerPoint

«Базы данных и информационные системы. Основные понятия» Prezentacii.com Портал готовых презентаций PowerPoint  Управління резервними копіями ОС

Управління резервними копіями ОС ПРОЦЕССОР Назначение, функции, состав

ПРОЦЕССОР Назначение, функции, состав Информационная система. Каталог музыкальных книг

Информационная система. Каталог музыкальных книг Объекты окружающего мира Свойства, действия и среда объектов

Объекты окружающего мира Свойства, действия и среда объектов  Информационные системы

Информационные системы Весёлый тест по информатике

Весёлый тест по информатике Информационная журналистика

Информационная журналистика Контекст и фрэйминг

Контекст и фрэйминг Форма модуля как объект конфигурации 1С

Форма модуля как объект конфигурации 1С Линейный алгоритм

Линейный алгоритм AMS partner. Софты. Обучение заработку в сети от 150 000 рублей

AMS partner. Софты. Обучение заработку в сети от 150 000 рублей Оборудование “Мультисофт cистемз”. Фискальные решений для бизнеса

Оборудование “Мультисофт cистемз”. Фискальные решений для бизнеса Назначение и виды операционных систем. Операции с файлами и папками

Назначение и виды операционных систем. Операции с файлами и папками Презентация "Компьютер и информация" - скачать презентации по Информатике

Презентация "Компьютер и информация" - скачать презентации по Информатике №2 Организация сети с использованием коммутатора

№2 Организация сети с использованием коммутатора Настройка безопасности беспроводной локальной сети

Настройка безопасности беспроводной локальной сети Количество информации

Количество информации Американские компании. Поисковая система eBay

Американские компании. Поисковая система eBay Презентация "Средства анализа защищённости. Internet Scanner" - скачать презентации по Информатике

Презентация "Средства анализа защищённости. Internet Scanner" - скачать презентации по Информатике