Содержание

- 2. УЧЕБНЫЕ ВОПРОСЫ: Микросхемы памяти Принципы организации обмена данными ЛИТЕРАТУРА: Дополнительная литература Л5. Угрюмов Е.П.. Цифровая схемотехника.

- 3. Контрольные вопросы Варианты: 1.Нарисовать УГО ОЗУ. 2.Состав ОЗУ 3.Нарисовать УГО ПЗУ. 4.Состав ПЗУ

- 4. 1. Микросхемы памяти

- 5. Основные виды памяти 1. Статическая память – построена на основе триггерной ячейки памяти 2. Динамическая память

- 6. Статическая память Классификация статической памяти: 1. По режимам работы делится на асинхронную, тактируемую синхронную (конвейерную) Запоминающими

- 7. Устройство статической памяти Запоминающий элемент ЗУ на n-МОП транзисторах представляет собой RS-триггер на транзисторах Т1 и

- 8. Работа статической памяти При обращении к данному ЗЭ появляется высокий потенциал на шине выборки ШВi (через

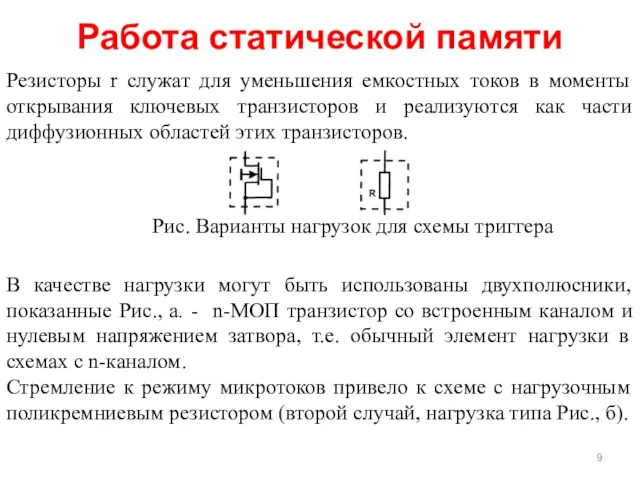

- 9. Работа статической памяти Резисторы r служат для уменьшения емкостных токов в моменты открывания ключевых транзисторов и

- 10. Разновидности статической памяти 1. Асинхронная статическая память — SRAM (Static Random Access Memory) имеет время выборки

- 11. Динамическая память Классификация динамической памяти: Динамическая память делится на стандартную, квазистатическую, повышенного быстродействия. В динамических ЗУ

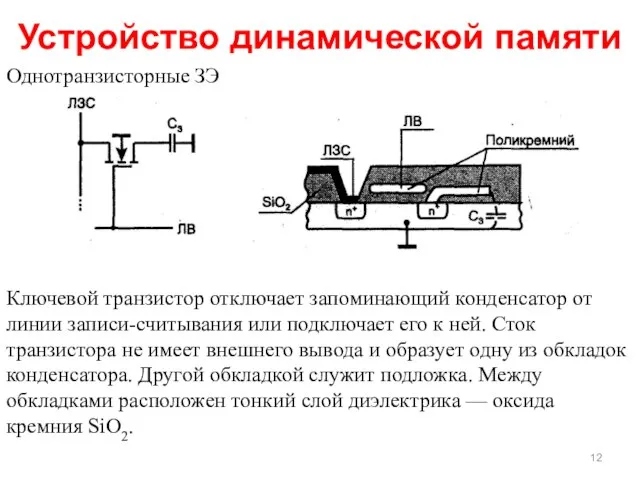

- 12. Устройство динамической памяти Однотранзисторные ЗЭ Ключевой транзистор отключает запоминающий конденсатор от линии записи-считывания или подключает его

- 13. Работа динамической памяти В режиме хранения ключевой транзистор заперт. При выборке данного ЗЭ транзистор отпирается. Запоминающая

- 14. Разновидности динамической памяти 1. Относительно медленная динамическая память с произвольным доступом DRAM (Dynamic Random Access Memory).

- 15. Разновидности динамической памяти 5. Синхронная динамическая память SDRAM (Synchronous DRAM), изготовляемая по БиКМОП (Bi-CMOS) технологии и

- 16. Разновидности динамической памяти 8. Direct RDRAM для пакетной обработки. 9. Память SLDRAM похожа на RDRAM. Содержит

- 17. Вывод по 1 вопросу В узлах МПС (микро-ЭВМ), требующих высокого быстродействия, широко применяются более дорогие статические

- 18. 2. Принципы организации обмена данными

- 19. Для достижения большей гибкости МПС в её работе реализуют различные режимы, отличающиеся друг от друга быстродействием,

- 20. Основной режим выполнения программ, Режимы прерывания, Режим прямого доступа к памяти, Режим ожидания, Режим захвата (пошаговые

- 21. 1) чтение данных из памяти; 2) запись данных в память; 3) выполнение арифметических и логических операций

- 22. Большую часть времени микро-ЭВМ тратит на выполнение основной программы. Обмен с внешними устройствами микро-ЭВМ осуществляет асинхронно

- 23. Микро-ЭВМ обменивается по прерыванию с большим количеством ВУ, но линия запроса прерывания одна. Для разделения одновременно

- 24. Предусмотрен для освобождения МП от управления обменом между УВВ и ОЗУ и предоставления ему возможности заниматься

- 25. Служит для согласования работы узлов МП с разным быстродействием. В магистралях микро-ЭВМ для этого вводится дополнительная

- 26. Применяют при отладке программ и отыскании неисправностей в микропроцессорных системах. Существуют два типа пошаговых режимов выполнения

- 27. Вывод по 2 вопросу Организация обмена данными внутри МП (и в целом в микро-ЭВМ) определяется режимами

- 29. Скачать презентацию

korolevstvo_zagadok__mishkie

korolevstvo_zagadok__mishkie Божья мудрость в сфере финансов

Божья мудрость в сфере финансов Товароведение и экспертиза электротоваров: холодильники и морозильники

Товароведение и экспертиза электротоваров: холодильники и морозильники Organizacja kursu, wprowadzenie i repetytorium

Organizacja kursu, wprowadzenie i repetytorium Поздравление

Поздравление В мастерской начинающих умельцев

В мастерской начинающих умельцев Благоверная деловая игра

Благоверная деловая игра Расчет индукционной канальной печи

Расчет индукционной канальной печи Путешествуем по миру

Путешествуем по миру План организации производственного участка и размещения оборудования

План организации производственного участка и размещения оборудования Презентація 2 клас Урок 1

Презентація 2 клас Урок 1 Modern construction materials

Modern construction materials ЦЕнники без цены (5)

ЦЕнники без цены (5) 20151016_konkurs_masterstva_2015_g

20151016_konkurs_masterstva_2015_g Волшебные фонари

Волшебные фонари Пример проведения функционально-стоимостного анализа изделия

Пример проведения функционально-стоимостного анализа изделия Инструкции для учителей ДЗ

Инструкции для учителей ДЗ Моя семья в Великой Отечественной войне

Моя семья в Великой Отечественной войне щелочные и щелочнозем. ме

щелочные и щелочнозем. ме Кто я, и где я живу?

Кто я, и где я живу? 20111015_muzykalnaya_stranichka_prezentaciya

20111015_muzykalnaya_stranichka_prezentaciya Малиновое приключение

Малиновое приключение Характеристика кожи лица

Характеристика кожи лица Принтеры. Типы принтеров, принцип их работы, устройство

Принтеры. Типы принтеров, принцип их работы, устройство История развития геофизики, геофизических методов исследования

История развития геофизики, геофизических методов исследования О Пасхе детям

О Пасхе детям Памятки в помощь лицам, прибывающим из Украины

Памятки в помощь лицам, прибывающим из Украины Była sobie wyspa

Była sobie wyspa