Содержание

- 2. 1. Типы Предустановленные Типы в VHDL Некоторые общие встроенные типы (для сигналов и переменных): Бит: '0'

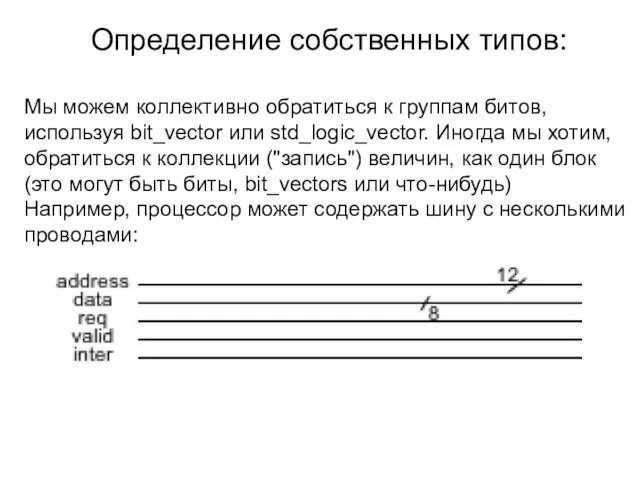

- 3. Определение собственных типов: Мы можем коллективно обратиться к группам битов, используя bit_vector или std_logic_vector. Иногда мы

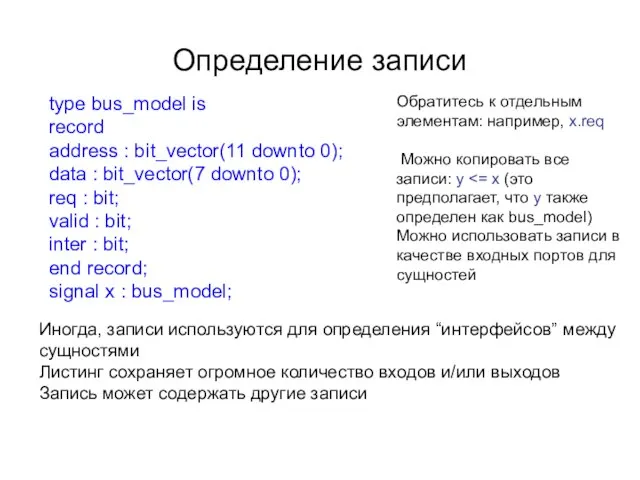

- 4. Определение записи type bus_model is record address : bit_vector(11 downto 0); data : bit_vector(7 downto 0);

- 5. Массивы: type word is array (0 to 31) of bit; type data is array (7 downto

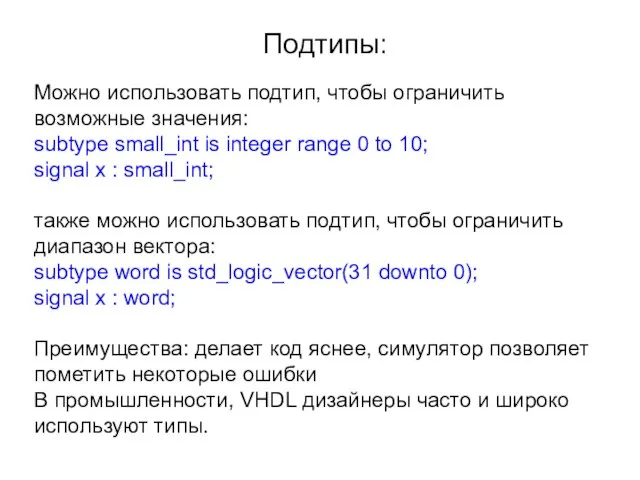

- 6. Подтипы: Можно использовать подтип, чтобы ограничить возможные значения: subtype small_int is integer range 0 to 10;

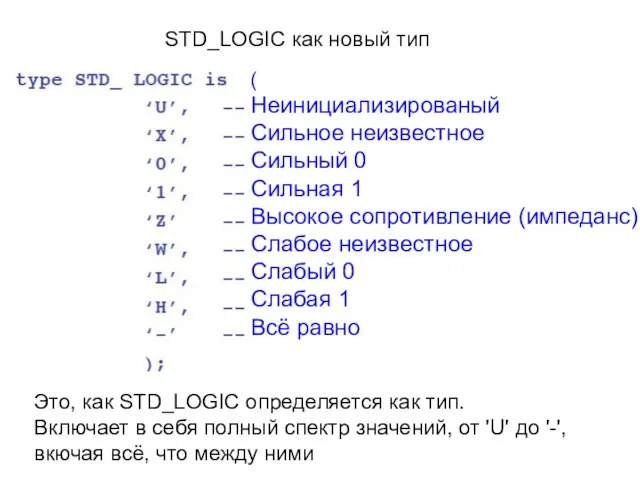

- 7. STD_LOGIC как новый тип ( Неинициализированый Сильное неизвестное Сильный 0 Сильная 1 Высокое сопротивление (импеданс) Слабое

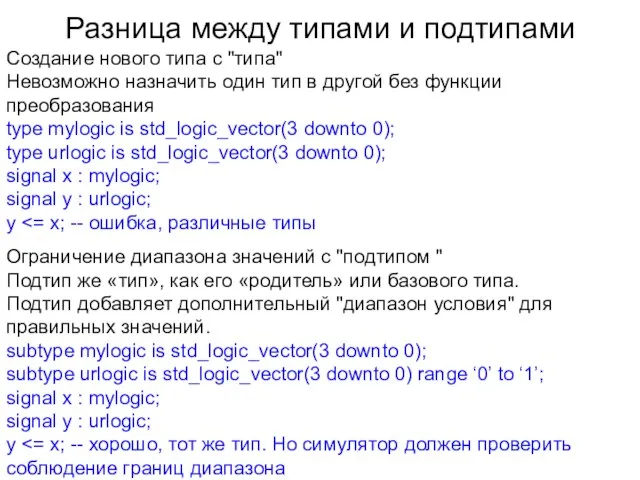

- 8. Разница между типами и подтипами Создание нового типа с "типа" Невозможно назначить один тип в другой

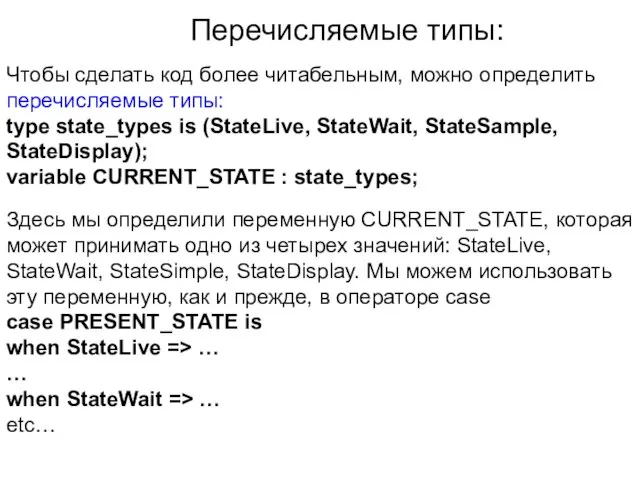

- 9. Чтобы сделать код более читабельным, можно определить перечисляемые типы: type state_types is (StateLive, StateWait, StateSample, StateDisplay);

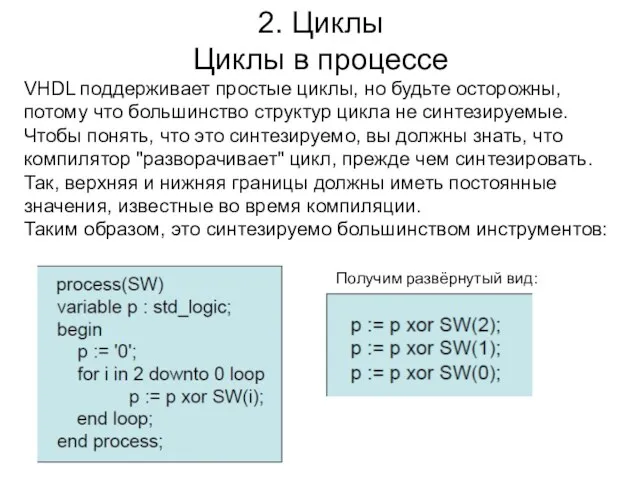

- 10. 2. Циклы Циклы в процессе VHDL поддерживает простые циклы, но будьте осторожны, потому что большинство структур

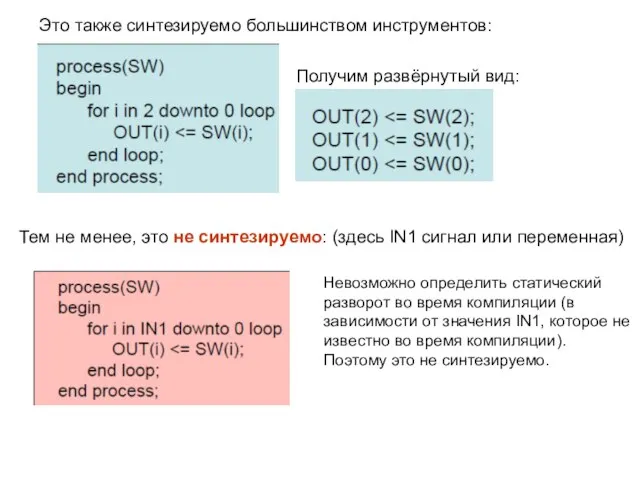

- 11. Это также синтезируемо большинством инструментов: Получим развёрнутый вид: Тем не менее, это не синтезируемо: (здесь IN1

- 12. Наблюдение: поскольку границы должны быть известны во время компиляции, цикл в процессе является просто коротким путём,

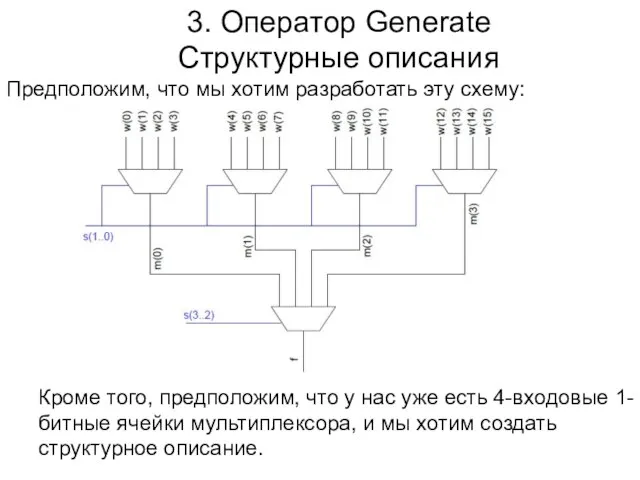

- 13. 3. Оператор Generate Структурные описания Предположим, что мы хотим разработать эту схему: Кроме того, предположим, что

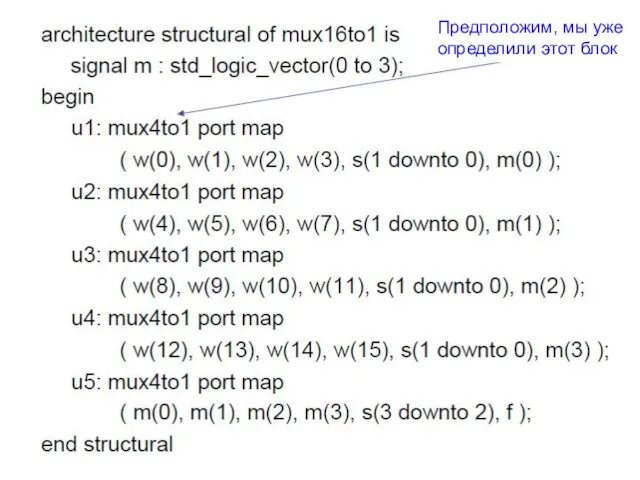

- 14. Предположим, мы уже определили этот блок

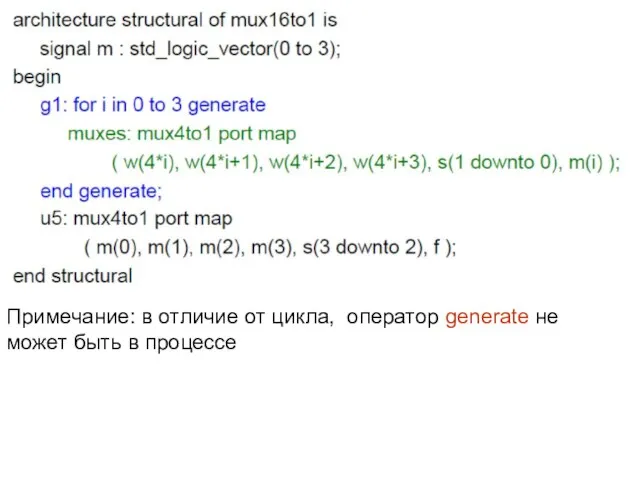

- 15. Примечание: в отличие от цикла, оператор generate не может быть в процессе

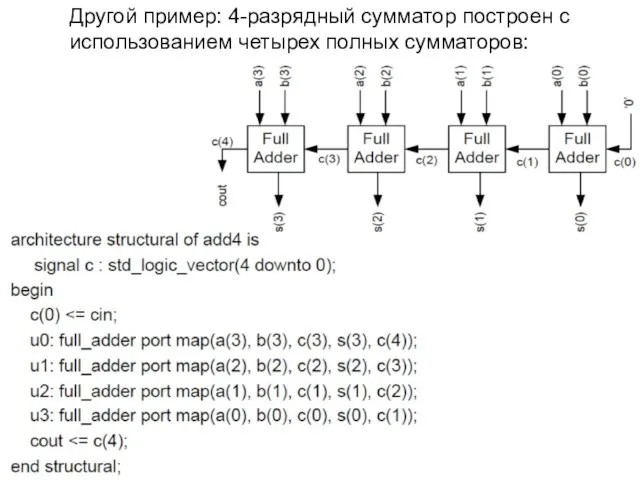

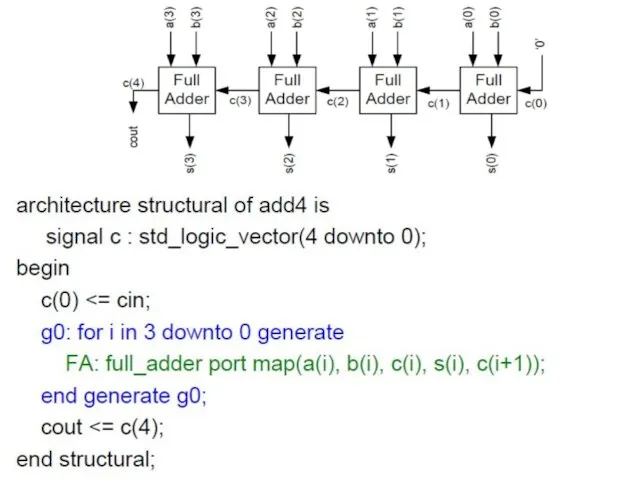

- 16. Другой пример: 4-разрядный сумматор построен с использованием четырех полных сумматоров:

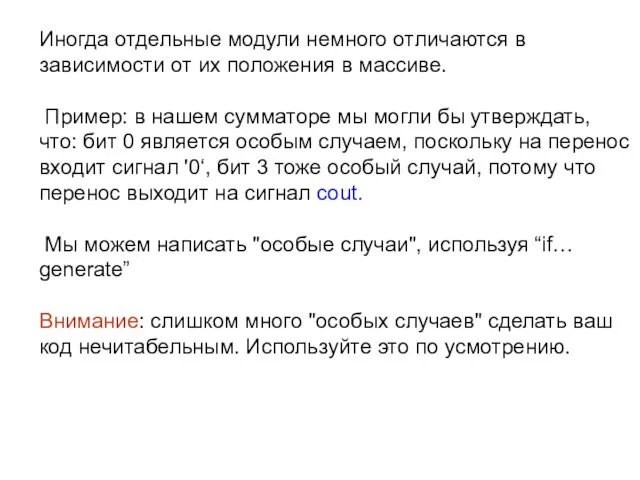

- 18. Иногда отдельные модули немного отличаются в зависимости от их положения в массиве. Пример: в нашем сумматоре

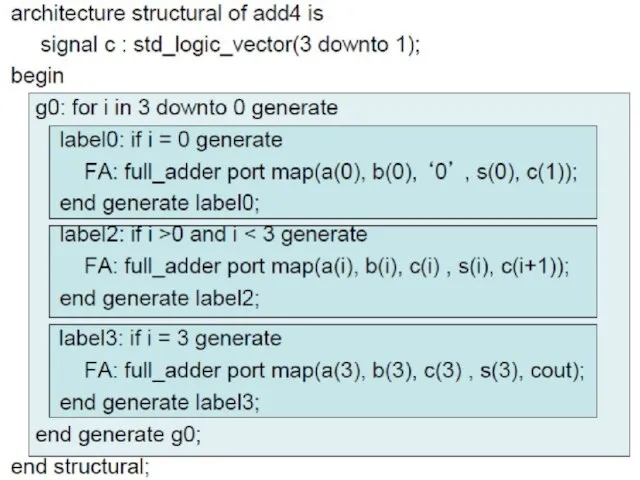

- 20. Еще одно предупреждение: Generate является только инструментом, который помогает описать структурные описания! Различия между generate и

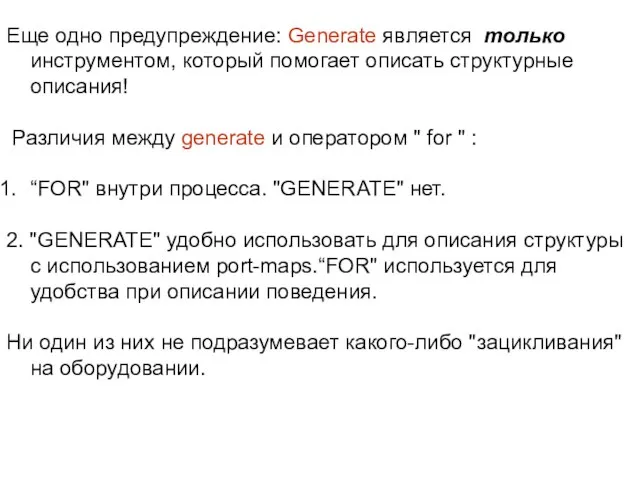

- 21. Драйверы в троичной логике/ Tri-state Drivers Пытается подать на узел 3.3 вольта Пытается подать на узел

- 22. Это пример “борьбы” - Что происходит, зависит от способа реализации схемы - для CМОS (большинство чипов

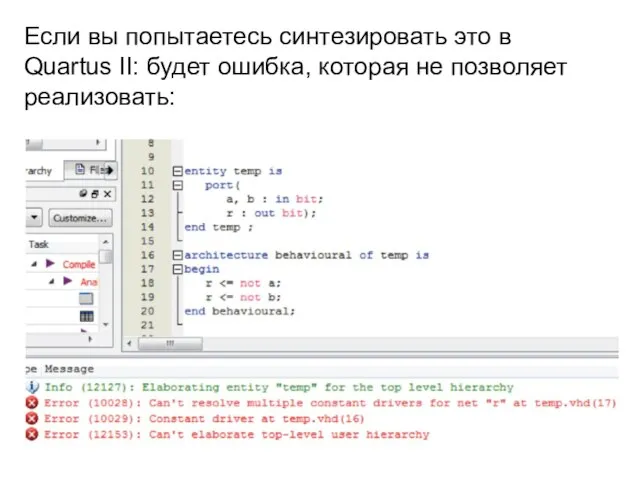

- 23. Если вы попытаетесь синтезировать это в Quartus II: будет ошибка, которая не позволяет реализовать:

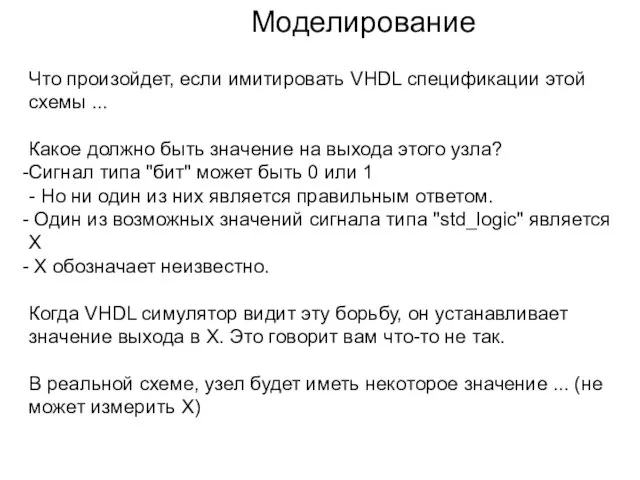

- 24. Что произойдет, если имитировать VHDL спецификации этой схемы ... Какое должно быть значение на выхода этого

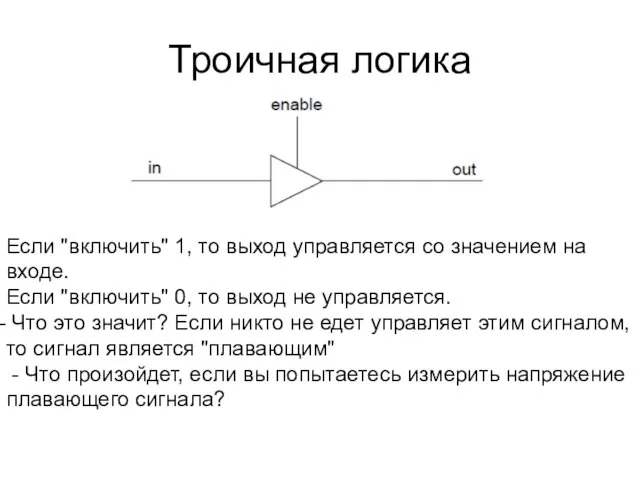

- 25. Троичная логика Если "включить" 1, то выход управляется со значением на входе. Если "включить" 0, то

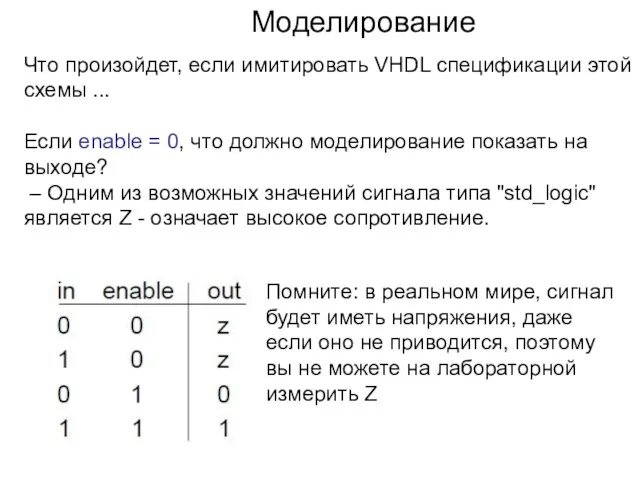

- 26. Что произойдет, если имитировать VHDL спецификации этой схемы ... Если enable = 0, что должно моделирование

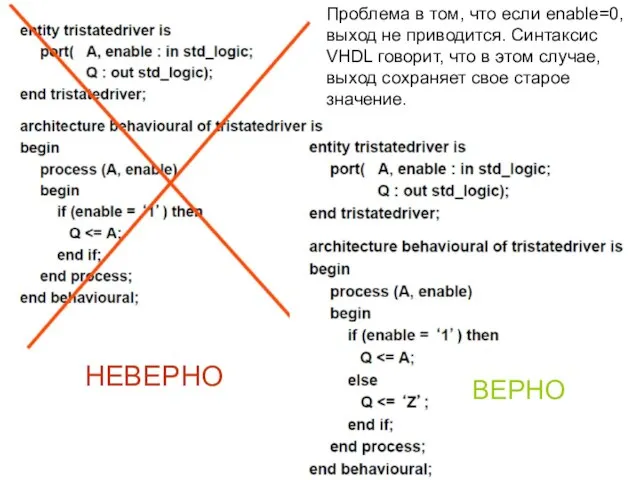

- 27. НЕВЕРНО ВЕРНО Проблема в том, что если enable=0, выход не приводится. Синтаксис VHDL говорит, что в

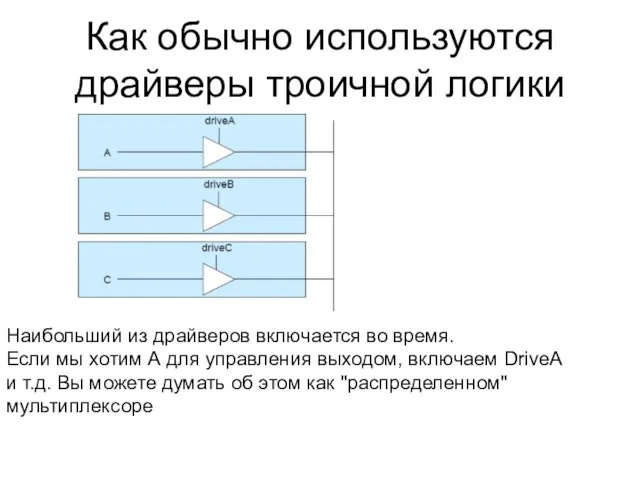

- 28. Как обычно используются драйверы троичной логики Наибольший из драйверов включается во время. Если мы хотим А

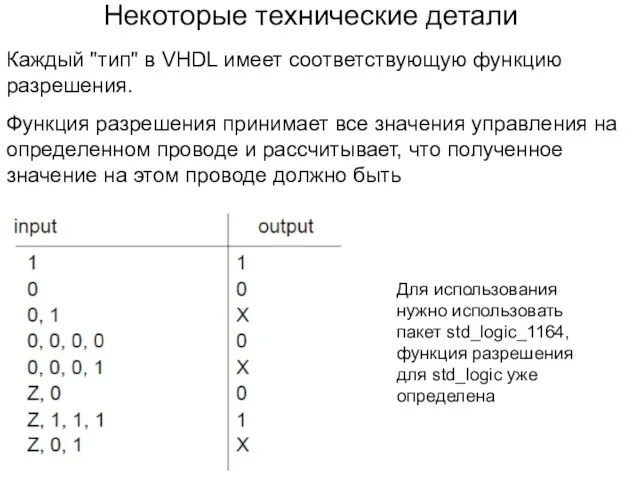

- 29. Некоторые технические детали Каждый "тип" в VHDL имеет соответствующую функцию разрешения. Функция разрешения принимает все значения

- 31. Скачать презентацию

Акжарская площадь. Гистрограмма распределения меди

Акжарская площадь. Гистрограмма распределения меди Разработка высоковольтного асинхронного взрывобезопасного двигателя мощностью 200 кВт с повышенной перегрузочной способностью

Разработка высоковольтного асинхронного взрывобезопасного двигателя мощностью 200 кВт с повышенной перегрузочной способностью Литературный квест по прочитанным произведениям

Литературный квест по прочитанным произведениям Презентационный материал. Драматизм и исповедальность поэмы

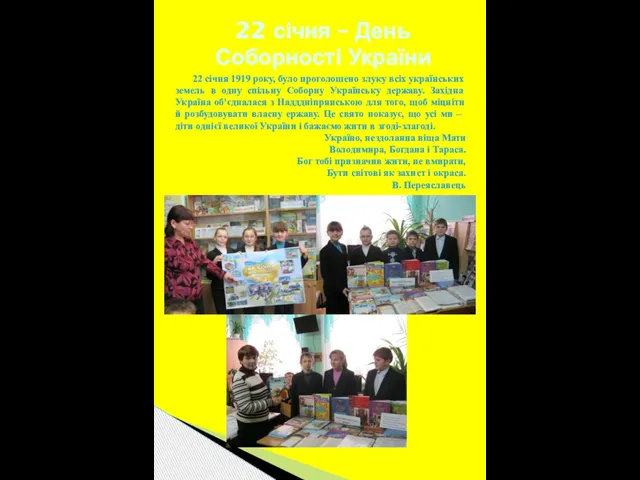

Презентационный материал. Драматизм и исповедальность поэмы 22 січня – День Соборності України

22 січня – День Соборності України Основы ухода за больными терапевтического профиля: Антропометрия. Гигиена. Основы физиотерапии

Основы ухода за больными терапевтического профиля: Антропометрия. Гигиена. Основы физиотерапии Парк молодежи

Парк молодежи Мебель в пункте выдачи. Техническое описание

Мебель в пункте выдачи. Техническое описание English speaking countries

English speaking countries Внеурочная деятельность Азбука общения Тема занятия Как провести праздник дома

Внеурочная деятельность Азбука общения Тема занятия Как провести праздник дома Альтернативные источники энергии ветра

Альтернативные источники энергии ветра Обпилювання заготовок із сортового прокату та листового металу

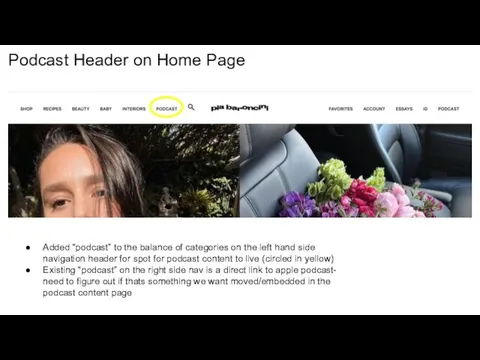

Обпилювання заготовок із сортового прокату та листового металу Pia Podcast Content Mock up

Pia Podcast Content Mock up Трубчевские поэты о войне

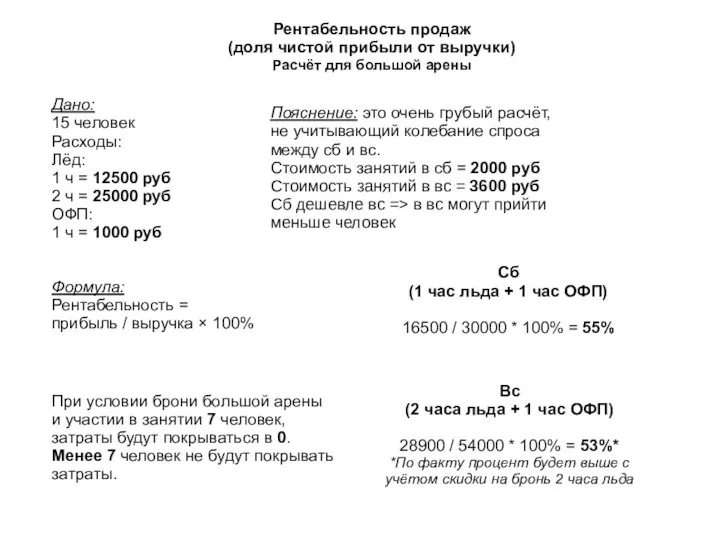

Трубчевские поэты о войне рентабельность

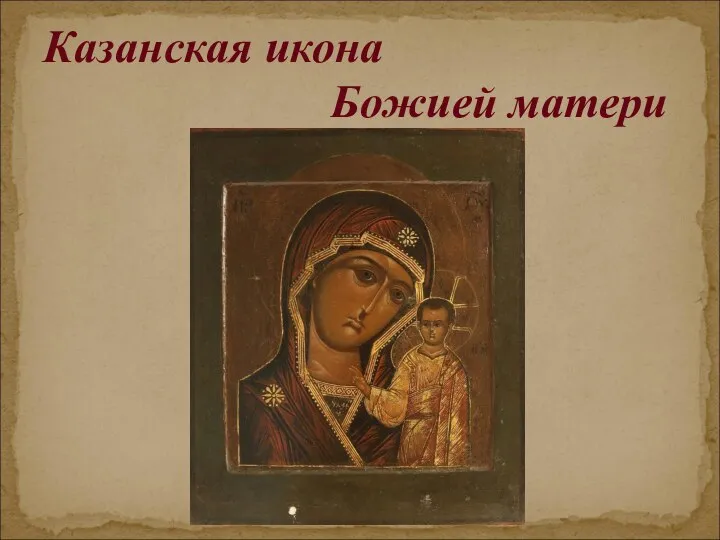

рентабельность Казанская икона Божией матери

Казанская икона Божией матери Олимпийские виды спорта. Лёгкая атлетика

Олимпийские виды спорта. Лёгкая атлетика Les jours de la semaine et les planètes

Les jours de la semaine et les planètes Оценка разрешающей способности малоглубинной сейсморазведки при определении глубины залегания скальных пород

Оценка разрешающей способности малоглубинной сейсморазведки при определении глубины залегания скальных пород Фотоальбом. Экскурсия 5 А класса

Фотоальбом. Экскурсия 5 А класса Отчет по экскурсии. Кварц-виниловая плитка

Отчет по экскурсии. Кварц-виниловая плитка Подбор и презентация турпродукта по запросу клиента: Подготовка курортного направления

Подбор и презентация турпродукта по запросу клиента: Подготовка курортного направления Основы построения инфокоммуникационных систем и сетей. Основные понятия и определения. Уровни передачи

Основы построения инфокоммуникационных систем и сетей. Основные понятия и определения. Уровни передачи Беларускія рамёствы

Беларускія рамёствы Эмоционально-экспрессивная окраска слов

Эмоционально-экспрессивная окраска слов Рубцова Р.У

Рубцова Р.У Советы правильного бега

Советы правильного бега The getKanban Board Game!

The getKanban Board Game!