Содержание

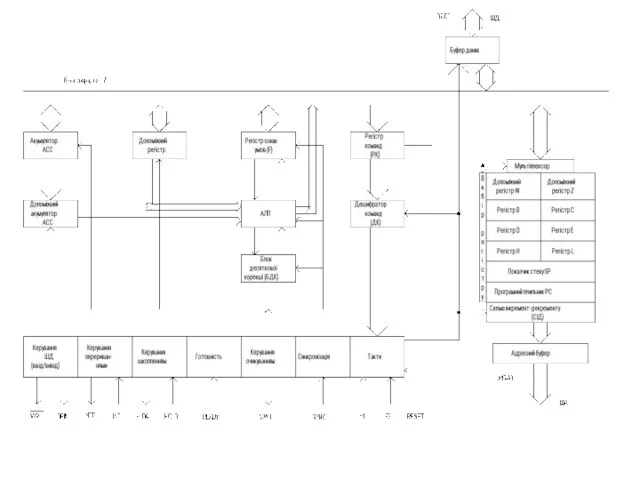

- 2. АРХІТЕКТУРА МП К580ВМ80 Даний МП являє собою центральний процесорний елемент (ЦПЕ), побудований на одному кристалі, структурна

- 4. Згідно наведеної схеми основними функціональними вузлами ЦПЕ є: - АЛП; - пристрій керування та синхронізації; -

- 5. Буфер даних (БД)- двонаправлена схема з трьома логічними станами (ввід, вивід, виключено), яка призначена для обміну

- 6. Блок регістрів загального призначення (РЗП) призначений для збереження та видачі даних. Регістри В, С, D, H,

- 7. Регістр команд (РК) призначений для збереження 1-го байту команди, яка виконується МП в поточний момент часу.

- 8. Дешифратор команд (ДК) для шифрування коду операції (КОП), який міститься у 1-му байті команди, з наступною

- 9. Арифметико логічний пристрій (АЛП) займає в МП центральне місце і являє собою 8‑мирозрядний паралельний пристрій, який

- 10. При виконанні операцій АЛП використовує наступні регістри: - 8-мирозрядний допоміжний регістр для тимчасового збереження даних; -

- 11. Регістр прапорців (F) призначений для збереження стану результата виконання операції АЛП і включає в себе наступні

- 12. Потреба у регістрі прапорців обумовлена тим, що виконання будь-якої операції (команди) може ставитися в залежності від

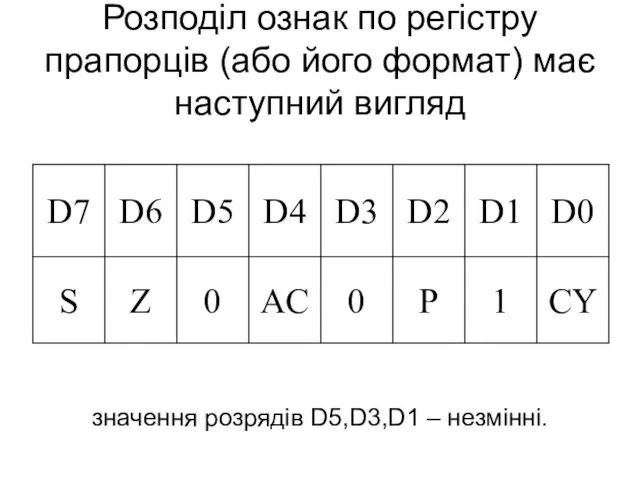

- 13. Розподіл ознак по регістру прапорців (або його формат) має наступний вигляд значення розрядів D5,D3,D1 – незмінні.

- 14. 16-тирозрядний програмний лічильник (або лічильник команд, Program Counter - PC) призначений для формування та збереження адреси

- 15. Покажчик стеку (Stack Pointer - SP) призначений як для початкового формування в оперативній пам’яті системи спеціальної

- 16. Оскільки при виконання будь-якої програми може виникнути потреба виклику підпрограми (або перерви виконання поточної програми), то

- 17. Адресний буфер (АБ) є 16-тирозрядним і призначений для формування вихідної адреси для зовнішньої адресної шини (ША),

- 18. Пристрій керування та синхронізації (ПКС) призначений для прийому та формування керуючих зовнішніх сигналів і здійснення управління

- 22. Скачать презентацию

רוצה +שם פועל

רוצה +שם פועל Конец Смутного времени

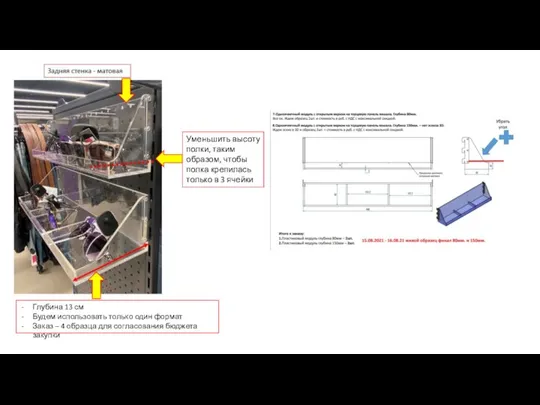

Конец Смутного времени Навеска пластиковая

Навеска пластиковая Types and properties of sound-absorbing panels

Types and properties of sound-absorbing panels 20150120_prakticheskie_zanyatiya

20150120_prakticheskie_zanyatiya a77d64503dde8688

a77d64503dde8688 Перечень внутри дворовых территорий, подлежащих ремонту. Город Серпухов

Перечень внутри дворовых территорий, подлежащих ремонту. Город Серпухов Фото-арсенал. Камера, объектив, штатив

Фото-арсенал. Камера, объектив, штатив Твердотельный накопитель SSD

Твердотельный накопитель SSD Подвижной состав пассажирского автомобильного транспорта

Подвижной состав пассажирского автомобильного транспорта Собственные бренды Абамет

Собственные бренды Абамет 20120720_soobshchenie_dlya_pedsoveta_s_prezentaciey

20120720_soobshchenie_dlya_pedsoveta_s_prezentaciey Искусство Древнего Египта

Искусство Древнего Египта Сравнительный анализ годовой динамики влажности агрогенных и постагрогенных почв на примере территории Студенческий сад АГУ

Сравнительный анализ годовой динамики влажности агрогенных и постагрогенных почв на примере территории Студенческий сад АГУ Пасхальные яйца

Пасхальные яйца Фитолеум жшс өндірісінде ошаған майының өндірісін техникалық қайта жабдықтау

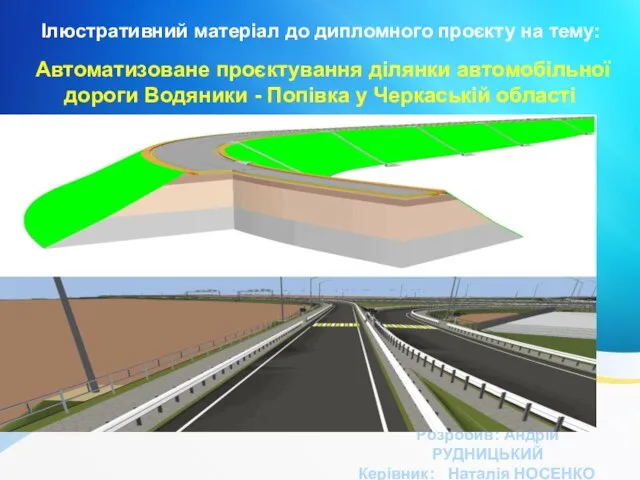

Фитолеум жшс өндірісінде ошаған майының өндірісін техникалық қайта жабдықтау Автоматизоване проєктування ділянки автомобільної дороги Водяники - Попівка у Черкаській області

Автоматизоване проєктування ділянки автомобільної дороги Водяники - Попівка у Черкаській області математика в сказках

математика в сказках Визитная карточка школьнго музея

Визитная карточка школьнго музея Викторина Занимательно о литературе

Викторина Занимательно о литературе Алексеева. Викторина по англ. яз

Алексеева. Викторина по англ. яз Кораблёв Борис 1 бригада 214

Кораблёв Борис 1 бригада 214 Технический КВ форум Своими знаниями и опытом надо делится!

Технический КВ форум Своими знаниями и опытом надо делится! Пластики и керамика

Пластики и керамика Акция Ключенкова К

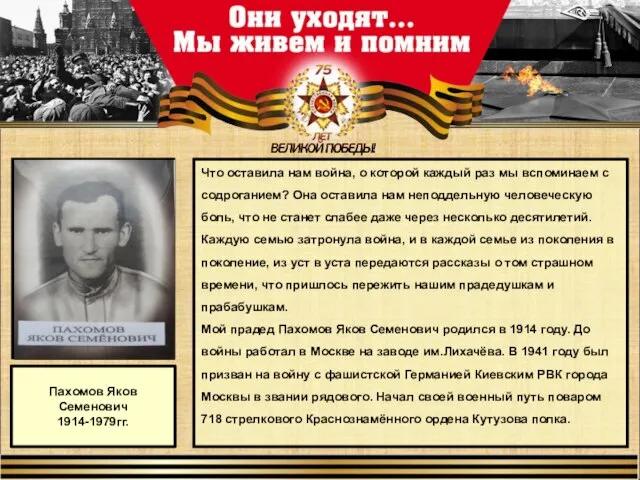

Акция Ключенкова К презентация

презентация С новым годом (стихотворения)

С новым годом (стихотворения) Обеспечение пожаровзрывобезопасности систем отопления

Обеспечение пожаровзрывобезопасности систем отопления