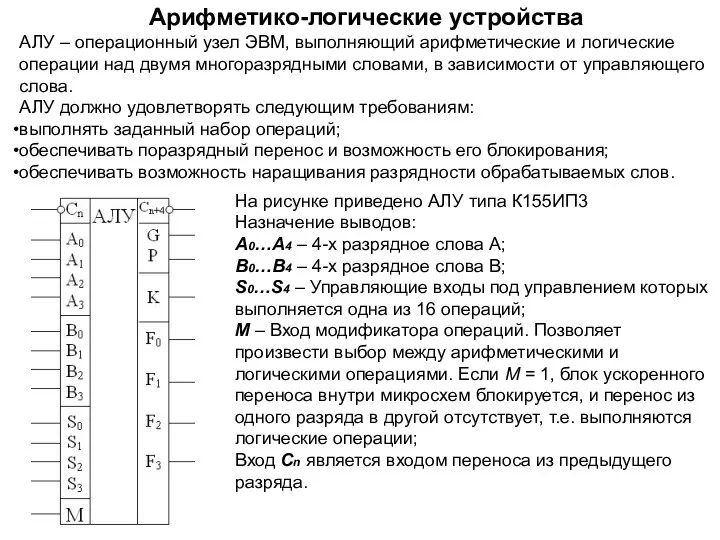

Арифметико-логические устройства

АЛУ – операционный узел ЭВМ, выполняющий арифметические и логические операции

над двумя многоразрядными словами, в зависимости от управляющего слова.

АЛУ должно удовлетворять следующим требованиям:

выполнять заданный набор операций;

обеспечивать поразрядный перенос и возможность его блокирования;

обеспечивать возможность наращивания разрядности обрабатываемых слов.

На рисунке приведено АЛУ типа К155ИП3

Назначение выводов:

A0…A4 – 4-х разрядное слова А;

B0…B4 – 4-х разрядное слова B;

S0…S4 – Управляющие входы под управлением которых выполняется одна из 16 операций;

M – Вход модификатора операций. Позволяет произвести выбор между арифметическими и логическими операциями. Если М = 1, блок ускоренного переноса внутри микросхем блокируется, и перенос из одного разряда в другой отсутствует, т.е. выполняются логические операции;

Вход Cn является входом переноса из предыдущего разряда.

Станки VI группы (фрезерные). Тема 3.3

Станки VI группы (фрезерные). Тема 3.3 Фотоальбом. Окрыляющая энергетика офиса Red Bull

Фотоальбом. Окрыляющая энергетика офиса Red Bull Зачем искусство

Зачем искусство Семинарские занятия для молодых специалистов отделения электромеханики

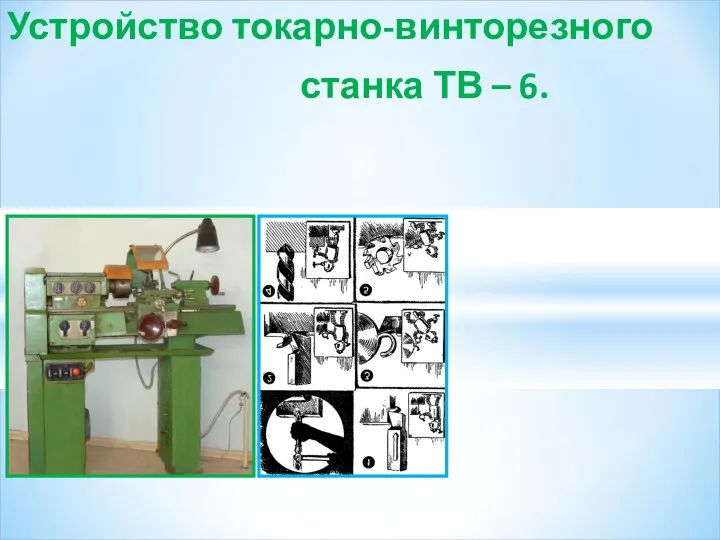

Семинарские занятия для молодых специалистов отделения электромеханики Устройство токарно-винторезного станка ТВ – 6

Устройство токарно-винторезного станка ТВ – 6 Обзор книг по изобразительному искусству для детей и взрослых из собрания Арт - Сатки

Обзор книг по изобразительному искусству для детей и взрослых из собрания Арт - Сатки Пиво

Пиво Магазин Базис, на память

Магазин Базис, на память Проект шумозащитного дома средней этажности

Проект шумозащитного дома средней этажности Житие Епифания Премудрого

Житие Епифания Премудрого Yi сamera usb. Guide

Yi сamera usb. Guide Тест, Шахматы

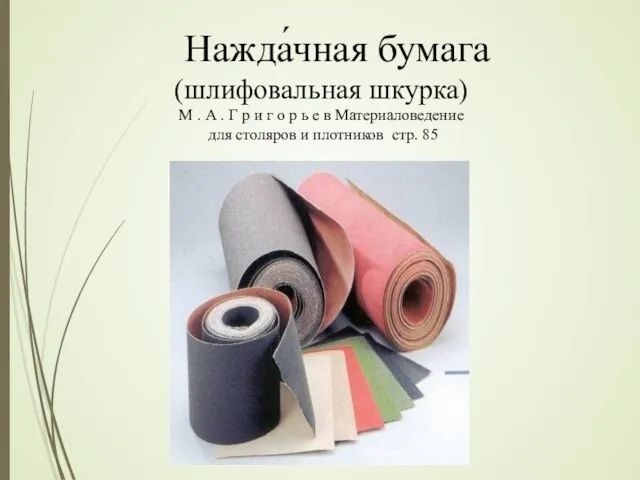

Тест, Шахматы Нажда́чная бумага (шлифовальная шкурка)

Нажда́чная бумага (шлифовальная шкурка) Сокращение издержек от штрафных санкций

Сокращение издержек от штрафных санкций 20120329_prezentaciya_k_uroku_po_rsv_i_fp__1_chast

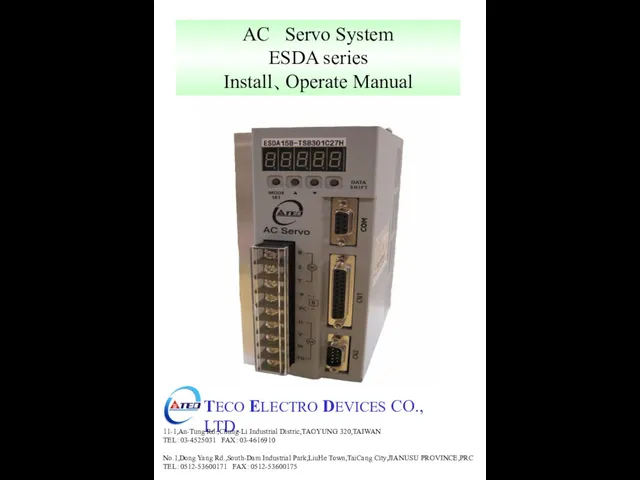

20120329_prezentaciya_k_uroku_po_rsv_i_fp__1_chast AC Servo System ESDA series Install、Operate Manual

AC Servo System ESDA series Install、Operate Manual 20150327_prezentatsiya3_0

20150327_prezentatsiya3_0 школа

школа Красота мира

Красота мира Презентация Microsoft Office PowerPoint

Презентация Microsoft Office PowerPoint Алена

Алена Сервис Mentimeter

Сервис Mentimeter Тема 1. Эконом теория

Тема 1. Эконом теория День защитника Отечества. Профессии в армии

День защитника Отечества. Профессии в армии Природа поселка Мадмас

Природа поселка Мадмас Pravila_distsipliny_i_poryadka_vzvoda_Novaya_versia_Raspolozhenie

Pravila_distsipliny_i_poryadka_vzvoda_Novaya_versia_Raspolozhenie Самодельные постройки из LEGO

Самодельные постройки из LEGO katalog_nabroski

katalog_nabroski