Содержание

- 2. Тема занятия: Структура кристалла современной СБИС Рассмотрим организацию кристалла СБИС в плане и в профиле. В

- 3. Вид кристалла в плане, в профиле, распределение напряжений

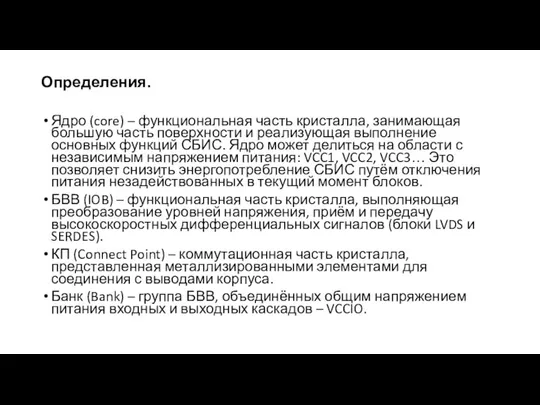

- 4. Определения. Ядро (core) – функциональная часть кристалла, занимающая большую часть поверхности и реализующая выполнение основных функций

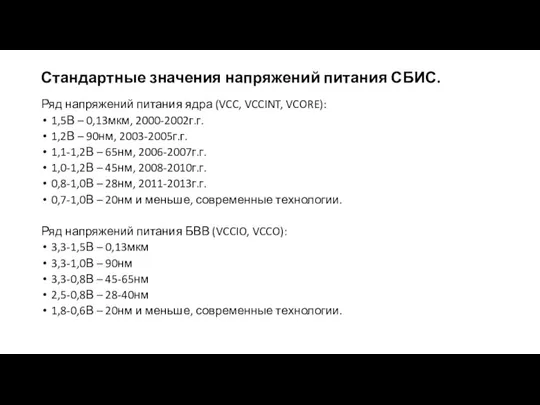

- 5. Стандартные значения напряжений питания СБИС. Ряд напряжений питания ядра (VCC, VCCINT, VCORE): 1,5В – 0,13мкм, 2000-2002г.г.

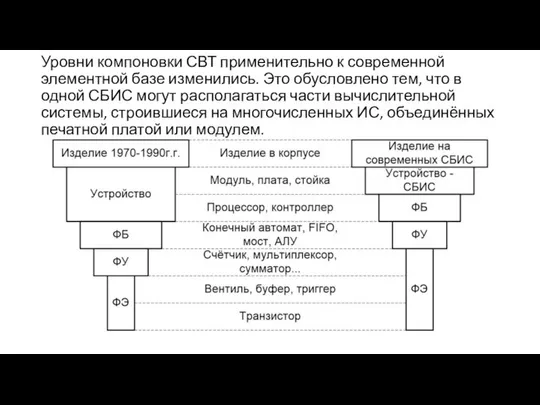

- 6. Уровни компоновки СВТ применительно к современной элементной базе изменились. Это обусловлено тем, что в одной СБИС

- 7. ФЭ, реализуемые в ядре СБИС: Триггер, регистр Логический вентиль, LUT-преобразователь (комбинационные логические элементы – CL, Combinatorial

- 8. ФЭ, реализуемые в блоках ввода-вывода СБИС: Триггер, регистр Программируемая задержка сигнала Встроенные резисторы согласования волнового сопротивления

- 9. В процессе проектирования ресурсы кристалла цифровой СБИС следует разделять на следующие пять групп: Комбинационные логические схемы

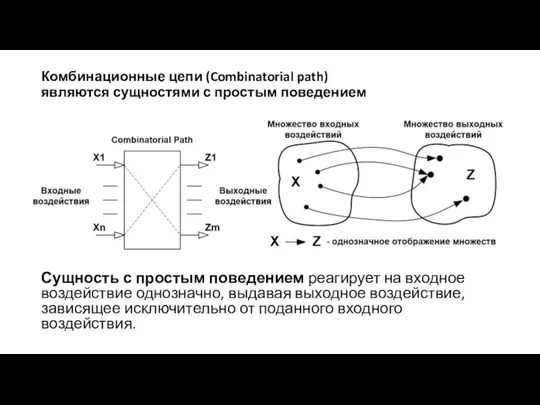

- 10. Комбинационные цепи (Combinatorial path) являются сущностями с простым поведением Сущность с простым поведением реагирует на входное

- 11. Следует отметить, что в случае цифровой логической схемы элементом множества входных или выходных воздействий является определённая

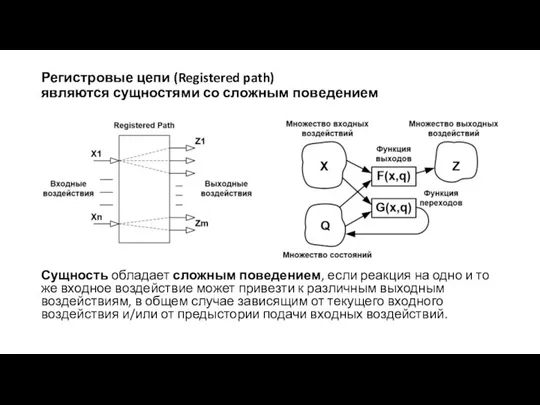

- 12. Регистровые цепи (Registered path) являются сущностями со сложным поведением Сущность обладает сложным поведением, если реакция на

- 13. Каждая из двух функций F и G в объёме сущности со сложным поведением реализует однозначное отображение

- 14. Возвращаясь к классификации ресурсов общего назначения кристалла СБИС или ПЛИС, разделим их на две категории: Комбинационные

- 16. Скачать презентацию

20150119_prezentatsiya_blok_meropriyatie

20150119_prezentatsiya_blok_meropriyatie Технология ремонта вертикальных поверхностей, облицованных керамическими плитками

Технология ремонта вертикальных поверхностей, облицованных керамическими плитками Реакторы токоограничивающие

Реакторы токоограничивающие Микропроцессор INTEL 8086

Микропроцессор INTEL 8086 Формирование математических представлений

Формирование математических представлений Распределение комплектов машин по объектам (лекция 14, 15, 16)

Распределение комплектов машин по объектам (лекция 14, 15, 16) Этнохоронимы

Этнохоронимы Эскиз-идея поселка

Эскиз-идея поселка Преподобный Сергий Радонежский: Игумен Земли Русской

Преподобный Сергий Радонежский: Игумен Земли Русской Справедливость. Сырцова

Справедливость. Сырцова Доклад об основных результатах деятельности Комитета по транспорту за 2015 год и задачах на 2016 год

Доклад об основных результатах деятельности Комитета по транспорту за 2015 год и задачах на 2016 год 20150427_prezentatsiya_madonny_voyny_chast_1

20150427_prezentatsiya_madonny_voyny_chast_1 Yandex with Uber in $1 bln deal (1)

Yandex with Uber in $1 bln deal (1) г. Новосибирск фотоотчет склада хранения артиллерийских боеприпасов

г. Новосибирск фотоотчет склада хранения артиллерийских боеприпасов Число 7. Цифра 7

Число 7. Цифра 7 Цвет как средство выражения

Цвет как средство выражения выступление1 ТРИЗ Полешова

выступление1 ТРИЗ Полешова Troubleshooting

Troubleshooting Системы разработки нефтяных месторождений

Системы разработки нефтяных месторождений 20140616_no2chtenie_slov_iz_2_pryamykh_slogov

20140616_no2chtenie_slov_iz_2_pryamykh_slogov Бизнес модель Fairy Pairs

Бизнес модель Fairy Pairs Свято-Троицкий женский монастырь города Муром

Свято-Троицкий женский монастырь города Муром Модельный ряд JCB. Преимущества минипогрузчика

Модельный ряд JCB. Преимущества минипогрузчика Вредное влияние алкоголя, курения и наркотиков в период эмбрионального развития

Вредное влияние алкоголя, курения и наркотиков в период эмбрионального развития ВК Ефремова Урмары

ВК Ефремова Урмары Умная Маруся

Умная Маруся Поместье Данбург

Поместье Данбург Можно ли соединить детали без соединительных материалов?

Можно ли соединить детали без соединительных материалов?