Содержание

- 2. ПОВТОРЕНИЕ Цифровыми устройствами комбинационного типа - ?

- 3. ПОВТОРЕНИЕ. ПРИНЦИП СЛОЖЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

- 4. ДВОИЧНЫЕ СУММАТОРЫ Сумматор — устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих

- 5. КЛАССИФИКАЦИЯ СУММАТОРОВ В зависимости от формы представления информации различают сумматоры аналоговые и цифровые.

- 6. ПО СПОСОБУ РЕАЛИЗАЦИИ механические электромеханические электронные пневматические

- 7. ПО ПРИНЦИПУ ДЕЙСТВИЯ на счётчиках, считающие количества импульсов в операндах функциональные, выдающие на выходах значения логической

- 8. ПО АРХИТЕКТУРЕ четвертьсумматоры — бинарные (двухоперандные) сумматоры по модулю без разряда переноса, характеризующиеся наличием двух входов,

- 9. ПО СПОСОБУ ДЕЙСТВИЯ Последовательные (одноразрядные), в которых обработка разрядов чисел ведётся поочерёдно, разряд за разрядом, на

- 10. ПО СПОСОБУ ОРГАНИЗАЦИИ ПЕРЕНОСА С последовательным переносом; С параллельным переносом; С условным переносом; С групповым переносом.

- 11. ПО СПОСОБУ ВЫПОЛНЕНИЯ ОПЕРАЦИИ СЛОЖЕНИЯ И ВОЗМОЖНОСТИ СОХРАНЕНИЯ РЕЗУЛЬТАТА СЛОЖЕНИЯ МОЖНО ВЫДЕЛИТЬ ТРИ ОСНОВНЫХ ВИДА СУММАТОРОВ:

- 12. ДВОИЧНЫЙ СУММАТОР Двоичный сумматор может быть определён тремя способами: 1. табличным, в виде таблицы истинности, 2.

- 13. ВАЖНЕЙШИМИ ПАРАМЕТРАМИ СУММАТОРОВ ЯВЛЯЮТСЯ: разрядность; статические параметры: Uвх, Uвх, Iвх и так далее, то есть обычные

- 14. ВАЖНЕЙШИМИ ПАРАМЕТРАМИ СУММАТОРОВ ЯВЛЯЮТСЯ: динамические параметры. Сумматоры характеризуются четырьмя задержками распространения: от подачи входного переноса до

- 15. ЧЕТВЕРТЬСУММАТОР Простейшим двоичным суммирующим элементом является четвертьсумматор. Происхождение названия этого элемента следует из того, что он

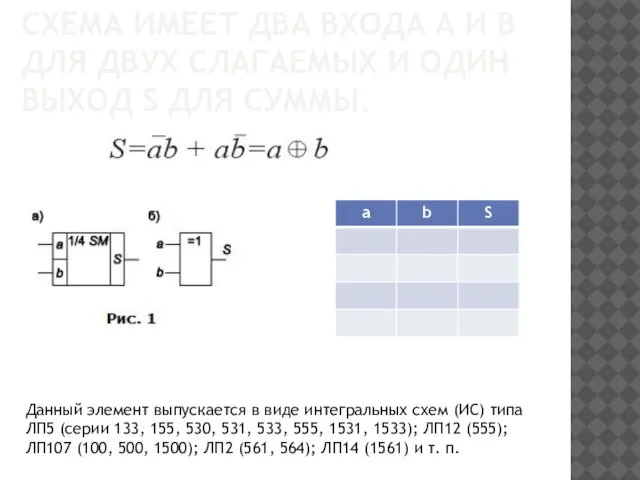

- 16. СХЕМА ИМЕЕТ ДВА ВХОДА А И B ДЛЯ ДВУХ СЛАГАЕМЫХ И ОДИН ВЫХОД S ДЛЯ СУММЫ.

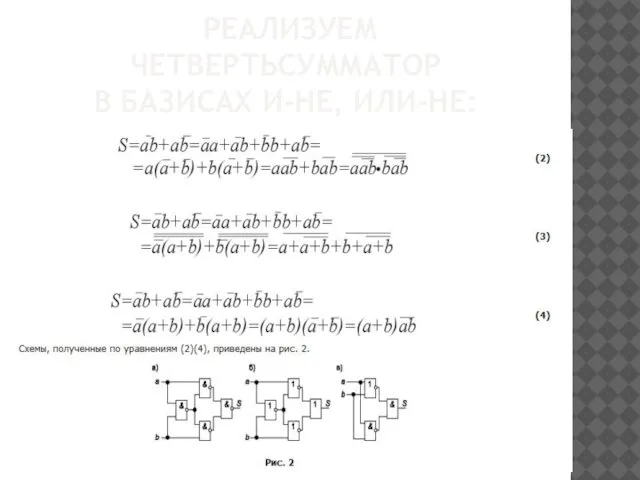

- 17. РЕАЛИЗУЕМ ЧЕТВЕРТЬСУММАТОР В БАЗИСАХ И-НЕ, ИЛИ-НЕ:

- 18. ПОЛУСУММАТОР Cхема, которая обеспечивает сложение двух однобитных чисел А и В называется полусумматором. Полусумматор имеет 4

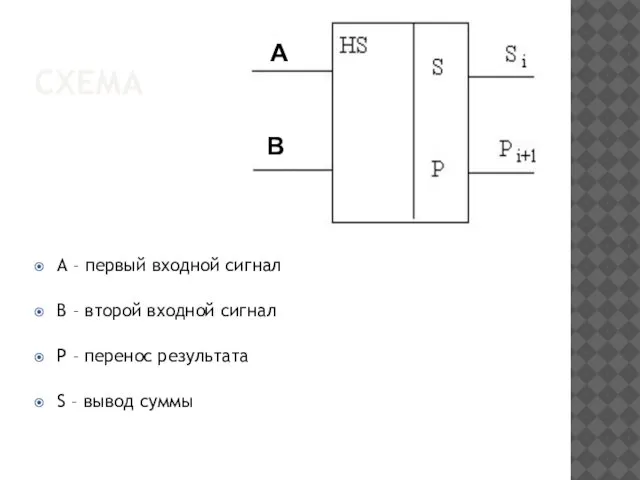

- 19. СХЕМА A – первый входной сигнал B – второй входной сигнал P – перенос результата S

- 20. В ДВОИЧНОЙ СИСТЕМЕ СЛОЖЕНИЕ ДВУХ ДВОИЧНЫХ ЧИСЕЛ ОСУЩЕСТВЛЯЕТСЯ ПО ПРАВИЛУ, ОПИСАННОМУ В ТАБЛИЦЕ:

- 21. ФОРМУЛА ДЛЯ S (ВЫВОД) Формулу для S можно вывести с помощью СДНФ используя таблицу истинности.

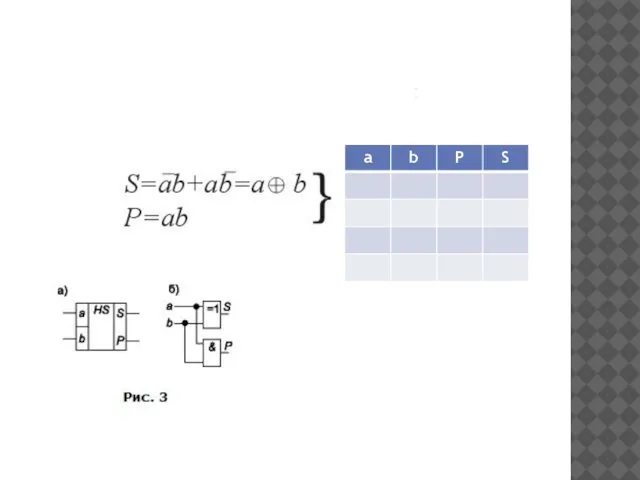

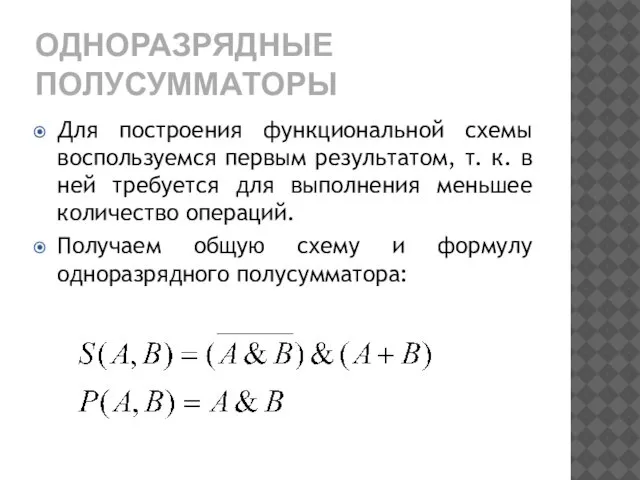

- 22. ОДНОРАЗРЯДНЫЕ ПОЛУСУММАТОРЫ Для построения функциональной схемы воспользуемся первым результатом, т. к. в ней требуется для выполнения

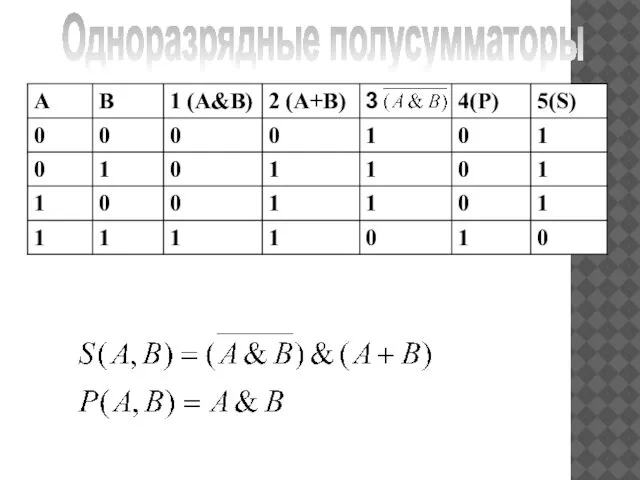

- 23. Одноразрядные полусумматоры

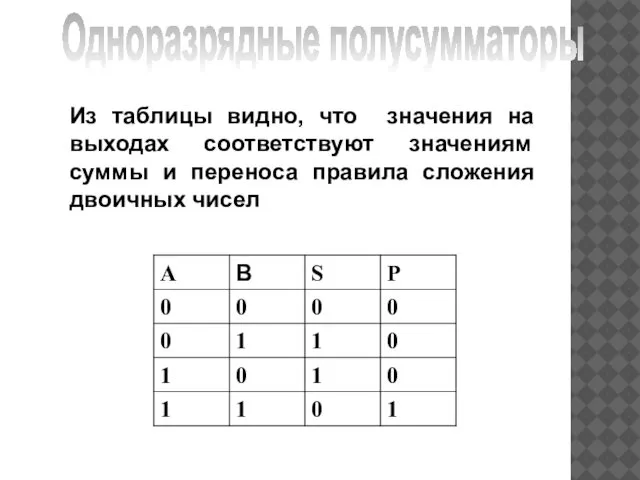

- 24. Одноразрядные полусумматоры Из таблицы видно, что значения на выходах соответствуют значениям суммы и переноса правила сложения

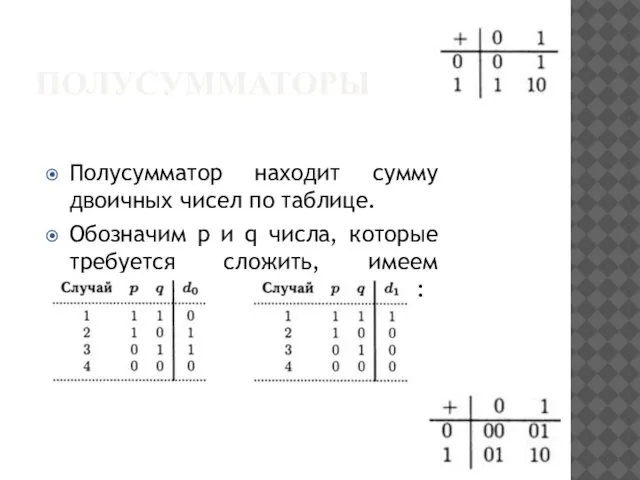

- 25. ПОЛУСУММАТОРЫ Полусумматор находит сумму двоичных чисел по таблице. Обозначим p и q числа, которые требуется сложить,

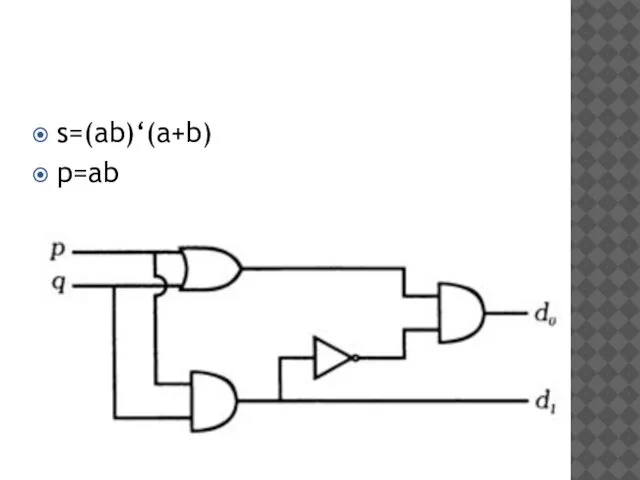

- 26. s=(ab)‘(a+b) p=ab

- 27. ПОЛНЫЙ ОДНОРАЗРЯДНЫЙ СУММАТОР Одноразрядный двоичный сумматор на три входа и два выхода называется полным одноразрядным сумматором.

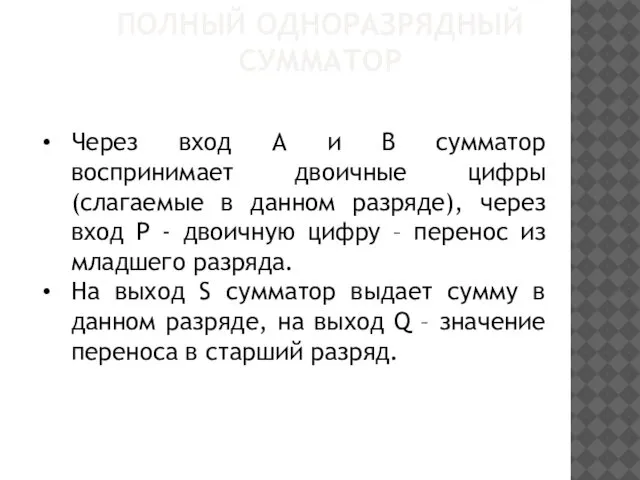

- 28. ПОЛНЫЙ ОДНОРАЗРЯДНЫЙ СУММАТОР Через вход A и B сумматор воспринимает двоичные цифры (слагаемые в данном разряде),

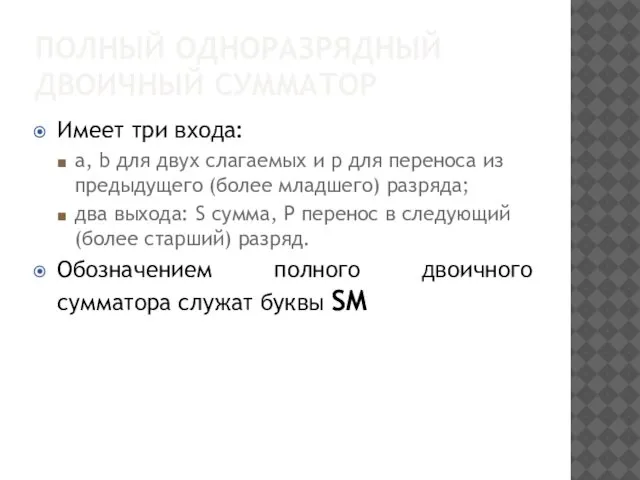

- 29. ПОЛНЫЙ ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР Имеет три входа: a, b для двух слагаемых и p для переноса

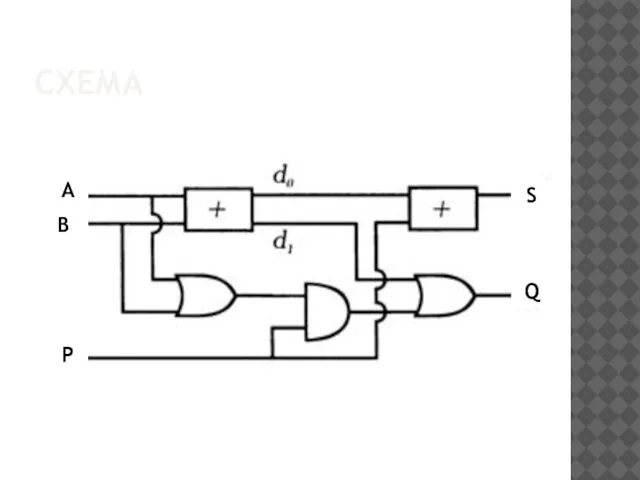

- 30. A – первый вход B – второй вход P – третий вход Q – перенос результата

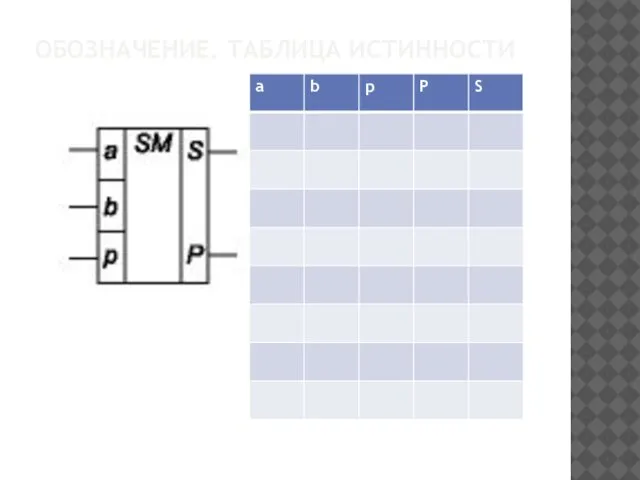

- 31. ОБОЗНАЧЕНИЕ. ТАБЛИЦА ИСТИННОСТИ

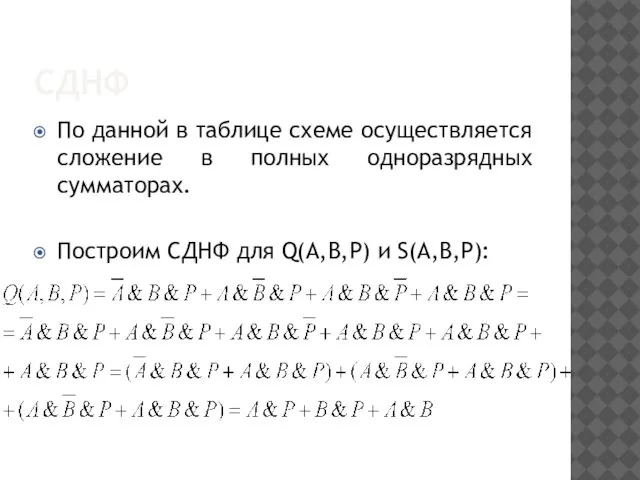

- 32. СДНФ По данной в таблице схеме осуществляется сложение в полных одноразрядных сумматорах. Построим СДНФ для Q(A,B,P)

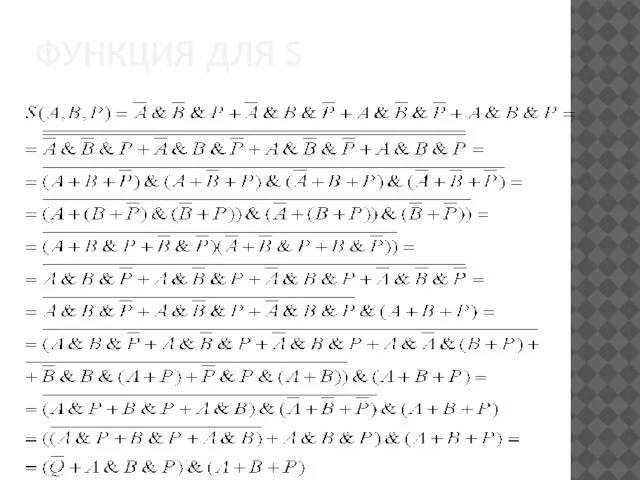

- 33. ФУНКЦИЯ ДЛЯ S

- 34. ПОЛУЧАЕМ СТРУКТУРНЫЕ ФОРМУЛЫ

- 35. СХЕМА A A A B P S Q

- 36. МНОГОРАЗРЯДНЫЕ ДВОИЧНЫЕ СУММАТОРЫ В зависимости от способа ввода кодов слагаемых сумматоры делятся на два типа: последовательного

- 37. ПОСЛЕДОВАТЕЛЬНЫЕ СУММАТОРЫ Последовательные сумматоры строятся на основе одноразрядной суммирующей схемы. В таких устройствах сложение двух чисел

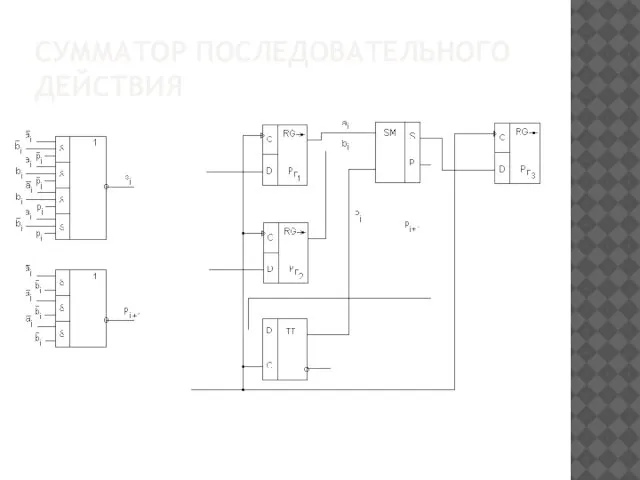

- 38. СУММАТОР ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ

- 39. ПАРАЛЛЕЛЬНЫЕ СУММАТОРЫ Параллельные сумматоры комбинационного типа представляют собой композиции одноразрядных суммирующих схем, причем обработка чисел в

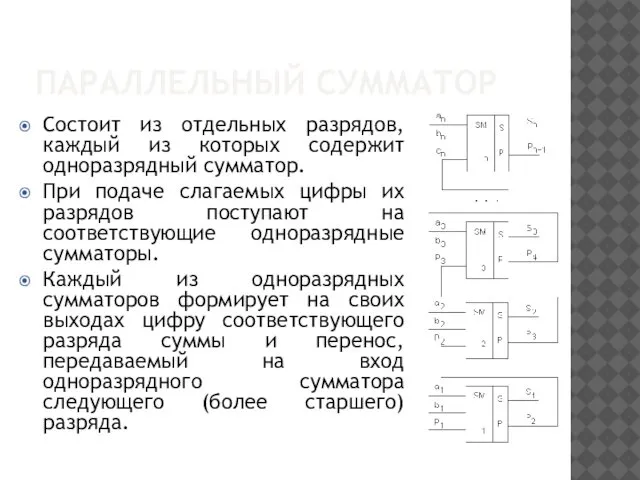

- 40. ПАРАЛЛЕЛЬНЫЙ СУММАТОР Состоит из отдельных разрядов, каждый из которых содержит одноразрядный сумматор. При подаче слагаемых цифры

- 41. ПАРАЛЛЕЛЬНЫЕ МНОГОРАЗРЯДНЫЕ СУММАТОРЫ Простейшими из параллельных сумматоров (ПС) являются ПС с последовательной передачей сигналов переноса. На

- 42. БЫСТРОДЕЙСТВИЕ СУММАТОРА Быстродействие сумматора при сложении двух n-разрядных чисел характеризуется временем суммирования, которое в наихудшем случае

- 43. ДЕСЯТИЧНЫЕ СУММАТОРЫ Для построения многоразрядных двоичных сумматоров, как было показано выше, необходимы одноразрядные двоичные сумматоры строятся

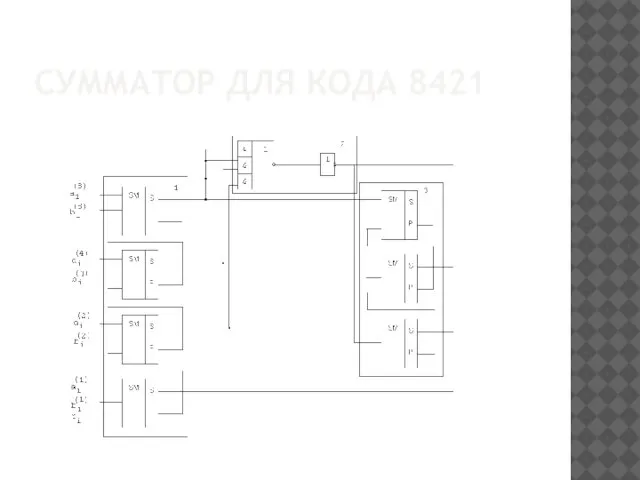

- 44. СУММАТОР ДЛЯ КОДА 8421

- 45. СХЕМА ФОРМИРОВАНИЯ ОБРАТНОГО КОДА В десятичной системе счисления обратный код образуется путем преобразования каждой цифры числа

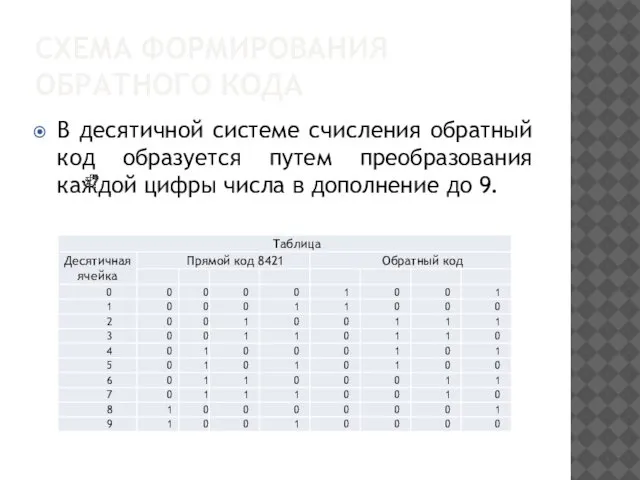

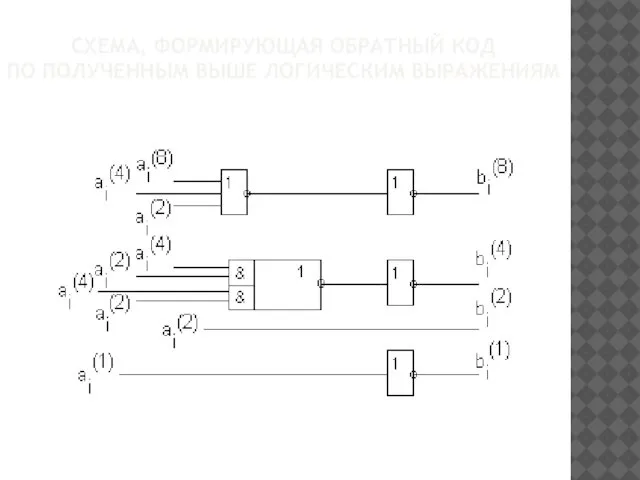

- 46. СХЕМА, ФОРМИРУЮЩАЯ ОБРАТНЫЙ КОД ПО ПОЛУЧЕННЫМ ВЫШЕ ЛОГИЧЕСКИМ ВЫРАЖЕНИЯМ

- 47. АРИФМЕТИКО-ЛОГИЧЕСКИЕ УСТРОЙСТВА Основными арифметическими операциями являются сложение и вычитание. Разработаны коды дополнительный и обратный, которые позволяют

- 48. Для повышения быстродействия ЭВМ разработаны и используются комбинированные арифметико-логические устройства, которые обеспечивают выполнение ряда арифметических и

- 49. МЕТОДИКА ПОСТРОЕНИЯ ОДНОРАЗРЯДНОГО АРИФМЕТИЧЕСКОГО УСТРОЙСТВА ДЛЯ ВЫПОЛНЕНИЯ ОПЕРАЦИЙ СУММИРОВАНИЯ И ВЫЧИТАНИЯ

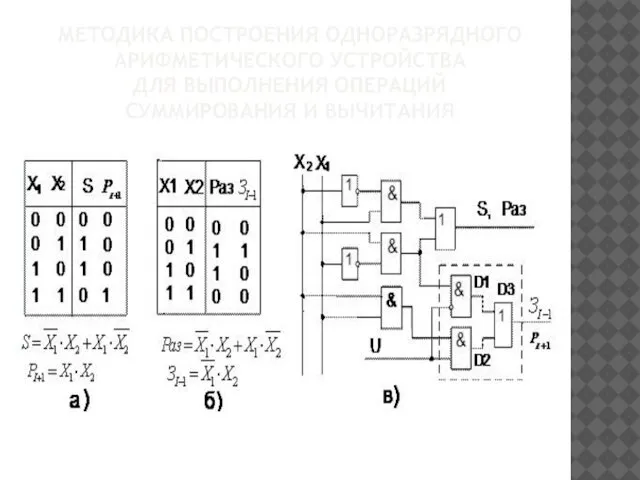

- 50. ОПЕРАЦИЯ ВЫЧИТАНИЯ Для выполнения операции вычитания не требуется получение дополнительных сигналов, поэтому и не требуются дополнительные

- 51. ВЫЧИТАНИЕ Вычитание числа В из А выполняется путем суммирования отрицательного числа В в дополнительном коде с

- 52. МНОГОРАЗРЯДНЫЕ АЛУ Многоразрядные АЛУ выпускаются в виде интегральных микросхем или входят в состав процессоров, являясь их

- 53. МС 564ИП3 (РИСУНОК 26,А) — ЭТО 4-РАЗРЯДНОЕ ПАРАЛЛЕЛЬНОЕ АЛУ, ВЫПОЛНЯЮЩАЯ 16 АРИФМЕТИЧЕСКИХ И 16 ЛОГИЧЕСКИХ ОПЕРАЦИЙ.

- 54. A(а0–а3) — первый операнд, B(b0–b3) — второй операнд, S(s0–s3) — код операции — 4 разряда. Если

- 56. Скачать презентацию

ЦСПА нового поколения

ЦСПА нового поколения Подбор и презентация турпродукта по запросу клиента: Подготовка курортного направления

Подбор и презентация турпродукта по запросу клиента: Подготовка курортного направления Весовой контроль сотрудников предприятия

Весовой контроль сотрудников предприятия Модуль Социально-культурная деятельность

Модуль Социально-культурная деятельность Приложение к протоколу/ Appendix to the report

Приложение к протоколу/ Appendix to the report Основные понятия и определения теории телетрафика

Основные понятия и определения теории телетрафика Азбука

Азбука местоимение. изменение по родам

местоимение. изменение по родам Планета сказок Юрия Магалифа

Планета сказок Юрия Магалифа Сонина дорога к искусству

Сонина дорога к искусству 9. Исключение грубых погрешностей измерений - промахов

9. Исключение грубых погрешностей измерений - промахов Определение режима работы колонны. Методы образования орошения и парового потока. Варианты устройства колонны

Определение режима работы колонны. Методы образования орошения и парового потока. Варианты устройства колонны Разработка веб-приложения доставка еды

Разработка веб-приложения доставка еды Unusual fashion

Unusual fashion Обучение персонала, обслуживающего трубопроводы пара и горячей воды

Обучение персонала, обслуживающего трубопроводы пара и горячей воды Жизнь в творчестве

Жизнь в творчестве 3чек_Бригада

3чек_Бригада Проект. Окружающий мир

Проект. Окружающий мир 20171228_edinstvo_dushi_i_zemli

20171228_edinstvo_dushi_i_zemli Аэропорты мира: Дюссельдорф и Гамбург

Аэропорты мира: Дюссельдорф и Гамбург Les jours de la semaine et les planètes

Les jours de la semaine et les planètes Зачистка поверхностей деталей из древесины

Зачистка поверхностей деталей из древесины Презентация ВКР

Презентация ВКР Статистика по директорам к курсу по Экономике _Андерсон_ (3)

Статистика по директорам к курсу по Экономике _Андерсон_ (3) Влияние лекарственных препаратов на плод человека

Влияние лекарственных препаратов на плод человека Анализ направлений логистической деятельности нефтегазовой организации (нефтегазового комплекса страны, региона)

Анализ направлений логистической деятельности нефтегазовой организации (нефтегазового комплекса страны, региона) Профориентация Мой город в радуге профессий

Профориентация Мой город в радуге профессий Преподобный Серафим Саровский

Преподобный Серафим Саровский