Содержание

- 2. Рисунок 1 – Условное графическое обозначение асинхронного RS-триггера (а), его логическая структура (б), временная диаграмма (в)

- 3. Рисунок 3.5.3 – Условное графическое обозначение D-триггера (а), его логическая структура (б), временная диаграмма (в) а)

- 4. Двухтактный JK-триггер (рисунок 5). Главная особенность триггера состоит в том, что переключение происходит по спаду тактовых

- 6. Скачать презентацию

Рисунок 1 – Условное графическое обозначение асинхронного RS-триггера (а),

его логическая

Рисунок 1 – Условное графическое обозначение асинхронного RS-триггера (а),

его логическая

а) б) в)

Таблица 1

Режимы работы асинхронного RS-триггера

Синхронный RS-триггер (рисунок 2) может быть получен на базе асинхронного RS-триггера. В большинстве схем необходимо переключение всех составляющих в определенный момент времени по сигналам тактового генератора. При этом добавляется третий синхронизирующий вход. Состояние синхронного RS-триггера изменяется при входных комбинациях R и S аналогично асинхронному RS-триггеру, но только в момент прихода тактового импульса на вход C. Переключение данного триггера возможно лишь при появлении положительного перепада импульса на тактовом перепаде C (таблица 2).

Рисунок 2 – Условное графическое обозначение синхронного RS-триггера (а), его логическая структура (б), временная диаграмма (в)

а) б)

Таблица 2

Режимы работы синхронного RS-триггера

в)

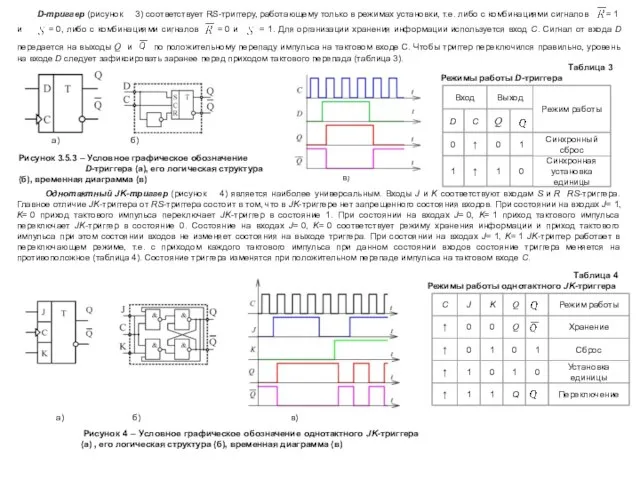

Рисунок 3.5.3 – Условное графическое обозначение

D-триггера (а), его логическая

Рисунок 3.5.3 – Условное графическое обозначение

D-триггера (а), его логическая

(б), временная диаграмма (в)

а) б)

Таблица 3

Режимы работы D-триггера

Однотактный JK-триггер (рисунок 4) является наиболее универсальным. Входы J и K соответствуют входам S и R RS-триггера. Главное отличие JK-триггера от RS-триггера состоит в том, что в JK-триггере нет запрещенного состояния входов. При состоянии на входах J= 1, K= 0 приход тактового импульса переключает JK-триггер в состояние 1. При состоянии на входах J= 0, K= 1 приход тактового импульса переключает JK-триггер в состояние 0. Состояние на входах J= 0, K= 0 соответствует режиму хранения информации и приход тактового импульса при этом состоянии входов не изменяет состояния на выходе триггера. При состоянии на входах J= 1, K= 1 JK-триггер работает в переключающем режиме, т.е. с приходом каждого тактового импульса при данном состоянии входов состояние триггера меняется на противоположное (таблица 4). Состояние триггера изменятся при положительном перепаде импульса на тактовом входе C.

Рисунок 4 – Условное графическое обозначение однотактного JK-триггера (а) , его логическая структура (б), временная диаграмма (в)

а) б) в)

Таблица 4

Режимы работы однотактного JK-триггера

в)

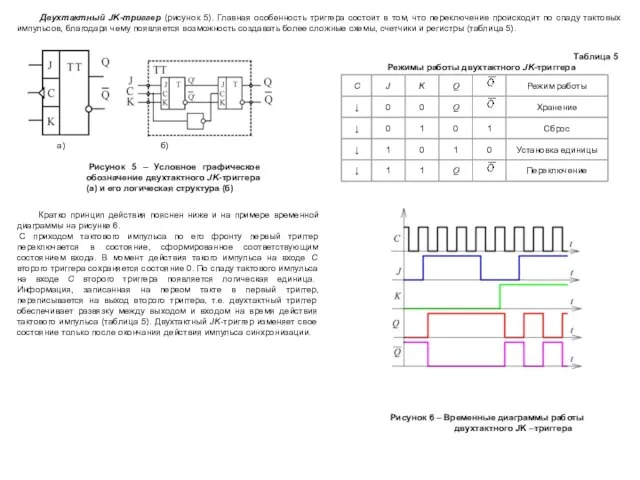

Двухтактный JK-триггер (рисунок 5). Главная особенность триггера состоит в том,

Двухтактный JK-триггер (рисунок 5). Главная особенность триггера состоит в том,

Рисунок 5 – Условное графическое обозначение двухтактного JK-триггера (а) и его логическая структура (б)

а) б)

Таблица 5

Режимы работы двухтактного JK-триггера

Кратко принцип действия пояснен ниже и на примере временной диаграммы на рисунке 6.

С приходом тактового импульса по его фронту первый триггер переключается в состояние, сформированное соответствующим состоянием входа. В момент действия такого импульса на входе C второго триггера сохраняется состояние 0. По спаду тактового импульса на входе C второго триггера появляется логическая единица. Информация, записанная на первом такте в первый триггер, переписывается на выход второго триггера, т.е. двухтактный триггер обеспечивает развязку между выходом и входом на время действия тактового импульса (таблица 5). Двухтактный JK-триггер изменяет свое состояние только после окончания действия импульса синхронизации.

Рисунок 6 – Временные диаграммы работы

двухтактного JK –триггера

Компоновка и конструкции деталей корпусной мебели

Компоновка и конструкции деталей корпусной мебели занятие1 Марина

занятие1 Марина Машины для посева

Машины для посева Аттестационная работа

Аттестационная работа School_Memory game

School_Memory game Мир авиации

Мир авиации Вычислительные комплексы в расчетах строительных конструкций

Вычислительные комплексы в расчетах строительных конструкций 20170327_3-2

20170327_3-2 Шешендік нерді насихаттау жолдары

Шешендік нерді насихаттау жолдары РФ-работа

РФ-работа ЗОЖ - лайфхаки для студентов

ЗОЖ - лайфхаки для студентов Презентация Час безопасности по БДД август 2022г. Новойл

Презентация Час безопасности по БДД август 2022г. Новойл СОВРЕМЕННЫЙ РУССКИЙ ЯЗЫК

СОВРЕМЕННЫЙ РУССКИЙ ЯЗЫК Причины возникновения ошибок при передаче текста Нового Завета

Причины возникновения ошибок при передаче текста Нового Завета Война в судьбе моей семьи

Война в судьбе моей семьи What can animal do

What can animal do Подача мяча двумя руками из-за головы. Игра Перестрелка

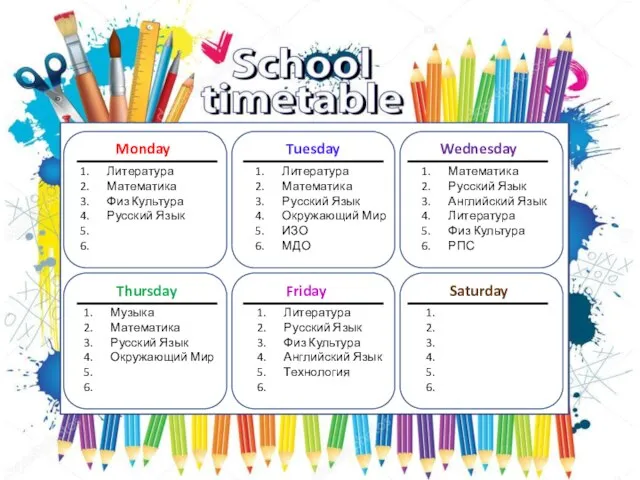

Подача мяча двумя руками из-за головы. Игра Перестрелка School timetable

School timetable Воспитание толерантности на уроках социальных дисциплин

Воспитание толерантности на уроках социальных дисциплин Электротехника и электроника

Электротехника и электроника Читайте детям книги

Читайте детям книги Измерение частоты и интервалов времени

Измерение частоты и интервалов времени 17 сентября 2017 года - День работников леса

17 сентября 2017 года - День работников леса Презентация МБ практика иммунитет

Презентация МБ практика иммунитет Поздравь свою библиотеку

Поздравь свою библиотеку Выбор направлений развития производственной системы судостроения

Выбор направлений развития производственной системы судостроения Понятие и длительность производственного цикла

Понятие и длительность производственного цикла Раскрой плечевого изделия

Раскрой плечевого изделия