Содержание

- 2. Дисциплина «Структура компьютерных средств» Тема №7 «Процессоры» Занятие №2/2 «Архитектура процессоров»

- 3. Учебные вопросы: Процессоры с различной архитектурой. Архитектура многоядерных процессоров. Цели занятия: Знать архитектуры процессоров; Иметь представление

- 4. Учебный вопрос №1. «Процессоры с различной архитектурой» Основными отличительными характеристиками каждой отдельной архитектуры являются: размер и

- 5. Вопрос №1. «Процессоры с различной архитектурой» Процессоры с архитектурой CISC Основную идею CISC-архитектуры отражает ее название

- 6. Вопрос №1. «Процессоры с различной архитектурой» Черты организации CISC-процессоров: большое количество различных машинных команд (сотни), каждая

- 7. Вопрос №1. «Процессоры с различной архитектурой» Процессоры с архитектурой RISC Особое внимание к RISC-архитектуре обусловлено тем,

- 8. Концепцию RISC-процессора можно свести к следующим положениям: выполнение почти всех (75% команд) за один цикл; стандартная

- 9. Вопрос №1. «Процессоры с различной архитектурой» Преимущества RISC Для технологии RISC характерна сравнительно простая структура УУ.

- 10. Недостатки RISC Принципиальный недостаток - сокращенное число команд: на выполнение ряда функций приходится тратить несколько команд

- 11. Процессоры с архитектурой VLIW Архитектура с командными словами сверхбольшой длины или со сверхдлинными командами (VLIW, Very

- 12. Объединение нескольких простых команд в одну сверхдлинную производится по следующим правилам: количество простых команд, объединяемых в

- 13. Рис. 7.19. Формат сверхдлинной команды и взаимосвязь полей команды с составляющими блока исполнения Вопрос №1. «Процессоры

- 14. Двумя проблемами VLIW-архитектуры являются: ■ усложнение регистрового файла и, прежде всего, связей этого файла с вычислительными

- 15. Процессоры с архитектурой EPIC Дальнейшим развитием идеи VLIW стала архитектура EPIC (Explicitly Parallel Instruction Computing) -

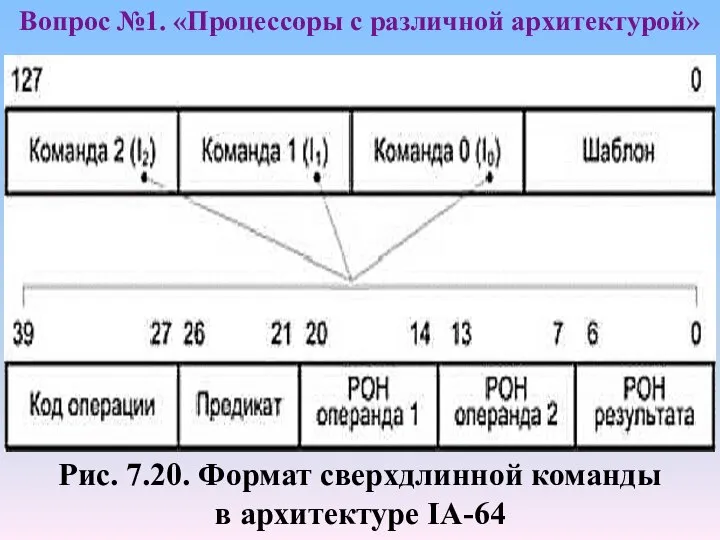

- 16. В архитектуре EPIC, которая в изделиях Intel получила название IA-64 (Intel Architecture - 64), предполагается наличие

- 17. Рис. 7.20. Формат сверхдлинной команды в архитектуре IA-64 Вопрос №1. «Процессоры с различной архитектурой»

- 18. Особенностями архитектуры EPIC являются: большое количество регистров; масштабируемость архитектуры до большого количества функциональных блоков. Это свойство

- 19. Учебный вопрос №2. «Архитектура многоядерных процессоров» Многоядерный процессор - это центральный процессор, содержащий два и более

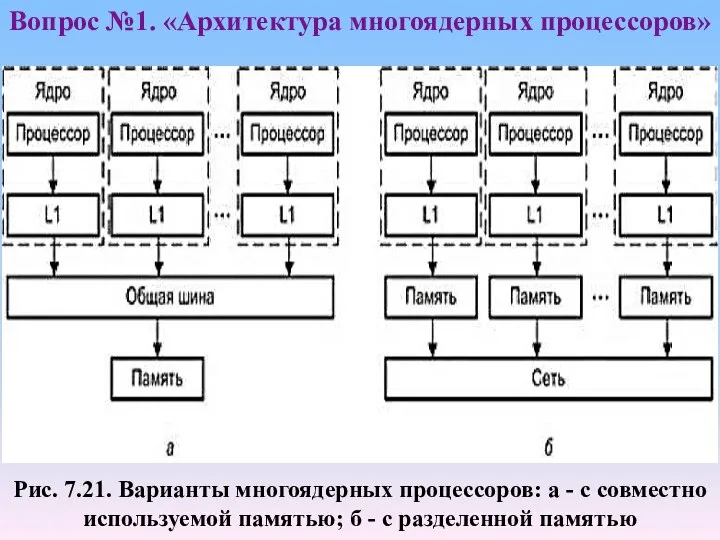

- 20. Рис. 7.21. Варианты многоядерных процессоров: а - с совместно используемой памятью; б - с разделенной памятью

- 22. Скачать презентацию

Обобщение знаний об имени прилагательном - презентация для начальной школы

Обобщение знаний об имени прилагательном - презентация для начальной школы Евроклуб При 78 СОУ “Христо Смирненски”

Евроклуб При 78 СОУ “Христо Смирненски” Методы расчета и уменьшения аддитивных и мультипликативных погрешностей цепей на ОУ

Методы расчета и уменьшения аддитивных и мультипликативных погрешностей цепей на ОУ Методы выгружения

Методы выгружения Рабочие программы дисциплин

Рабочие программы дисциплин Фокина Л. П. Интеллектуальный марафон - 4 - презентация для начальной школы

Фокина Л. П. Интеллектуальный марафон - 4 - презентация для начальной школы autumn-classroom-posters_73895

autumn-classroom-posters_73895 Списания и работа с браком. Урок 7

Списания и работа с браком. Урок 7 Передача информации. Локальные компьютерные сети

Передача информации. Локальные компьютерные сети государство

государство Системы безопасности Сименс

Системы безопасности Сименс 《汉语口语速成 基础篇》

《汉语口语速成 基础篇》 Іудаїзм - перша монотеїстична релігія

Іудаїзм - перша монотеїстична релігія АТТЕСТАЦИЯ как элемент планирования карьеры

АТТЕСТАЦИЯ как элемент планирования карьеры Провідникові матеріали. Класифікація провідникових матеріалів

Провідникові матеріали. Класифікація провідникових матеріалів Экономика стран Евразийского экономического сообщества

Экономика стран Евразийского экономического сообщества Презентация на тему "ОГЭ2015" - скачать презентации по Педагогике

Презентация на тему "ОГЭ2015" - скачать презентации по Педагогике Министерство Здравоохранения Украины Запорожский Государственный Медицинский Университет Доклад на тему:Туберкулёз височ

Министерство Здравоохранения Украины Запорожский Государственный Медицинский Университет Доклад на тему:Туберкулёз височ Контроль-функции менеджмента

Контроль-функции менеджмента  Создание простейшего графического приложения. Microsoft Visual. Studio Visual. C++ Windows. Forms GDI+

Создание простейшего графического приложения. Microsoft Visual. Studio Visual. C++ Windows. Forms GDI+ Постановка концепции исследования

Постановка концепции исследования  Спортивная инфраструктура Института физической культуры, спорта и туризма ПетрГУ

Спортивная инфраструктура Института физической культуры, спорта и туризма ПетрГУ Красноярский медицинский университет им.проф.В.Ф.Войно-Ясенецкого.

Красноярский медицинский университет им.проф.В.Ф.Войно-Ясенецкого.  Функции политической власти

Функции политической власти Киборги. Новейшее время и киборгизация

Киборги. Новейшее время и киборгизация . Побег и почки

. Побег и почки Пожарная безопасность в России

Пожарная безопасность в России Тісті берілістер

Тісті берілістер