Содержание

- 2. схемы сброса регистров по сигналу PowerGood от БП или кнопки Reset управления напряжением измерений температуры

- 3. Н-р, формата mini ATX с PCI-E 16x

- 4. ATX с двумя PCI-E 16x и WiFi

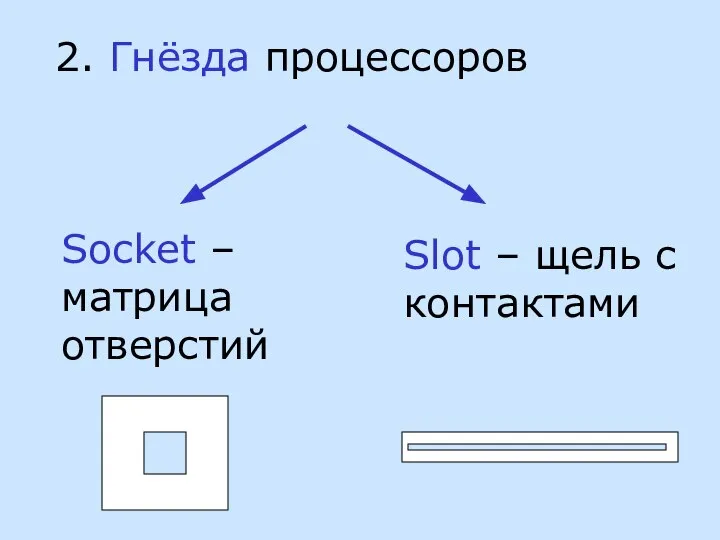

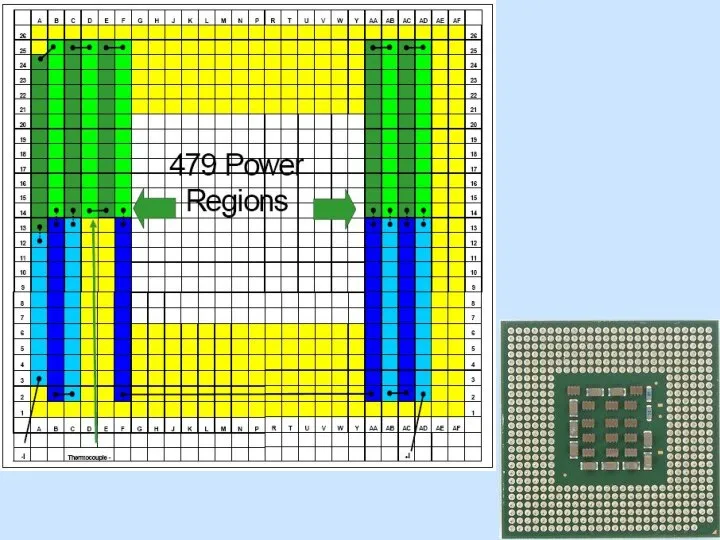

- 5. 2. Гнёзда процессоров Socket – матрица отверстий Slot – щель с контактами

- 6. Гнёзда отличаются также количеством контактов их расположением напряжением Будьте внимательны!

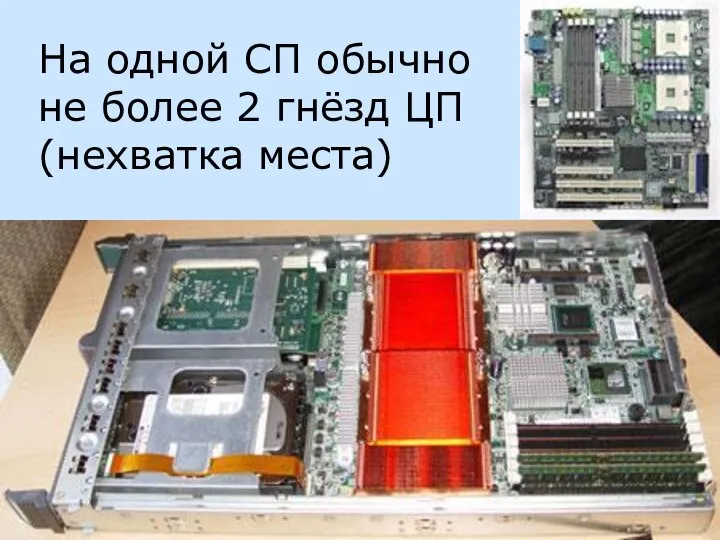

- 9. На одной СП обычно не более 2 гнёзд ЦП (нехватка места)

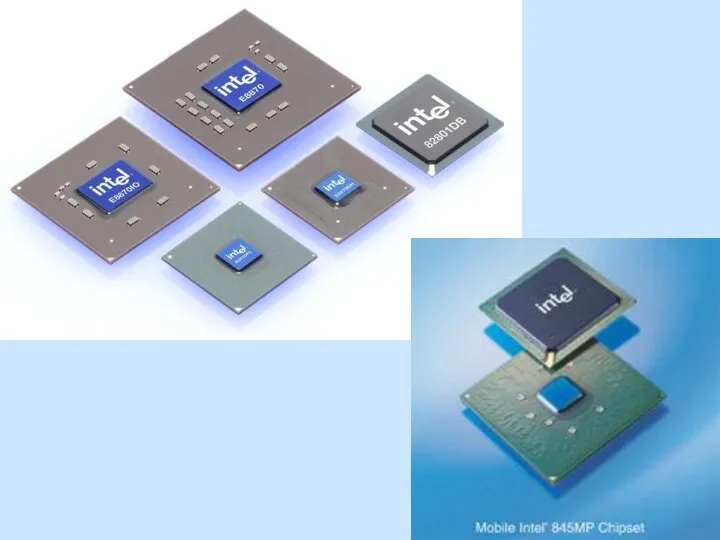

- 10. 3. Чипсет а) Это набор БИС с контроллерами интерфейсов (набор микросхем системной логики)

- 12. Чипсет рассчитан только на определённые типы ЦП и ОЗУ Заметно (н-р, 30%) влияет на производительность ПК

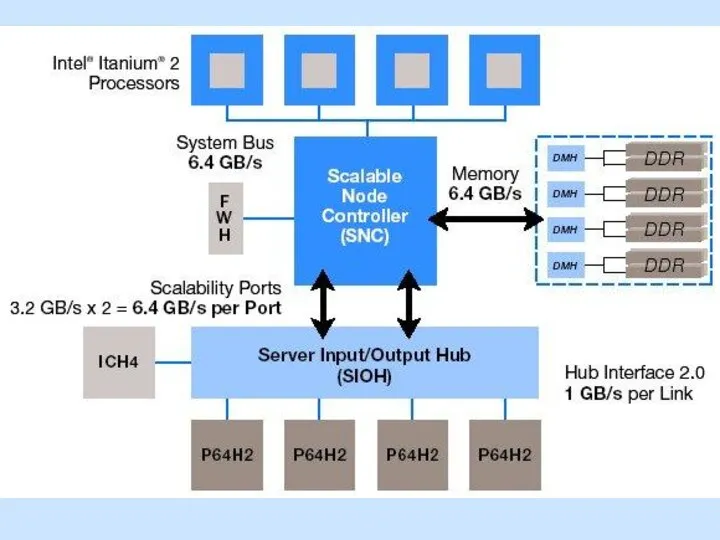

- 13. б) Архитектура North/South Bridge Две БИС: Север – быстрый: ЦП – ОЗУ – видеокарта – IRQ,

- 14. Замечание: Intel называет современную мостовую схему Hub-архитектурой Hub – центр, ядро, пуп

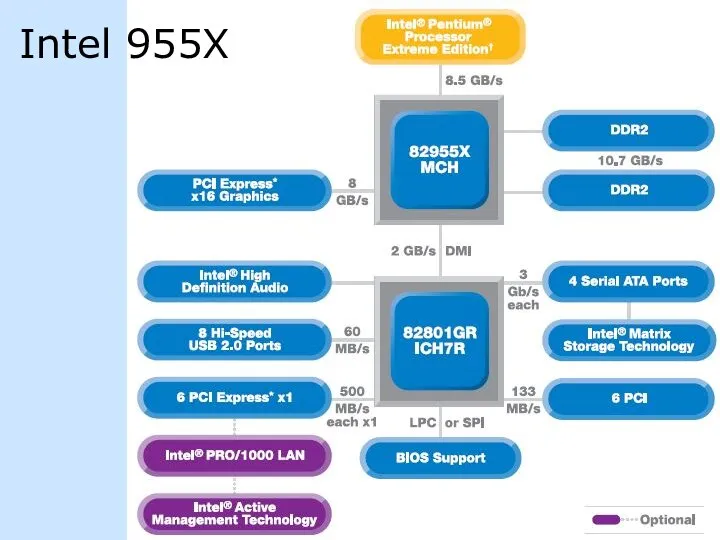

- 15. Здесь «хабы» – концентраторы контроллеров на севере: MCH – main controller hub на юге: ICH –

- 16. Intel 955X

- 17. в) Замечания Возможности СП зависят не только от чипсета, но и - других БИС - BIOS

- 18. чипсет настраивается во время POST биты настроек читаются из ПЗУ их можно менять в CMOS Setup

- 19. Передаёт адреса, данные и сигналы управления между ЦП, ОЗУ и северным мостом шины: адресов данных (в

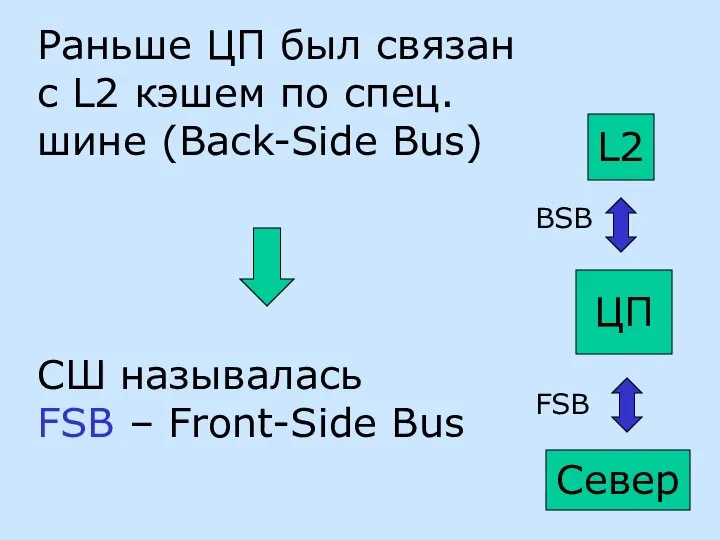

- 20. Раньше ЦП был связан с L2 кэшем по спец. шине (Back-Side Bus) ЦП L2 Север BSB

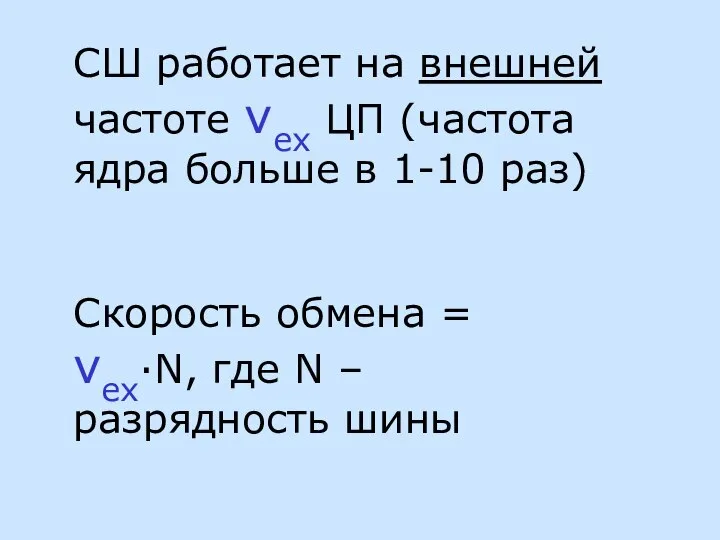

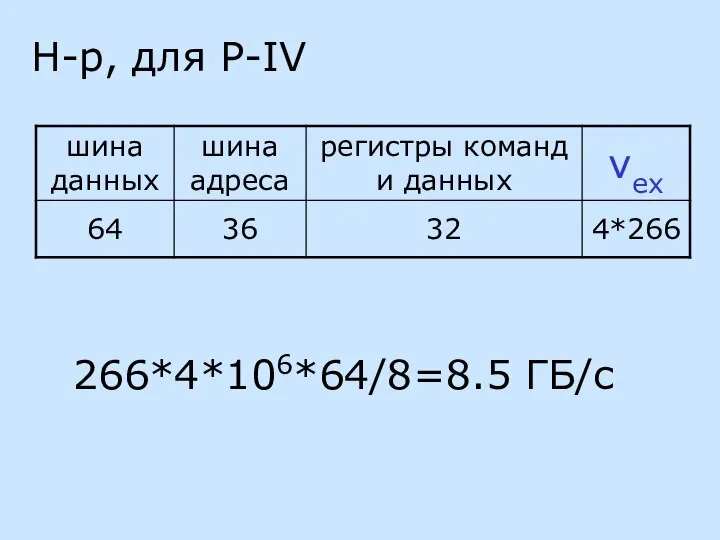

- 21. СШ работает на внешней частоте νex ЦП (частота ядра больше в 1-10 раз) Скорость обмена =

- 22. Н-р, для P-IV 266*4*106*64/8=8.5 ГБ/с

- 23. 5. Шина памяти - между чипсетом и ОЗУ Иногда является частью СШ север ЦП ОЗУ СШ

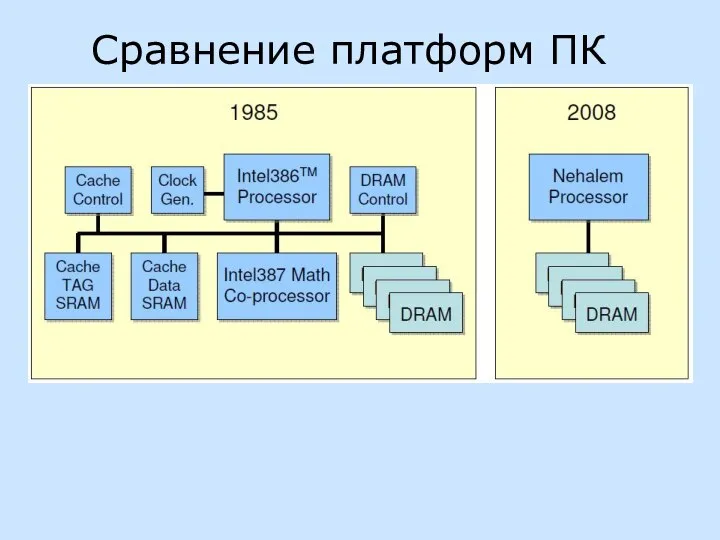

- 25. Сравнение платформ ПК

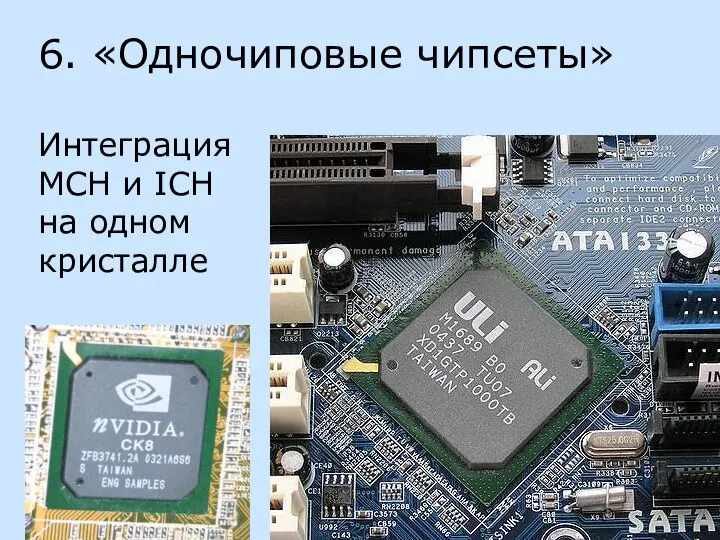

- 26. 6. «Одночиповые чипсеты» Интеграция MCH и ICH на одном кристалле

- 28. Скачать презентацию

Интервью и ТЗ. Инженерия

Интервью и ТЗ. Инженерия Жизнь и творчество Ивана Сергеевича Тургенева

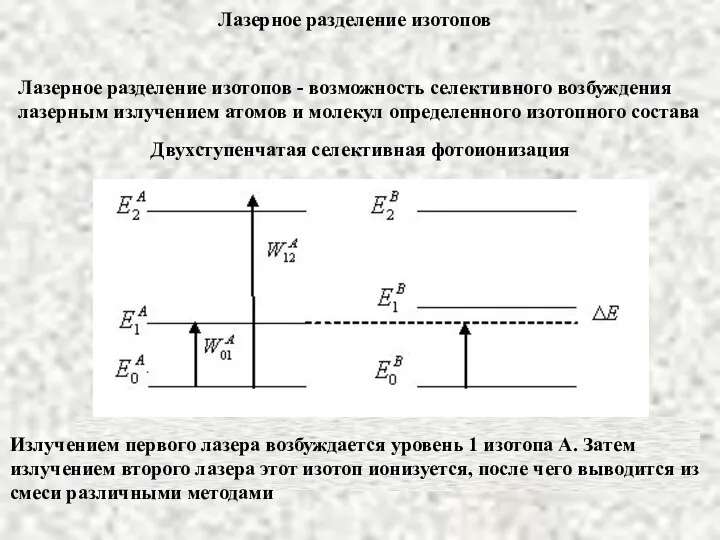

Жизнь и творчество Ивана Сергеевича Тургенева Лазерное разделение изотопов

Лазерное разделение изотопов  Фреймы в HTML

Фреймы в HTML Қазақтың сүт өнімдері. Сүт өнімдерінің адам ағзасына пайдасы

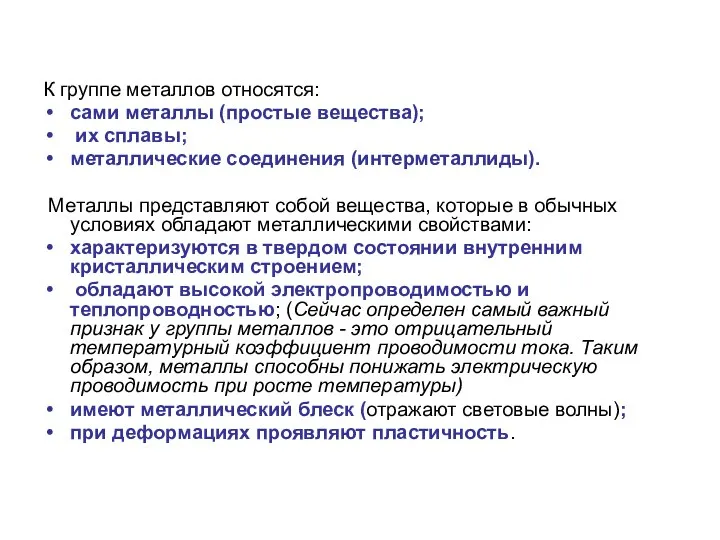

Қазақтың сүт өнімдері. Сүт өнімдерінің адам ағзасына пайдасы Промышленная классификация металлов

Промышленная классификация металлов Назначение и состав инженерно-геодезических изысканий. Технические требования к выбору положения сооружения. (Лекция 5)

Назначение и состав инженерно-геодезических изысканий. Технические требования к выбору положения сооружения. (Лекция 5) Презентация к уроку МХК по теме «Виды искусств». Выполнена учителем МХК Карпухиной И.В.

Презентация к уроку МХК по теме «Виды искусств». Выполнена учителем МХК Карпухиной И.В. Les symboles du l'Ukraine

Les symboles du l'Ukraine Названия животных в Псалтири

Названия животных в Псалтири Post 9/11 Society

Post 9/11 Society Презентация Бюджетная система ФРГ

Презентация Бюджетная система ФРГ  Теорема Менелая и теорема Чевы в школьном курсе математики

Теорема Менелая и теорема Чевы в школьном курсе математики  Физико-химические свойства смесей бензина с этанолом

Физико-химические свойства смесей бензина с этанолом  Posix threads

Posix threads  Масленица

Масленица Die Wiedervereinigung Deutschlands. Präteritum Passiv

Die Wiedervereinigung Deutschlands. Präteritum Passiv Автоматизация технологических процессов и производств

Автоматизация технологических процессов и производств  Green Building Materials

Green Building Materials История успеха компании Apple

История успеха компании Apple Разработка стратегии развития отрасли «жилищное строительство»

Разработка стратегии развития отрасли «жилищное строительство» Банк саласындағы аударма

Банк саласындағы аударма Геополитика исламского мира

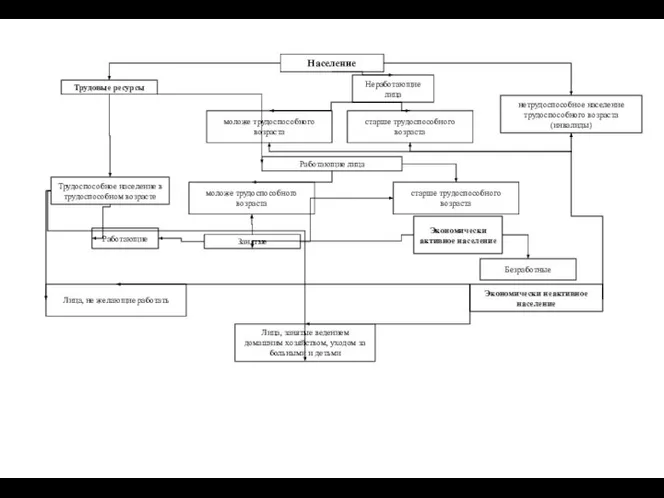

Геополитика исламского мира Трудовые ресурсы

Трудовые ресурсы Экологические основы паразитизма в типе Круглые черви

Экологические основы паразитизма в типе Круглые черви Наследование в программировании

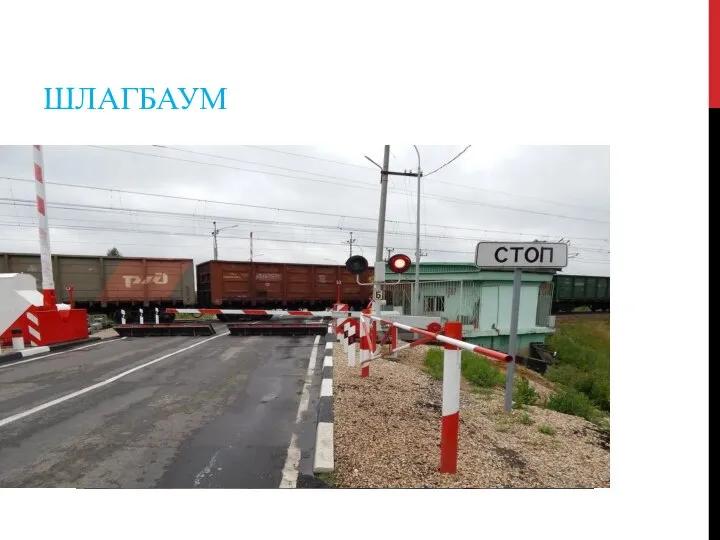

Наследование в программировании Шлагбаум со светофором. Проект

Шлагбаум со светофором. Проект Памп-трек в г. Дубна

Памп-трек в г. Дубна