Содержание

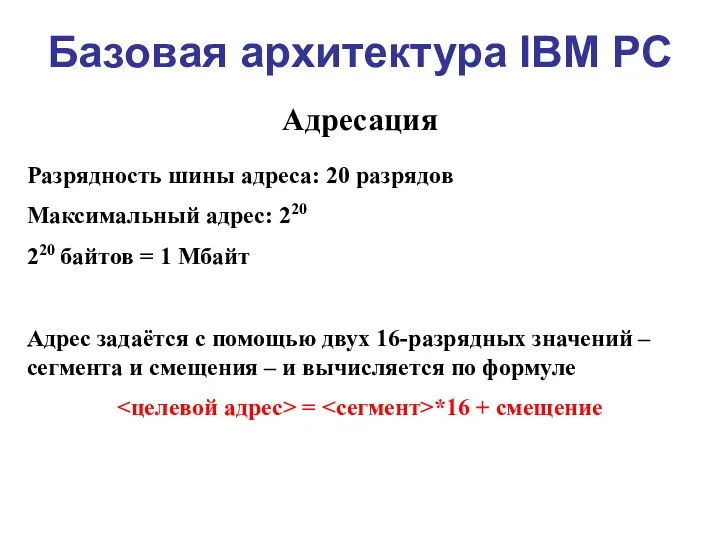

- 2. Базовая архитектура IBM PC Адресация Разрядность шины адреса: 20 разрядов Максимальный адрес: 220 220 байтов =

- 3. Базовая архитектура IBM PC Система команд Команды пересылки: а) между регистрами и памятью; б) между регистрами

- 4. Базовая архитектура IBM PC Организация вычислительного процесса Вычислительный процесс организован в полном соответствии с принципами фон

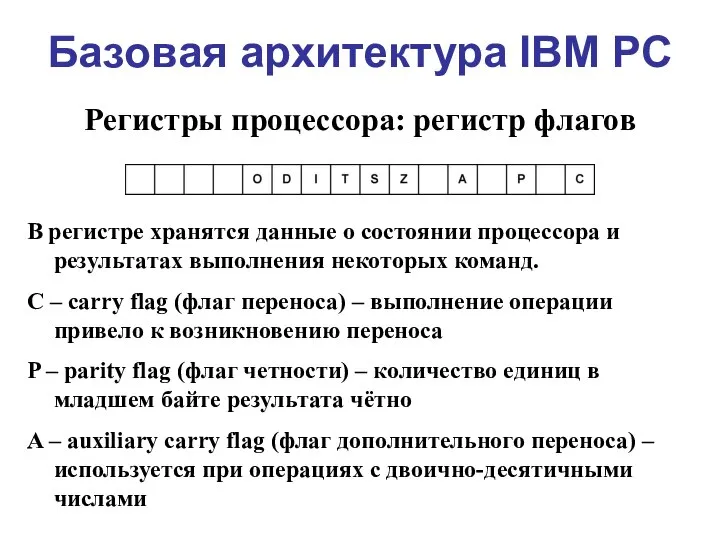

- 5. Базовая архитектура IBM PC Регистры процессора: регистр флагов В регистре хранятся данные о состоянии процессора и

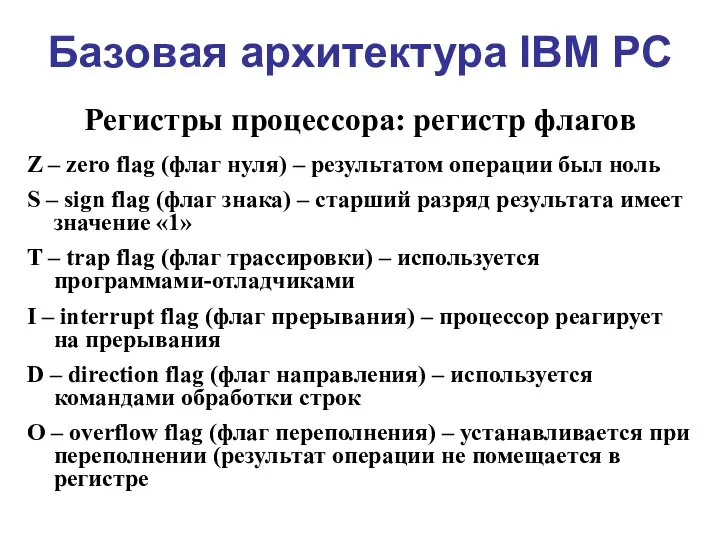

- 6. Базовая архитектура IBM PC Регистры процессора: регистр флагов Z – zero flag (флаг нуля) – результатом

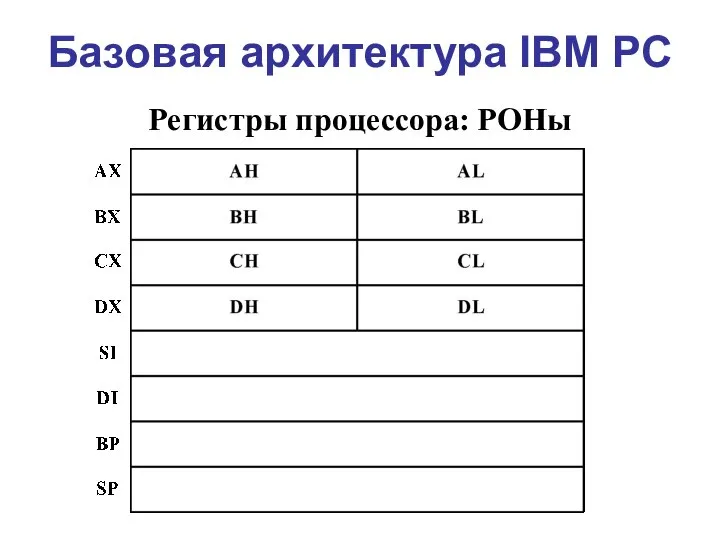

- 7. Базовая архитектура IBM PC Регистры процессора: РОНы

- 8. Базовая архитектура IBM PC Регистры процессора: РОНы Регистр AX (accumulator, аккумулятор) Это регистр-накопитель. Наиболее эффективно его

- 9. Базовая архитектура IBM PC Регистры процессора: РОНы Регистр BX (base, базовый регистр) В некоторых операциях этот

- 10. Базовая архитектура IBM PC Регистры процессора: РОНы Регистр CX (counter, счётчик) Обычно этот регистр используется как

- 11. Базовая архитектура IBM PC Регистры процессора: РОНы Регистр DX (data, регистр данных) Этот регистр используется в

- 12. Базовая архитектура IBM PC Регистры процессора: РОНы Регистры SI, DI Индексные регистры источника (SI, source index)

- 13. Базовая архитектура IBM PC Регистры процессора: РОНы Регистр BP Базовый регистр, в котором содержится смещение относительно

- 14. Базовая архитектура IBM PC Регистры процессора: РОНы Регистр SP (stack pointer, указатель стека) В SP содержится

- 15. Базовая архитектура IBM PC Регистры процессора: РОНы Регистр IP (instruction pointer, счётчик команд) Регистр содержит адрес

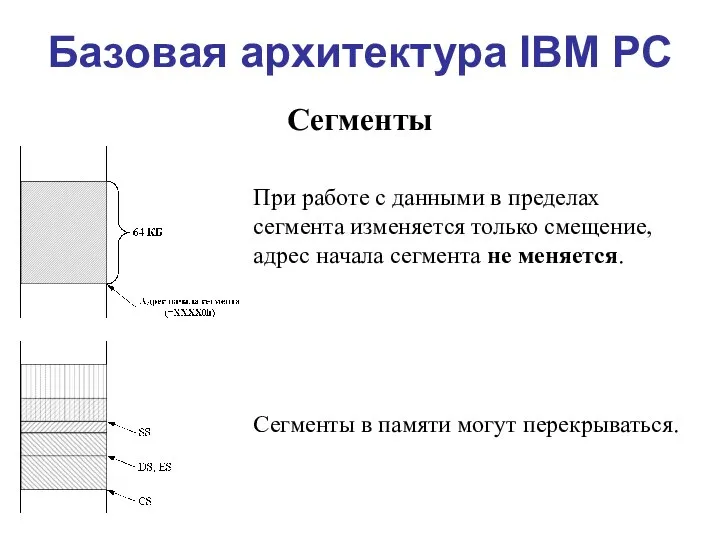

- 16. Базовая архитектура IBM PC Сегменты При работе с данными в пределах сегмента изменяется только смещение, адрес

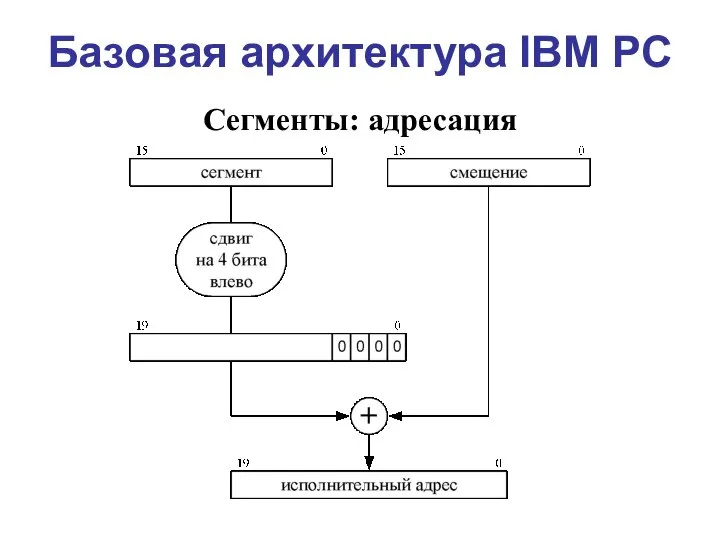

- 17. Базовая архитектура IBM PC Сегменты: адресация

- 18. Базовая архитектура IBM PC Регистры процессора: сегментные регистры CS (code segment) – указывает на сегмент, в

- 19. Базовая архитектура IBM PC Система прерываний Предусмотрены прерывания аппаратные и программные. Всего в системе может быть

- 21. Скачать презентацию

Начертательная геометрия. Точка и линия на поверхности. Коноид. Тело вращения. Геликоид

Начертательная геометрия. Точка и линия на поверхности. Коноид. Тело вращения. Геликоид Режимы работы и функциональные возможности САРП

Режимы работы и функциональные возможности САРП Потоки. Работа с потоками

Потоки. Работа с потоками Адресация в Интернете

Адресация в Интернете Понятие конституционных прав и свобод человека и гражданина, их классификация.

Понятие конституционных прав и свобод человека и гражданина, их классификация.  Инвенция

Инвенция  Деньги и товар как экономические категории. ЭБ01/1601 Коньшина Юлия Гарчагодашвили Кирилл

Деньги и товар как экономические категории. ЭБ01/1601 Коньшина Юлия Гарчагодашвили Кирилл  Научно-техническая цивилизация и ноосфера

Научно-техническая цивилизация и ноосфера Стандартизация в России

Стандартизация в России Сақтандыру компаниясы. Қазақстан Республикасындағы сақтандыру қызметінің қалыптасу жағдайына

Сақтандыру компаниясы. Қазақстан Республикасындағы сақтандыру қызметінің қалыптасу жағдайына ММА. What is UFC

ММА. What is UFC Методы обработки речевых сигналов в задаче распознавания

Методы обработки речевых сигналов в задаче распознавания Возрождение традиционного вепсского ремесла - ткачества

Возрождение традиционного вепсского ремесла - ткачества МИРОВАЯ ХУДОЖЕСТВЕННАЯ КУЛЬТУРА

МИРОВАЯ ХУДОЖЕСТВЕННАЯ КУЛЬТУРА Основные источники современного российского конституционного права, их соотношение с источниками налогового права. Тема 2

Основные источники современного российского конституционного права, их соотношение с источниками налогового права. Тема 2 Paul’s Sermon on Mars’ Hill

Paul’s Sermon on Mars’ Hill Перемещение товаров трубопроводным транспортом; особенности таможенного оформления и контроля. Подготовили: Белоусов Евгений и

Перемещение товаров трубопроводным транспортом; особенности таможенного оформления и контроля. Подготовили: Белоусов Евгений и  Стихи Маршака - 2 - презентация для начальной школы

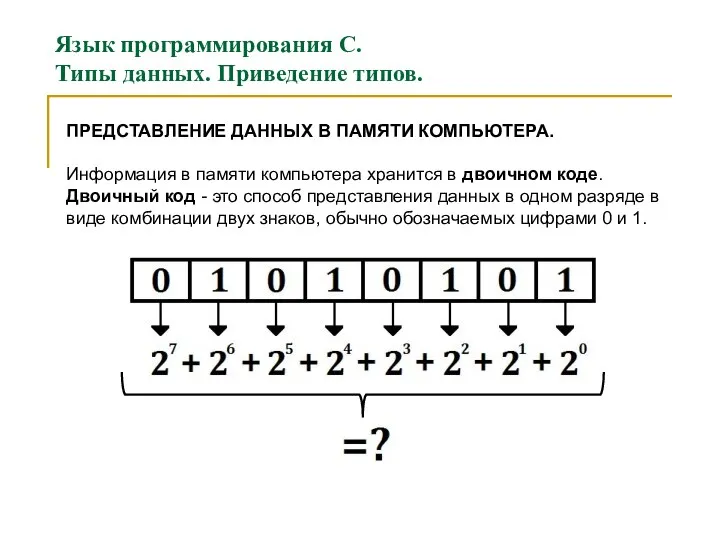

Стихи Маршака - 2 - презентация для начальной школы Язык программирования С. Типы данных. Приведение типов. (Лекция 4)

Язык программирования С. Типы данных. Приведение типов. (Лекция 4) Радіолокація. Історія розвитку радіолокації

Радіолокація. Історія розвитку радіолокації класс государство

класс государство Нормативно-правовые аспекты психологомедико-педагогического сопровождения детей с ограниченными возможностями здоровья

Нормативно-правовые аспекты психологомедико-педагогического сопровождения детей с ограниченными возможностями здоровья Фармакотерапия антитромбоцитарными, антикоагулянтными и фибринолитическими препаратами в клинике внутренних болезней Кафе

Фармакотерапия антитромбоцитарными, антикоагулянтными и фибринолитическими препаратами в клинике внутренних болезней Кафе Презентация Характеристика стран с переходной экономикой

Презентация Характеристика стран с переходной экономикой Как помочь ребенку справиться со стрессом во время ЕГЭ (Памятка организатору)

Как помочь ребенку справиться со стрессом во время ЕГЭ (Памятка организатору) ВЫДЕЛЕНИЕ-2 Дистальные канальца Собирательные трубочки

ВЫДЕЛЕНИЕ-2 Дистальные канальца Собирательные трубочки  Богатые Домашнее задание: параграф

Богатые Домашнее задание: параграф «ДОБРЫХ РУК МАСТЕРСТВО». Публичное выступление – представление исследовательского проекта о произведениях декоративно-п

«ДОБРЫХ РУК МАСТЕРСТВО». Публичное выступление – представление исследовательского проекта о произведениях декоративно-п