Содержание

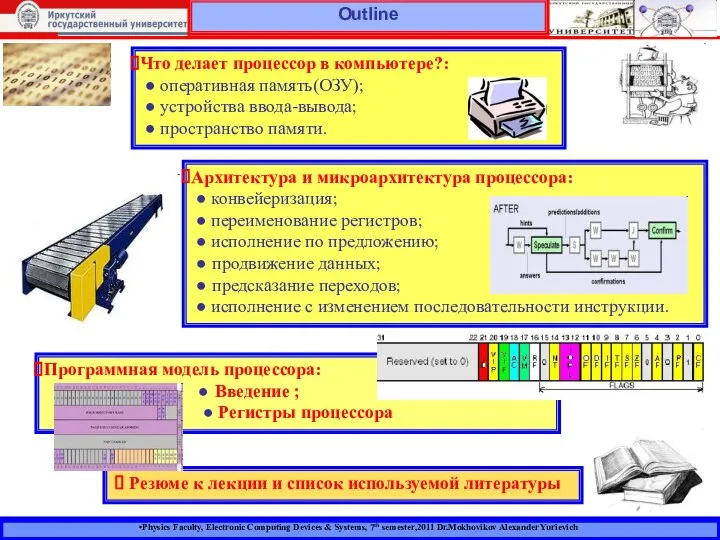

- 2. Physics Faculty, Electronic Computing Devices & Systems, 7th semester,2011 Dr.Mokhovikov Alexander Yurievich Outline Что делает процессор

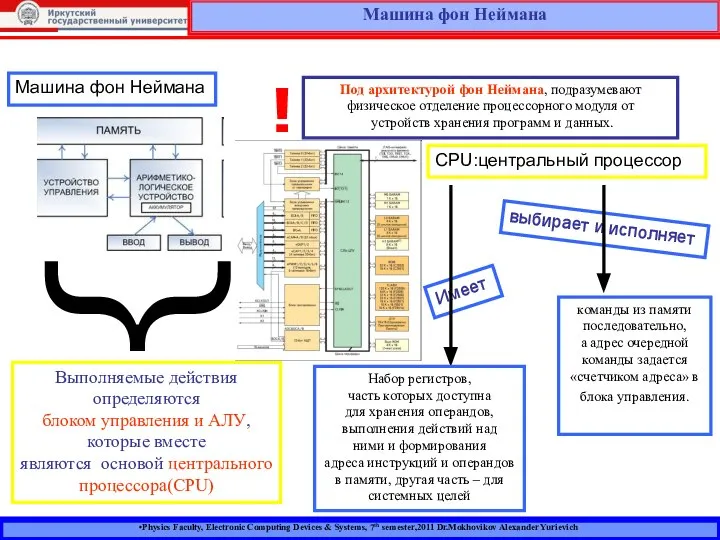

- 3. Под архитектурой фон Неймана, подразумевают физическое отделение процессорного модуля от устройств хранения программ и данных. !

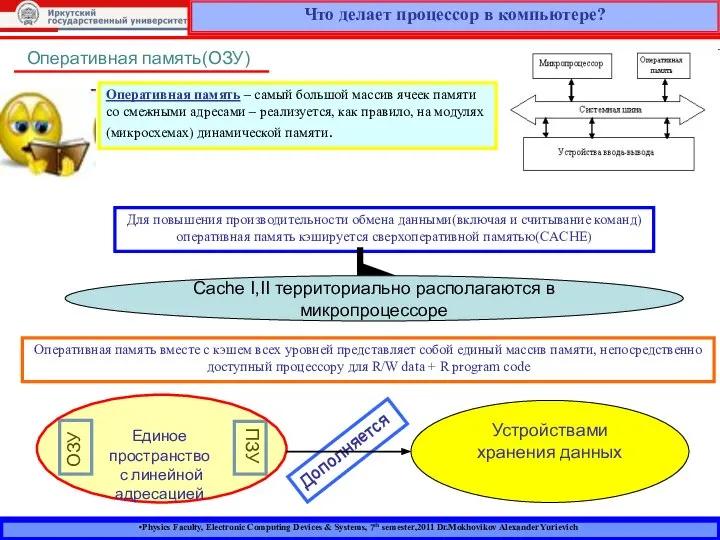

- 4. Оперативная память(ОЗУ) Оперативная память – самый большой массив ячеек памяти со смежными адресами – реализуется, как

- 5. Устройства ввода-вывода Служат для преобразования информации из внутреннего представления в компьютере(биты и байты) в форму, доступную

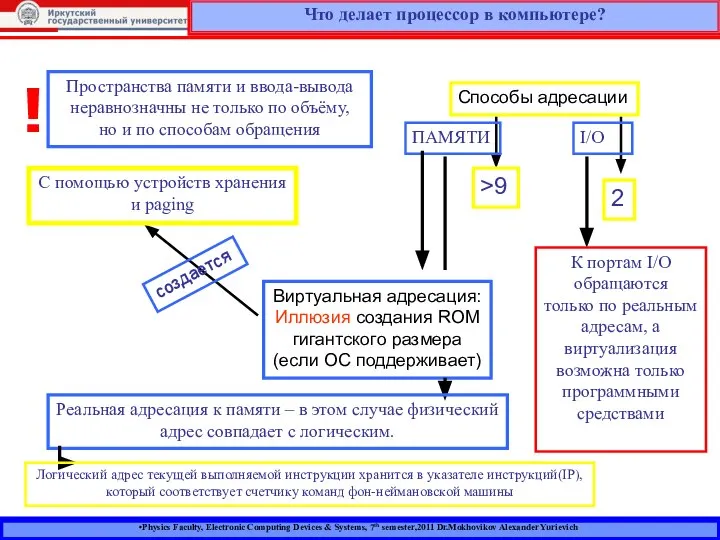

- 6. Пространства памяти и ввода-вывода неравнозначны не только по объёму, но и по способам обращения ! Способы

- 7. Архитектура и микроархитектура процессора Архитектура процессора – это его программная модель, то есть программно-видимые свойства. Микроархитектура

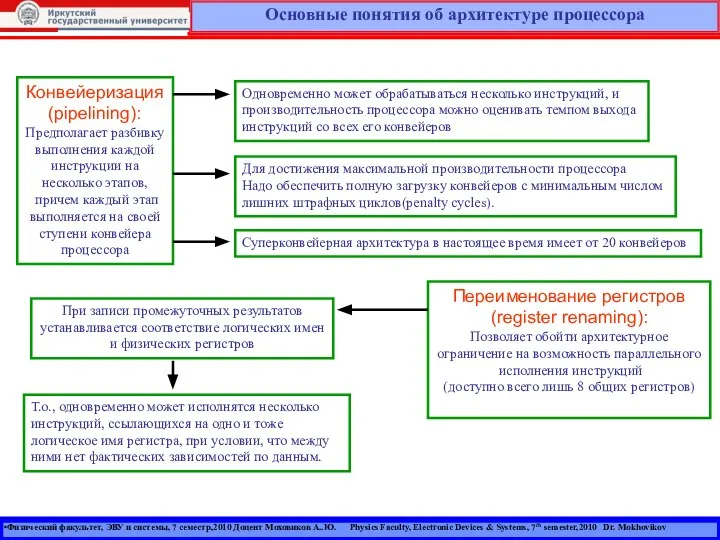

- 8. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

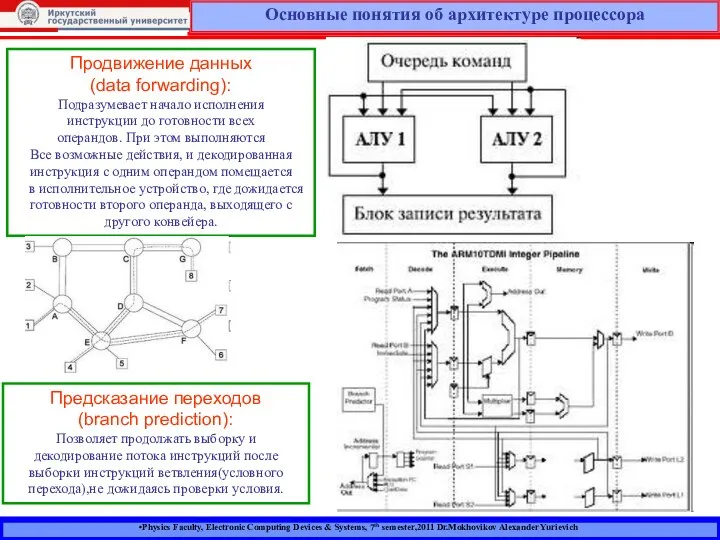

- 9. Продвижение данных (data forwarding): Подразумевает начало исполнения инструкции до готовности всех операндов. При этом выполняются Все

- 10. Physics Faculty, Electronic Computing Devices & Systems, 7th semester,2011 Dr.Mokhovikov Alexander Yurievich Основные понятия об архитектуре

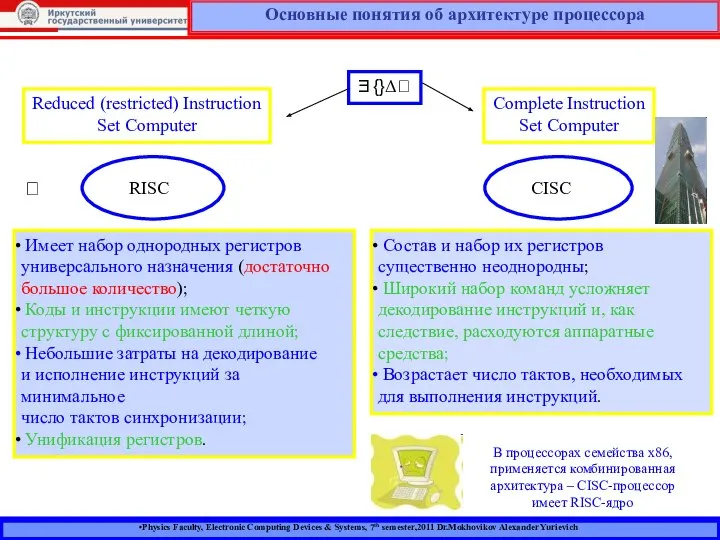

- 11. RISC CISC Reduced (restricted) Instruction Set Computer Complete Instruction Set Computer Имеет набор однородных регистров универсального

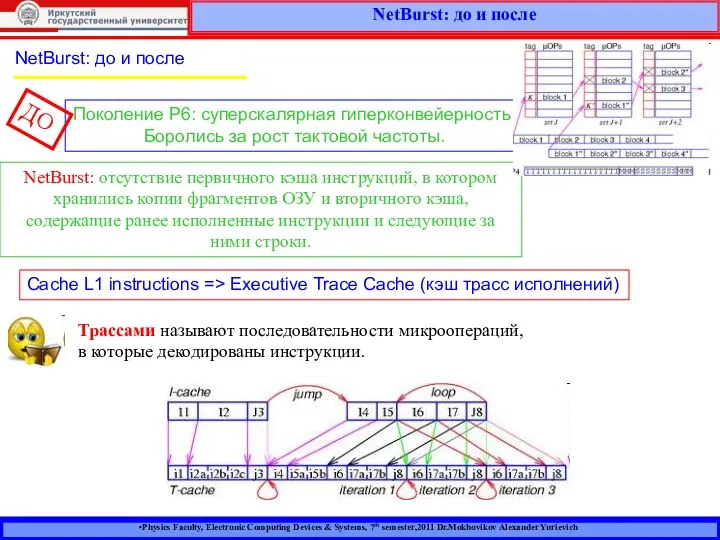

- 12. NetBurst: до и после Поколение Р6: суперскалярная гиперконвейерность. Боролись за рост тактовой частоты. NetBurst: отсутствие первичного

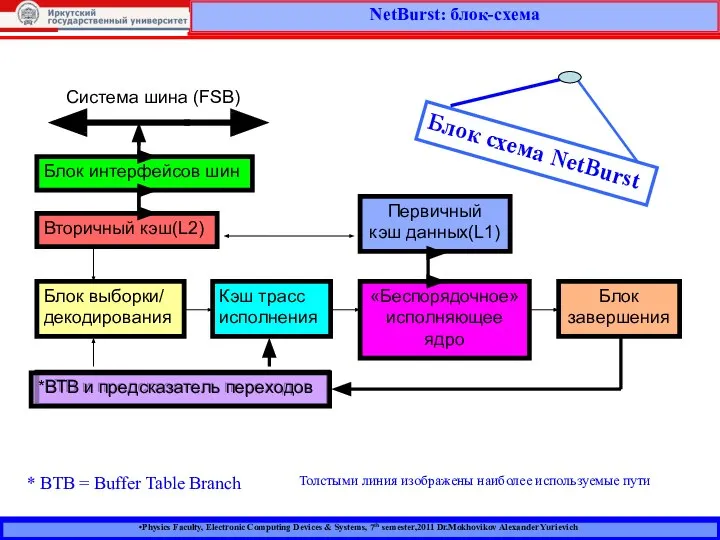

- 13. Система шина (FSB) Блок интерфейсов шин Вторичный кэш(L2) Блок выборки/ декодирования Кэш трасс исполнения ВТВ и

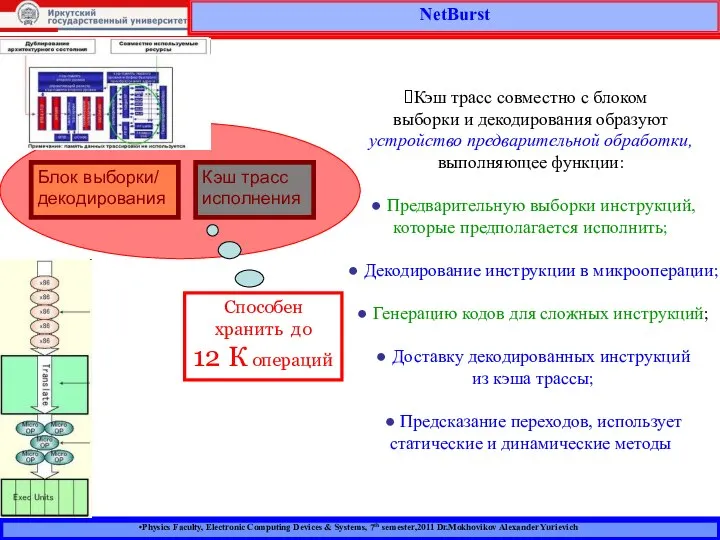

- 14. Блок выборки/ декодирования Кэш трасс исполнения Кэш трасс совместно с блоком выборки и декодирования образуют устройство

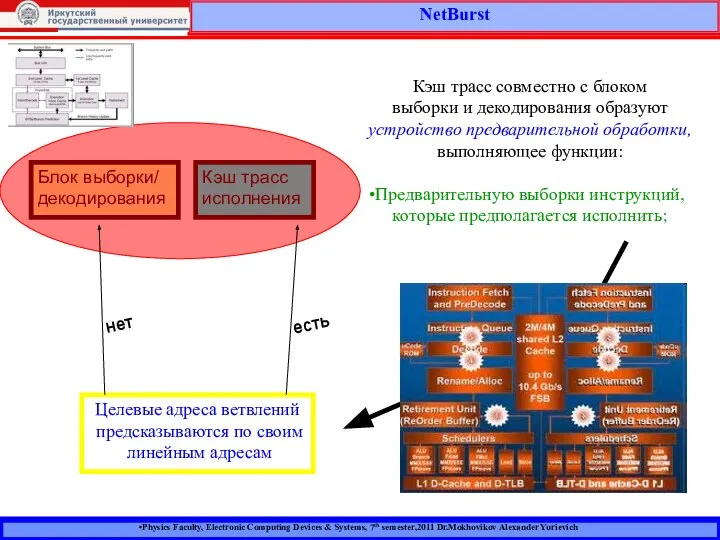

- 15. Блок выборки/ декодирования Кэш трасс исполнения Кэш трасс совместно с блоком выборки и декодирования образуют устройство

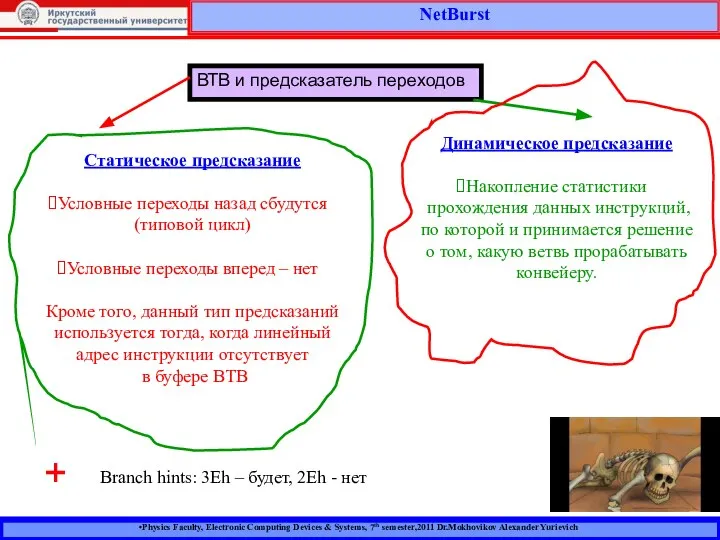

- 16. ВТВ и предсказатель переходов Статическое предсказание Условные переходы назад сбудутся (типовой цикл) Условные переходы вперед –

- 17. «Беспорядочное» исполняющее ядро Имеет пиковую пропускную способность, превышающую возможности блока предварительной обработки и блока завершения По

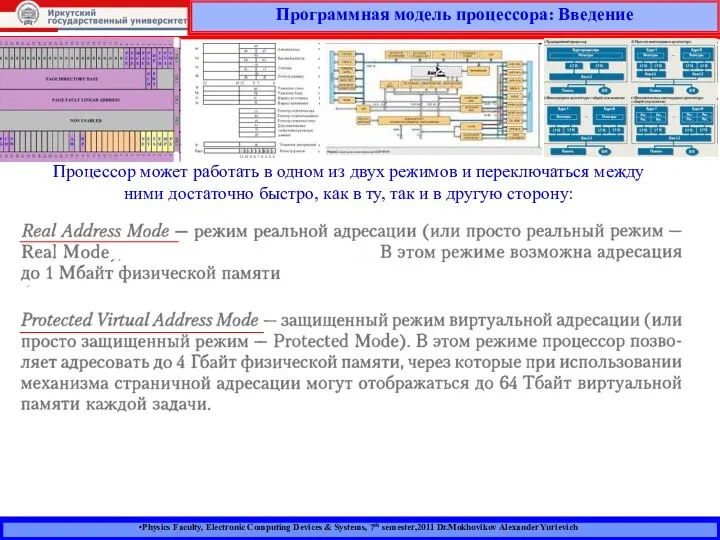

- 18. Процессор может работать в одном из двух режимов и переключаться между ними достаточно быстро, как в

- 19. Программная модель процессора: Введение Physics Faculty, Electronic Computing Devices & Systems, 7th semester,2011 Dr.Mokhovikov Alexander Yurievich

- 20. Программная модель процессора: Введение Physics Faculty, Electronic Computing Devices & Systems, 7th semester,2011 Dr.Mokhovikov Alexander Yurievich

- 21. Физический факультет, ЭВУ и системы, 7 семестр,2011 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 23. Скачать презентацию

Презентация на тему "Часть 3 (С2.2). Сочинение-рассуждение (собственное высказывание на основе прочитанного текста)" - скачать пр

Презентация на тему "Часть 3 (С2.2). Сочинение-рассуждение (собственное высказывание на основе прочитанного текста)" - скачать пр Презентация "Производство и издержки в рыночной экономике" - скачать презентации по Экономике

Презентация "Производство и издержки в рыночной экономике" - скачать презентации по Экономике Презентация на тему "Сбор информации у пациента с сердечной патологией" - скачать презентации по Медицине

Презентация на тему "Сбор информации у пациента с сердечной патологией" - скачать презентации по Медицине Административно-правовое регулирование в административно-политической сфере

Административно-правовое регулирование в административно-политической сфере Презентация Методы государственного контроля прямые и косвенные

Презентация Методы государственного контроля прямые и косвенные Экономика семьи

Экономика семьи  СРЕДСТВА И МЕТОДЫ ХИМИЧЕСКОЙ РАЗВЕДКИ И КОНТРОЛЯ

СРЕДСТВА И МЕТОДЫ ХИМИЧЕСКОЙ РАЗВЕДКИ И КОНТРОЛЯ Тема урока: В музыкальном театре. Балет.

Тема урока: В музыкальном театре. Балет. Основные фонды предприятия Цыганова Е., ЭБ2-3

Основные фонды предприятия Цыганова Е., ЭБ2-3 История мировой политической мысли

История мировой политической мысли тундра - презентация для начальной школы

тундра - презентация для начальной школы Крит Часть 2

Крит Часть 2 Конкурс «Воспитать человека 2009» Номинация «Социальный педагог» Федосеенкова Лариса Абакаровна МОУ « Савватиевская сош» Социальный педагог стаж в данной должности 5 лет Конкурс « Педагогическая кладовая II часть классный час « Дружба – это…»

Конкурс «Воспитать человека 2009» Номинация «Социальный педагог» Федосеенкова Лариса Абакаровна МОУ « Савватиевская сош» Социальный педагог стаж в данной должности 5 лет Конкурс « Педагогическая кладовая II часть классный час « Дружба – это…» ИНСТИТУЦИОНАЛЬНАЯ ЭКОНОМИКА (ВЗАИМОДЕЙСТВИЕ ГОСУДАРСТВА И БИЗНЕСА)

ИНСТИТУЦИОНАЛЬНАЯ ЭКОНОМИКА (ВЗАИМОДЕЙСТВИЕ ГОСУДАРСТВА И БИЗНЕСА)  Массивы. Строки. Пользовательские типы.(Тема 3)

Массивы. Строки. Пользовательские типы.(Тема 3) ОБЩАЯ И ПРОФЕССИОНАЛЬНАЯ КУЛЬТУРА ПЕДАГОГА Выполнила: студентка 1курса гр. В 23 Смурыгина Дарья Мамаева Екатерина

ОБЩАЯ И ПРОФЕССИОНАЛЬНАЯ КУЛЬТУРА ПЕДАГОГА Выполнила: студентка 1курса гр. В 23 Смурыгина Дарья Мамаева Екатерина  Небесная синева Гжели Презентация учащихся 7 класса МОУ «СОШ с. Сокур» Кл. руководитель – Белоусова Г.Г.

Небесная синева Гжели Презентация учащихся 7 класса МОУ «СОШ с. Сокур» Кл. руководитель – Белоусова Г.Г. Структурированный язык запросов SQL

Структурированный язык запросов SQL Транзисторы и их применение

Транзисторы и их применение Древний и современный фольклор

Древний и современный фольклор Cost-benefit analysis Анализ «издержки-выгоды» Выполнила: Калиновская М.В. 4 курс политологии ГУ-ВШЭ

Cost-benefit analysis Анализ «издержки-выгоды» Выполнила: Калиновская М.В. 4 курс политологии ГУ-ВШЭ  ОБРАЗОВАТЕЛЬНАЯ СИСТЕМА «ШКОЛА 2100» - И ЕЕ ГОТОВНОСТЬ К ФГОС

ОБРАЗОВАТЕЛЬНАЯ СИСТЕМА «ШКОЛА 2100» - И ЕЕ ГОТОВНОСТЬ К ФГОС Механизмы центрального торможения

Механизмы центрального торможения Общие сведения о кранах

Общие сведения о кранах Политология

Политология Vorbereitung für die Kontrollarbeit. Essen

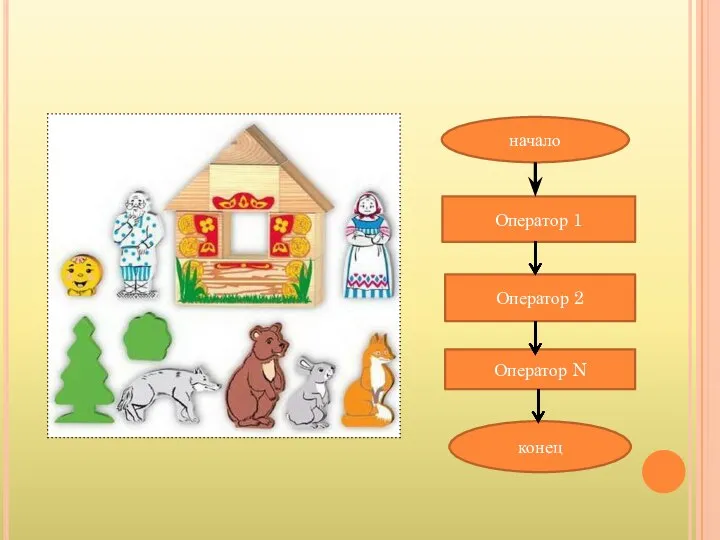

Vorbereitung für die Kontrollarbeit. Essen Докучные сказки

Докучные сказки Тайны русского алфавита

Тайны русского алфавита