Содержание

- 2. 2013 Литература по цифровой схемотехнике Джон Ф. Уэйкерли Проектирование цифровых устройств. В 2 т. М.: Постмаркет.

- 3. 2013 Литература по ПЛИС Максфилд К. Проектирование на ПЛИС. Курс молодого бойца. М.: Изд.дом "Додэка-ХХІ", 2007.

- 4. 2013 Проектування комп'ютерних систем на основі мікросхем програмованої логіки : монографія / С. А. Іванець, Ю.

- 5. 2013 Интернет-ресурсы Форум «Телесистемы» Форум по ПЛИС http://www.telesys.ru/wwwboards/fpga/index.shtml Языки описания аппаратуры (VHDL и др.) http://www.telesys.ru/wwwboards/vhdl/index.shtml Xilinx

- 6. 2013 ELECTRONIX.ru Форум разработчиков электроники ELECTRONIX.ru http://electronix.ru/forum/ Среды разработки - Development software Работаем с ПЛИС, области

- 7. 2013 Структура курса. 1 семестр Лекции: 32 часа Практические занятия: 16 часов Лабораторные работы: 32 часа

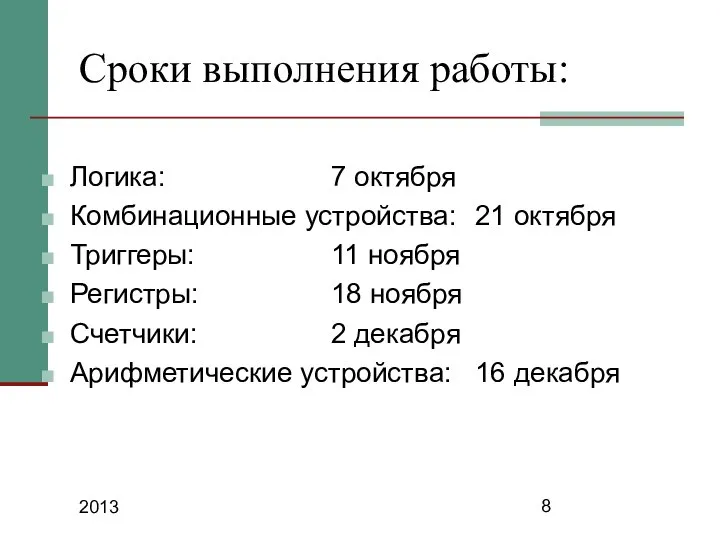

- 8. 2013 Сроки выполнения работы: Логика: 7 октября Комбинационные устройства: 21 октября Триггеры: 11 ноября Регистры: 18

- 9. 2013 Работа на лекции На лекцию нужно прийти с распечатанными слайдами. На каждой паре будет контрольная.

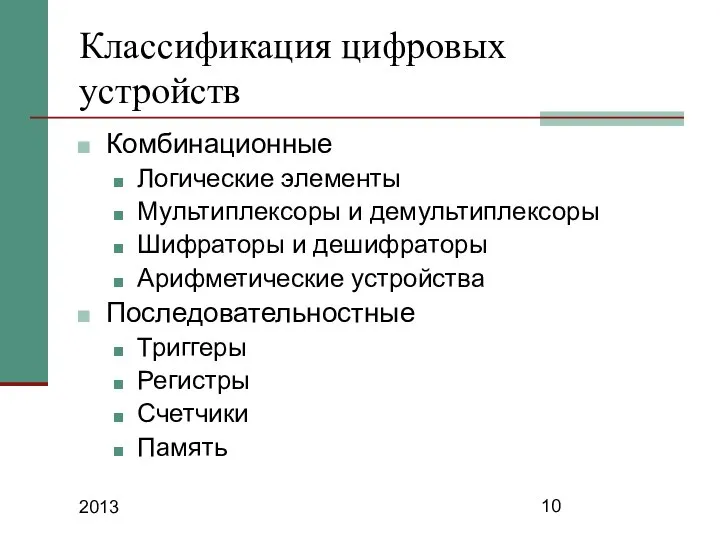

- 10. 2013 Классификация цифровых устройств Комбинационные Логические элементы Мультиплексоры и демультиплексоры Шифраторы и дешифраторы Арифметические устройства Последовательностные

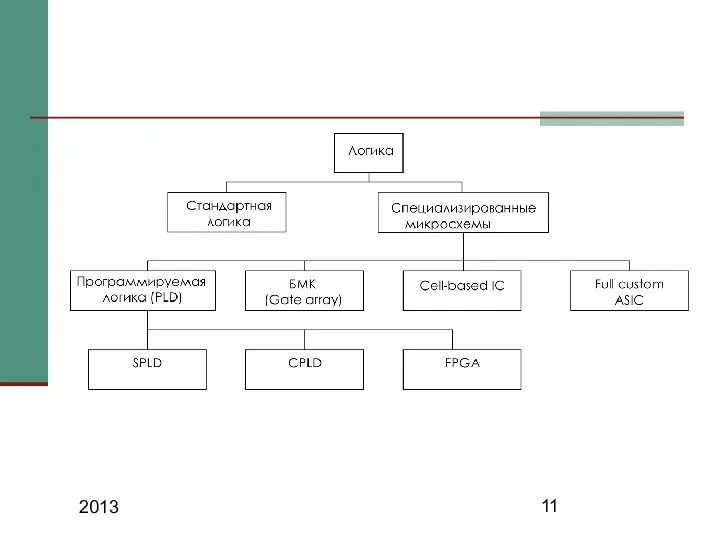

- 11. 2013

- 12. 2013 ASIC: Application Specific Integrated Circuit

- 13. 2013 SPLD - Simple Programmable Logic Devices CPLD - Complex Programmable Logic Devices FPGA - Field

- 14. 2013 По уровню интеграции малая интегральная схема (МИС) — до 100 элементов в кристалле, средняя интегральная

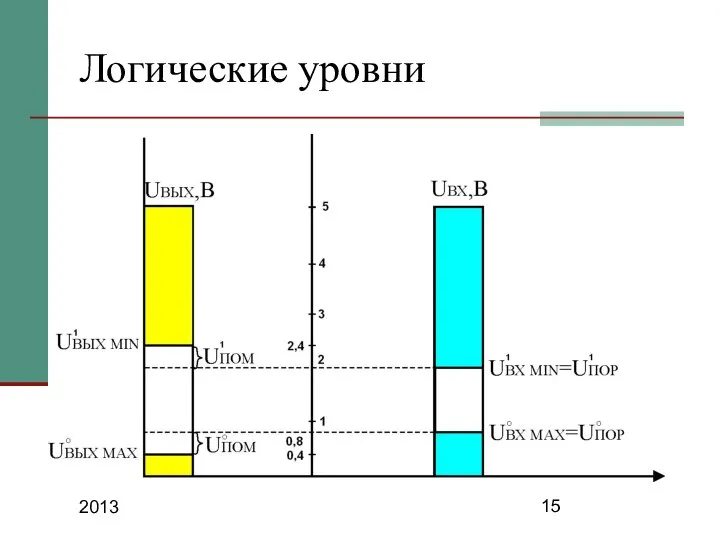

- 15. 2013 Логические уровни

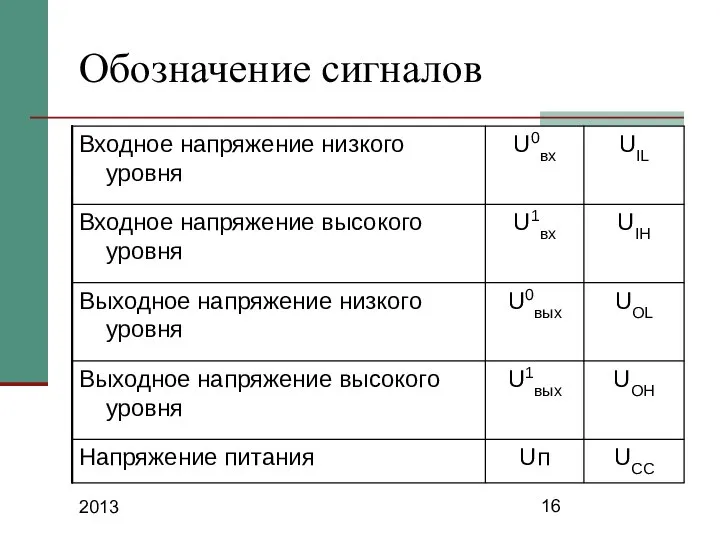

- 16. 2013 Обозначение сигналов

- 17. 2013 Обозначение линий питания VCC, VDD, V+, VS+ положительное питание СС – collector – коллектор DD

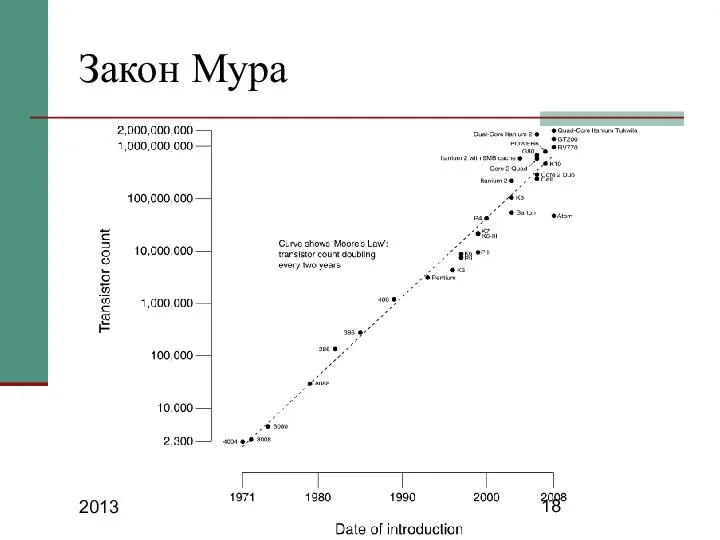

- 18. 2013 Закон Мура

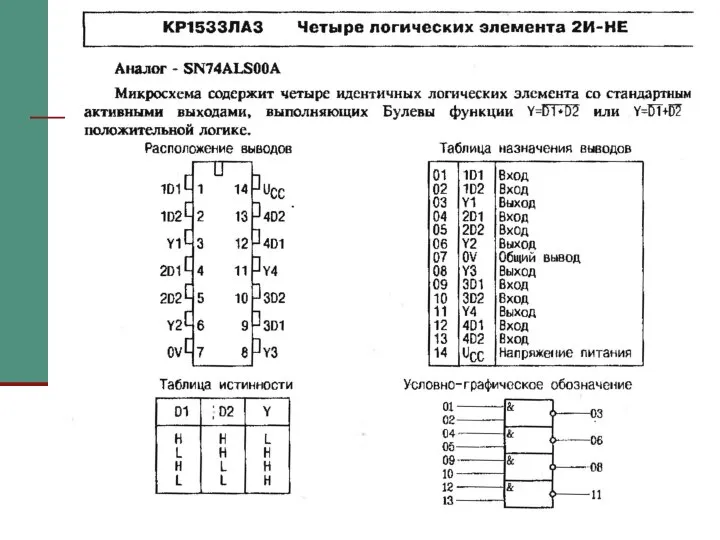

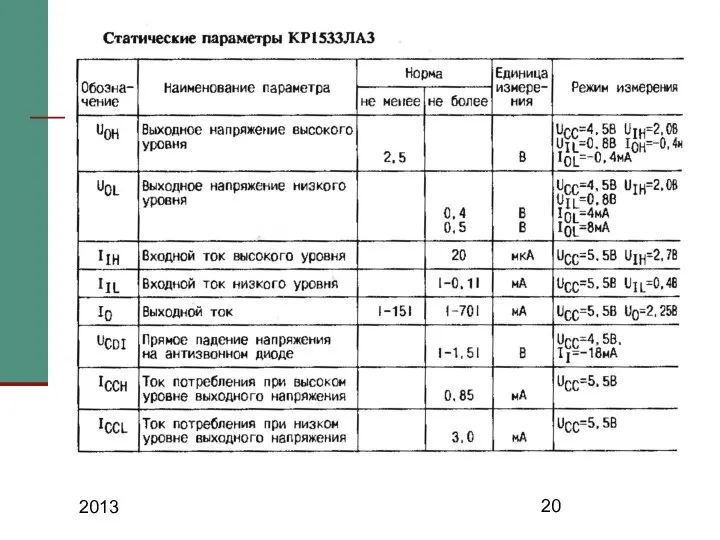

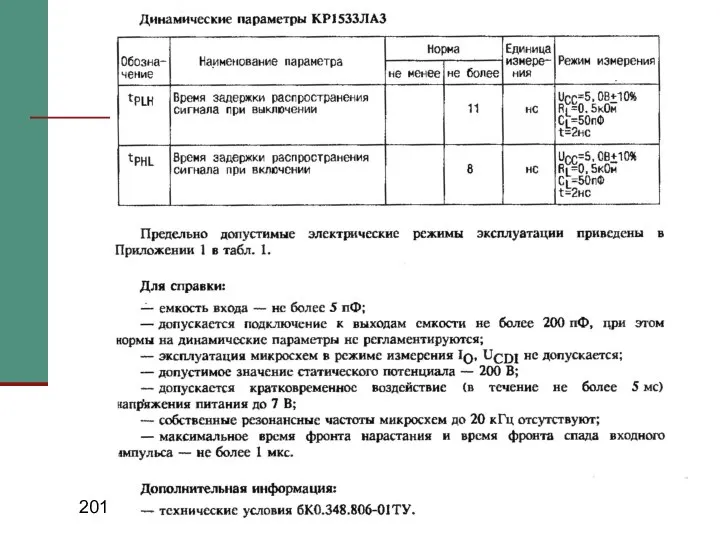

- 19. 2013

- 20. 2013

- 21. 2013

- 22. 2013

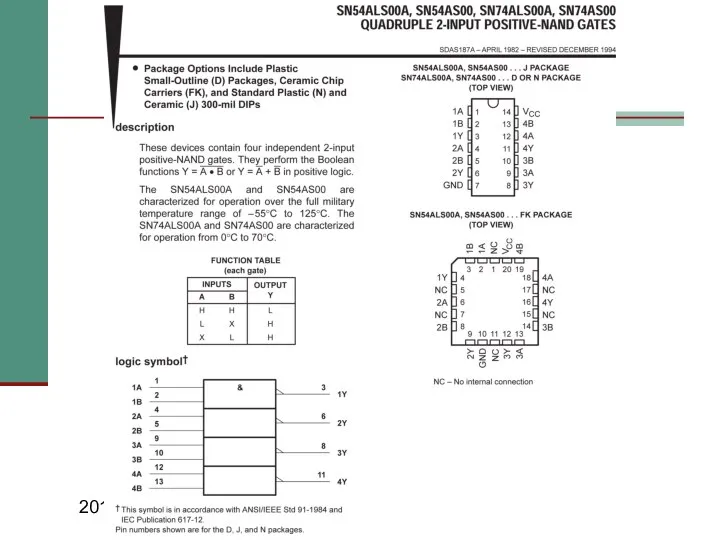

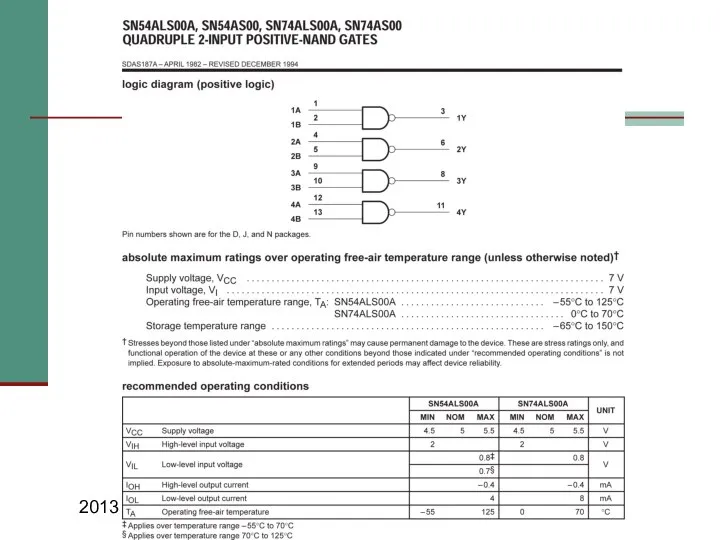

- 23. 2013

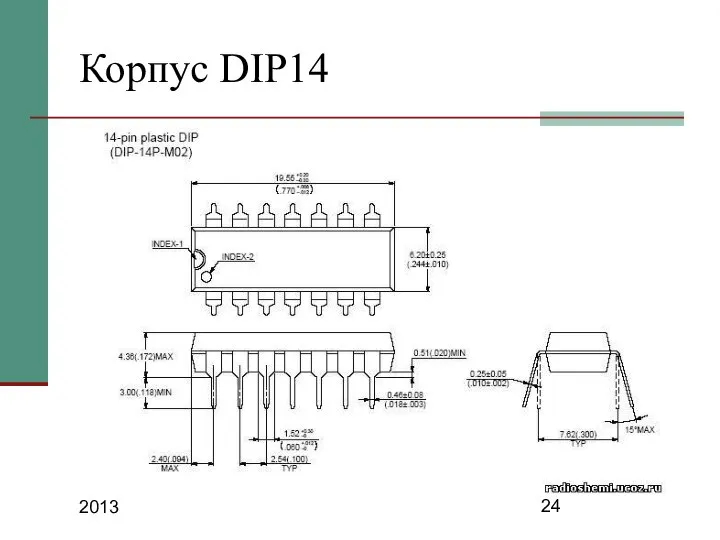

- 24. 2013 Корпус DIP14

- 25. 2013 Одновентильные микросхемы 74AHC1G09 – NXP 2И с открытым коллектором 5-выводный корпус 2х2 мм

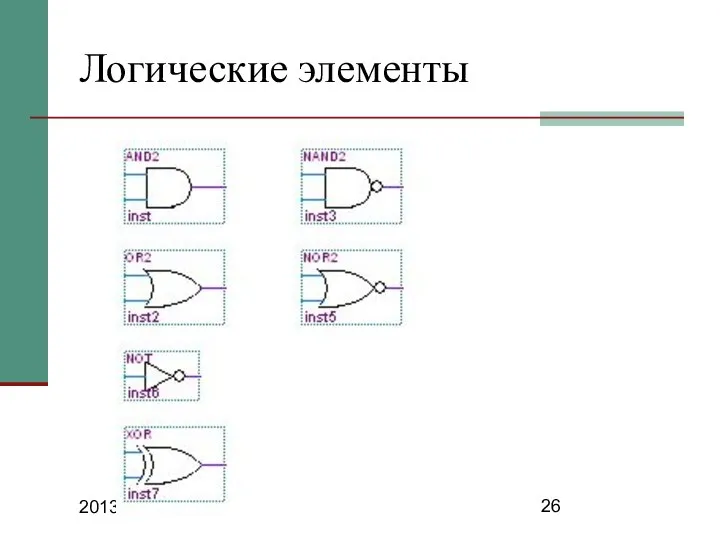

- 26. 2013 Логические элементы

- 27. 2013 Домашнее задание Система обозначений микросхем. Аванесян, стр. 28-29.

- 29. Скачать презентацию

Важные шаги к эффективному регулированию банков

Важные шаги к эффективному регулированию банков Динамика материальной точки

Динамика материальной точки  Красный крест

Красный крест  Жанель

Жанель Strategytraining.com & firmsconsulting: worlds largest consulting streaming training platform

Strategytraining.com & firmsconsulting: worlds largest consulting streaming training platform Trudovoe_pravo презентация 2014

Trudovoe_pravo презентация 2014 Презентация "Выдающиеся женщины - художницы" - скачать презентации по МХК

Презентация "Выдающиеся женщины - художницы" - скачать презентации по МХК Надежность и безопасность железобетонных конструкций

Надежность и безопасность железобетонных конструкций Алгоритмизация и программирование

Алгоритмизация и программирование Суть коммуникационных схем Геллера

Суть коммуникационных схем Геллера Основные вопросы профилактической работы врачей детских и подростковых учреждений

Основные вопросы профилактической работы врачей детских и подростковых учреждений Условия подобия процессов конвективного теплообмена

Условия подобия процессов конвективного теплообмена Презентация Цели, объекты и субъекты управления в таможенных органах

Презентация Цели, объекты и субъекты управления в таможенных органах  Современные методы устранения дисколоритов зубов

Современные методы устранения дисколоритов зубов Московский Кремль

Московский Кремль Бэкон обоснование эмпиризма

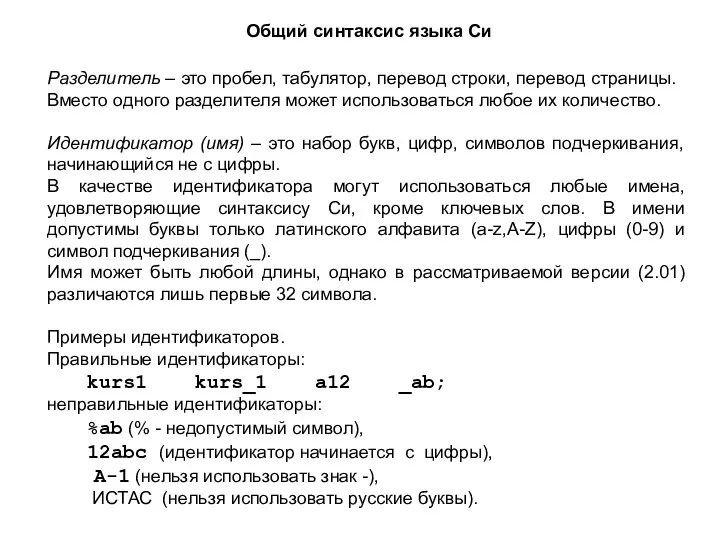

Бэкон обоснование эмпиризма  Общий синтаксис языка Си

Общий синтаксис языка Си «СПЕЦИАЛИЗИРОВАННЫЕ ТАМОЖНИ» ВЫПОЛНИЛА СТУДЕНТКА ЮРИДЮИЧЕСКОГО ФАКУЛЬТЕТА ГРУППЫ№1404 Микаилова Ламан

«СПЕЦИАЛИЗИРОВАННЫЕ ТАМОЖНИ» ВЫПОЛНИЛА СТУДЕНТКА ЮРИДЮИЧЕСКОГО ФАКУЛЬТЕТА ГРУППЫ№1404 Микаилова Ламан  «Электротехнические» элементы цепей

«Электротехнические» элементы цепей Барокко в Голландии

Барокко в Голландии Осетия. Обычаи осетинского народа

Осетия. Обычаи осетинского народа Памятка исследователя

Памятка исследователя Численность населения мира

Численность населения мира Библиотека VCL в Delphi

Библиотека VCL в Delphi Нейрофизиология программы

Нейрофизиология программы  Урок математики 4 класс «Закрепление вычислительных приемов умножения и деления»

Урок математики 4 класс «Закрепление вычислительных приемов умножения и деления» презентация ВПЦ Русский Виятзь

презентация ВПЦ Русский Виятзь Бортовые компьютеры. Конструкции бортовых компьютеров на базе стандарта РС/104

Бортовые компьютеры. Конструкции бортовых компьютеров на базе стандарта РС/104