Слайд 5

![Типы АЦП АЦП прямого преобразования или параллельный АЦП[1] содержит по одному](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1473917/slide-4.jpg)

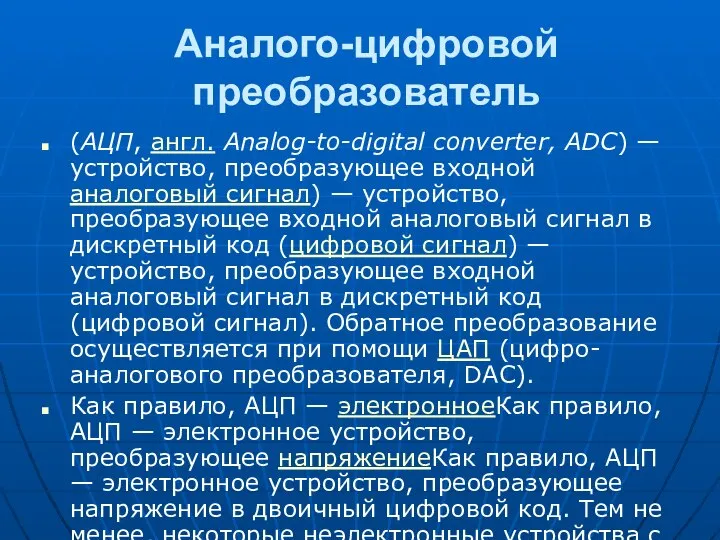

Типы АЦП

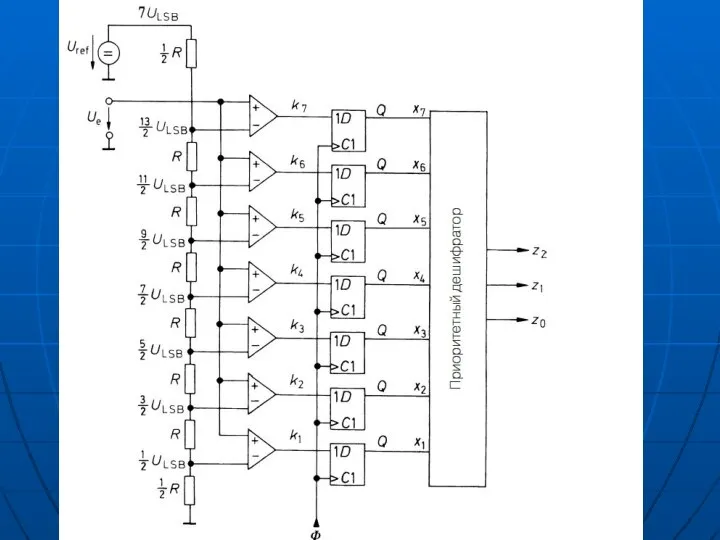

АЦП прямого преобразования или параллельный АЦП[1] содержит по одному компаратору[1]

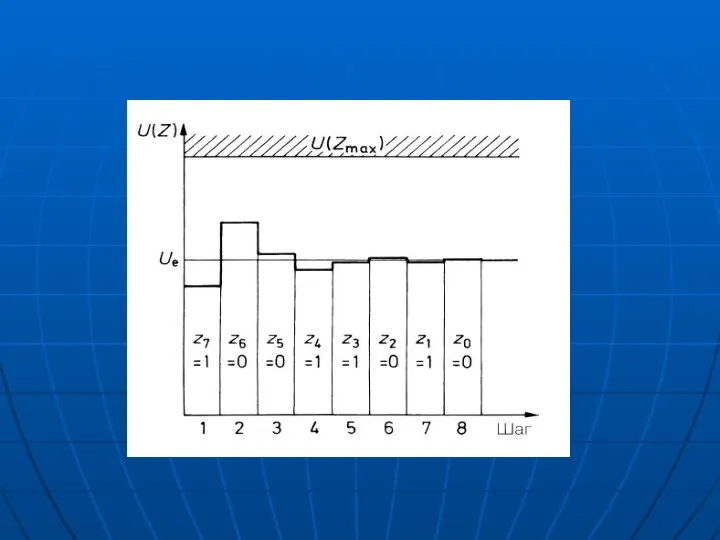

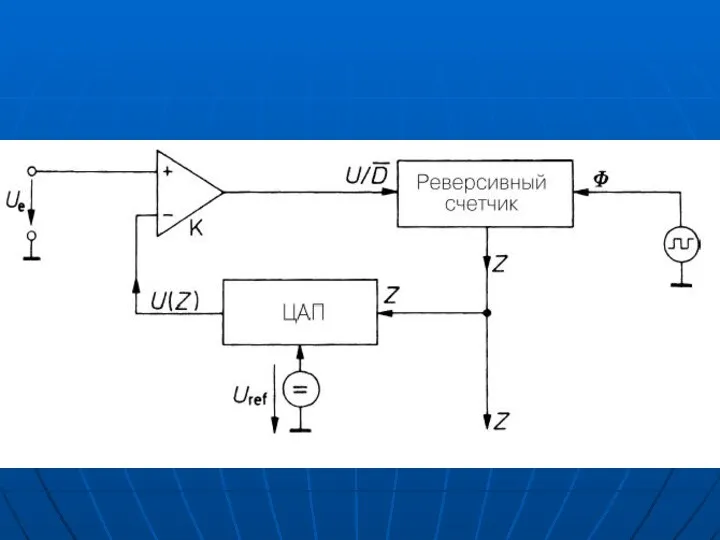

содержит по одному компаратору на каждый дискретный уровень входного сигнала. В любой момент времени только компараторы, соответствующие уровням ниже уровня входного сигнала, выдадут на своём выходе сигнал превышения. Сигналы со всех компараторов поступают на логическую схему[1] содержит по одному компаратору на каждый дискретный уровень входного сигнала. В любой момент времени только компараторы, соответствующие уровням ниже уровня входного сигнала, выдадут на своём выходе сигнал превышения. Сигналы со всех компараторов поступают на логическую схему, которая выдаёт цифровой код, зависящий от того, сколько и какие компараторы показали превышение. Параллельные АЦП очень быстры, но обычно имеют разрешение не более 8 бит (256 компараторов), так как имеют большую и дорогую схему. АЦП этого типа имеют очень большой размер кристалла микросхемы[1] содержит по одному компаратору на каждый дискретный уровень входного сигнала. В любой момент времени только компараторы, соответствующие уровням ниже уровня входного сигнала, выдадут на своём выходе сигнал превышения. Сигналы со всех компараторов поступают на логическую схему, которая выдаёт цифровой код, зависящий от того, сколько и какие компараторы показали превышение. Параллельные АЦП очень быстры, но обычно имеют разрешение не более 8 бит (256 компараторов), так как имеют большую и дорогую схему. АЦП этого типа имеют очень большой размер кристалла микросхемы, высокую входную ёмкость[1] содержит по одному компаратору на каждый дискретный уровень входного сигнала. В любой момент времени только компараторы, соответствующие уровням ниже уровня входного сигнала, выдадут на своём выходе сигнал превышения. Сигналы со всех компараторов поступают на логическую схему, которая выдаёт цифровой код, зависящий от того, сколько и какие компараторы показали превышение. Параллельные АЦП очень быстры, но обычно имеют разрешение не более 8 бит (256 компараторов), так как имеют большую и дорогую схему. АЦП этого типа имеют очень большой размер кристалла микросхемы, высокую входную ёмкость, и могут выдавать кратковременные ошибки на выходе. Часто используются для видео или других высокочастотных сигналов.

![Типы АЦП АЦП прямого преобразования или параллельный АЦП[1] содержит по одному](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1473917/slide-4.jpg)

London. Parts of London

London. Parts of London Загальні фізіологічні закономірності розвитку організму людини

Загальні фізіологічні закономірності розвитку організму людини Презентация на тему "Совет детских школьных организаций" - скачать презентации по Педагогике

Презентация на тему "Совет детских школьных организаций" - скачать презентации по Педагогике Модемы и факсмодемы

Модемы и факсмодемы Christmas in Great Britain

Christmas in Great Britain Как извлечь корень?

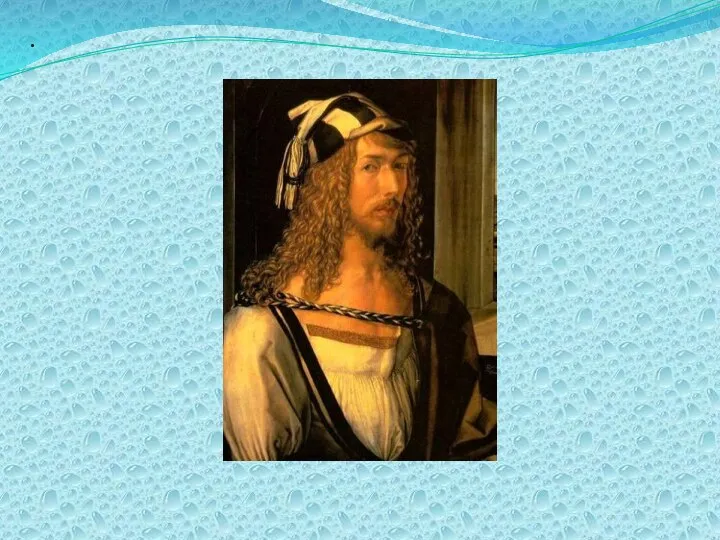

Как извлечь корень?  искусство

искусство АНТИБИОТИКОТЕРАПИЯ В ДЕТСКОЙ ХИРУРГИИ М.П. Разин

АНТИБИОТИКОТЕРАПИЯ В ДЕТСКОЙ ХИРУРГИИ М.П. Разин  Физиология труда

Физиология труда Системы связи. Единая сеть электросвязи РФ

Системы связи. Единая сеть электросвязи РФ Паралимпийское движение

Паралимпийское движение Systemy rozgrywek. Wybór systemu rozgrywek

Systemy rozgrywek. Wybór systemu rozgrywek ОСТРОВСКИЙ КАК ОСНОВОПОЛОЖНИК РУССКОГО ТЕАТРА

ОСТРОВСКИЙ КАК ОСНОВОПОЛОЖНИК РУССКОГО ТЕАТРА Искусство декупажа

Искусство декупажа Патофизиология системы внешнего дыхания

Патофизиология системы внешнего дыхания Задания по механике

Задания по механике Формы и методы проведения занятий инструктором в учебной группе

Формы и методы проведения занятий инструктором в учебной группе Урок №39(120) Тест «Подготовка к усвоению табличных случаев умножения»

Урок №39(120) Тест «Подготовка к усвоению табличных случаев умножения»  Стандарты работы старшего оператора

Стандарты работы старшего оператора Основные стратегии регуляции метаболических путей

Основные стратегии регуляции метаболических путей Системы Автоматизации Управления Воздушным Движением

Системы Автоматизации Управления Воздушным Движением Парк Большой Истокк

Парк Большой Истокк Физическая реабилитация в травматологии, ортопедии и хирургии

Физическая реабилитация в травматологии, ортопедии и хирургии  Тестовая комбинаторика Создание тестового набора. Минимальные проверки. Перебор значений. Метод взаимосвязанных проверок

Тестовая комбинаторика Создание тестового набора. Минимальные проверки. Перебор значений. Метод взаимосвязанных проверок Презентация "Основные русские архитектурные стили" - скачать презентации по МХК

Презентация "Основные русские архитектурные стили" - скачать презентации по МХК Уровни и формы правосознания

Уровни и формы правосознания  Die Butterwoche in Russland. Russische Volksfeste

Die Butterwoche in Russland. Russische Volksfeste Расчет параметров кремниевого интегрального N-канального МДП-транзистора

Расчет параметров кремниевого интегрального N-канального МДП-транзистора