Содержание

- 2. Эволюция технологий изготовления процессора Электромеханическое реле Вакуумные лампы и ячейки на лампах Транзисторы

- 3. Эволюция технологий изготовления процессора: микросхемы Микропроцессор Intel 4004 1971 год первый в мире коммерчески доступный однокристальный

- 4. В настоящее время Intel Core i3 2010 2011 год 995 000 000 транзисторов ~145 000 000

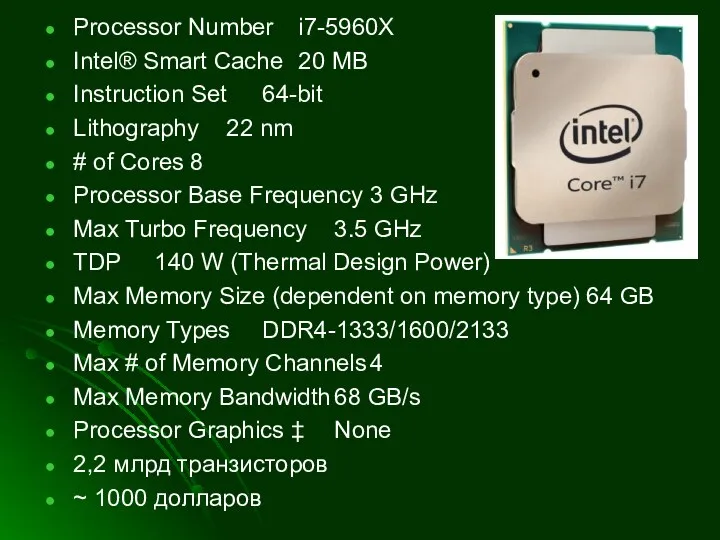

- 5. Processor Number i7-5960X Intel® Smart Cache 20 MB Instruction Set 64-bit Lithography 22 nm # of

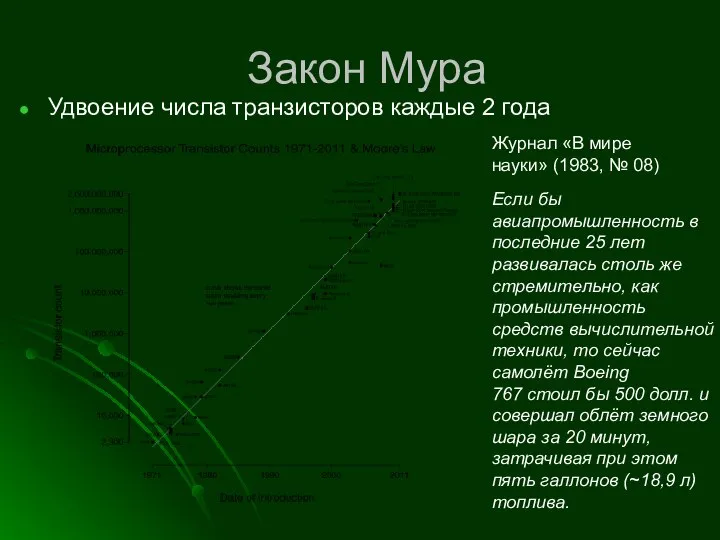

- 6. Закон Мура Удвоение числа транзисторов каждые 2 года Если бы авиапромышленность в последние 25 лет развивалась

- 7. Схема работы транзистора Напряжение на базе ниже критического – транзистор действует как большое сопротивление; выходное напряжение

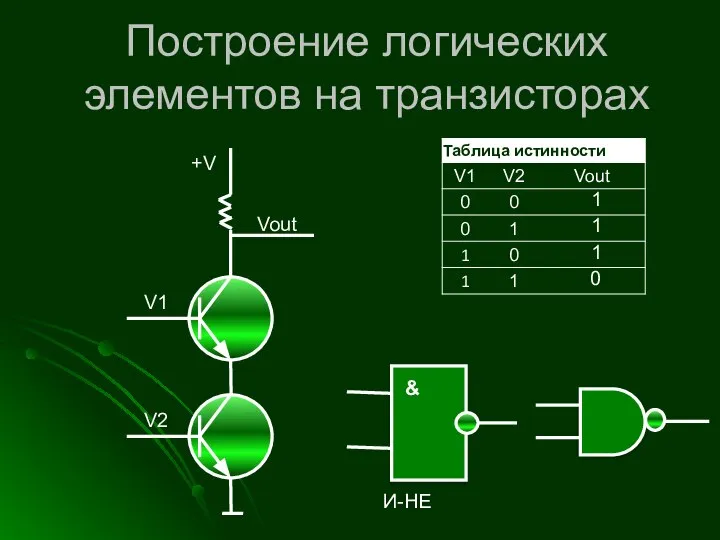

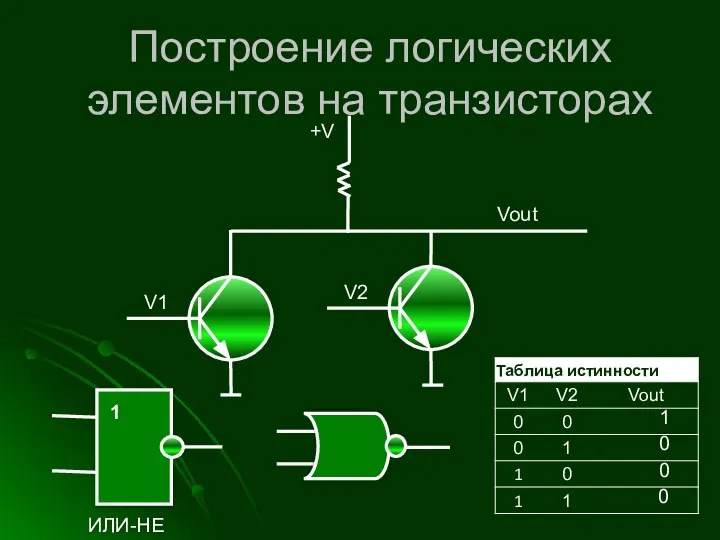

- 8. Построение логических элементов на транзисторах Vout +V V1 V2 0 1 1 1

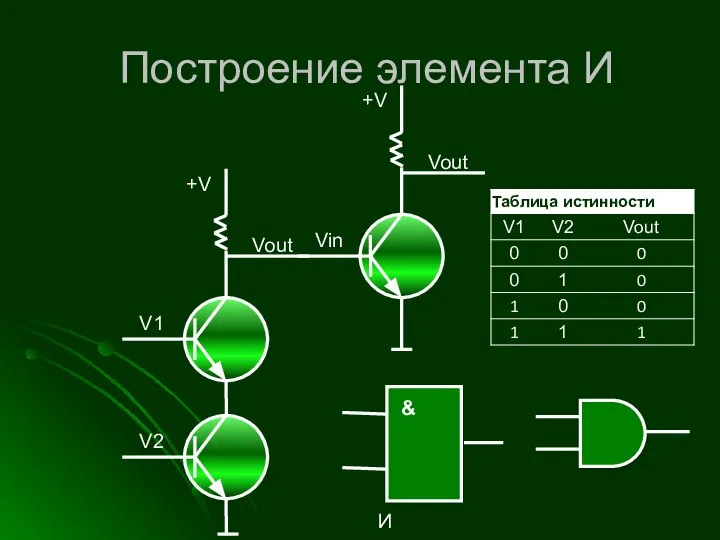

- 9. Построение элемента И Vout +V V1 V2 Vout +V Vin

- 10. Vout +V V1 V2 Построение логических элементов на транзисторах 0 1 0 0

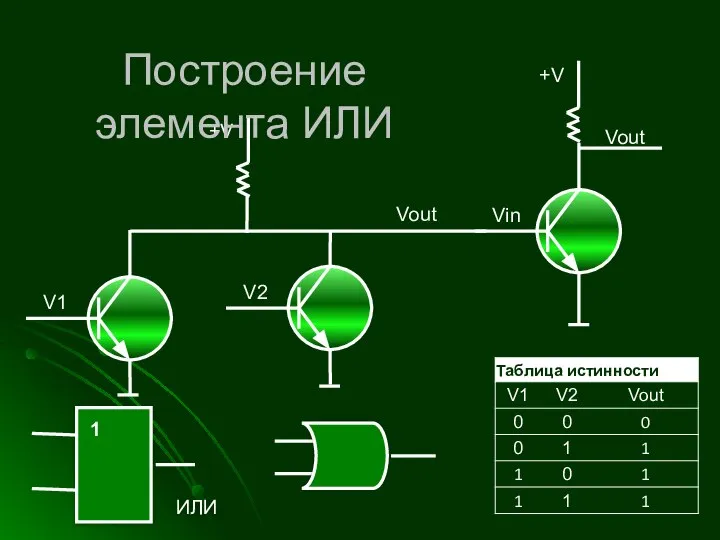

- 11. Vout +V V1 V2 Построение элемента ИЛИ Vout +V Vin

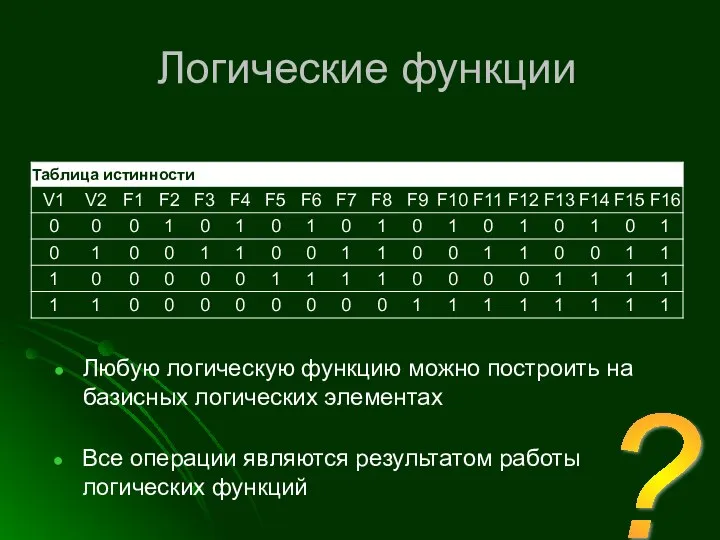

- 12. Логические функции Все операции являются результатом работы логических функций ? Любую логическую функцию можно построить на

- 13. Пример: Таблица истинности сумматора 0 0 1 1 Перенос 1 0 0 0 0 0 1

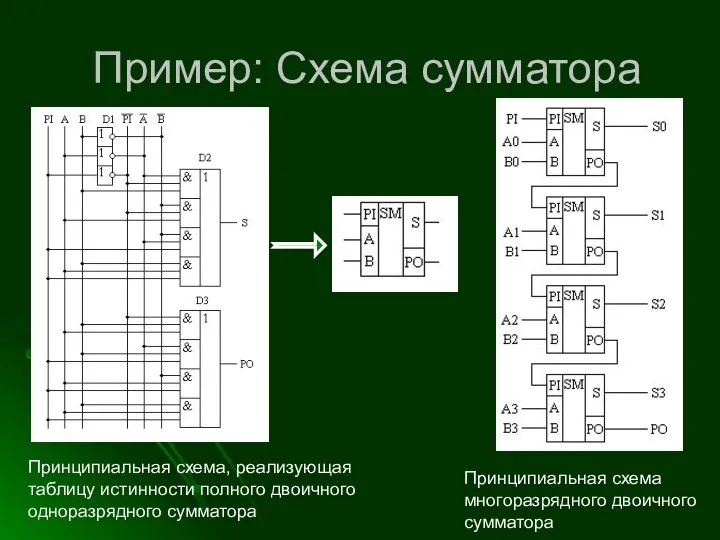

- 14. Пример: Схема сумматора Принципиальная схема, реализующая таблицу истинности полного двоичного одноразрядного сумматора Принципиальная схема многоразрядного двоичного

- 15. Схема материнской платы ПК

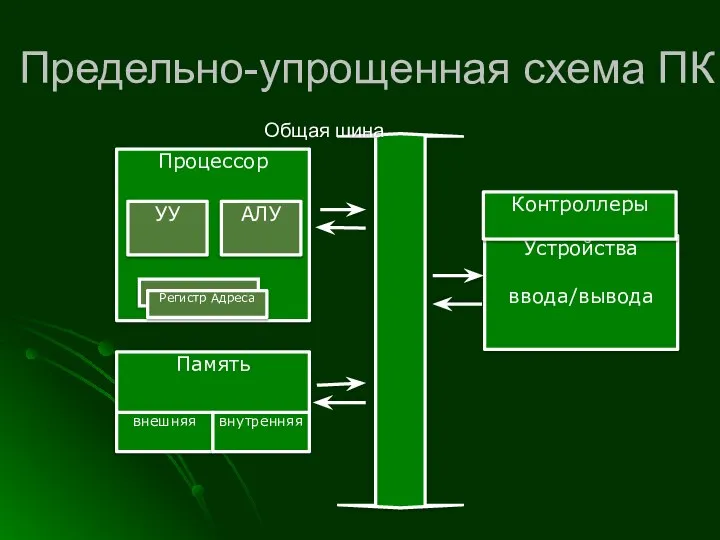

- 16. Предельно-упрощенная схема ПК Процессор Память Устройства ввода/вывода внешняя внутренняя Общая шина Контроллеры УУ АЛУ Регистр Адреса

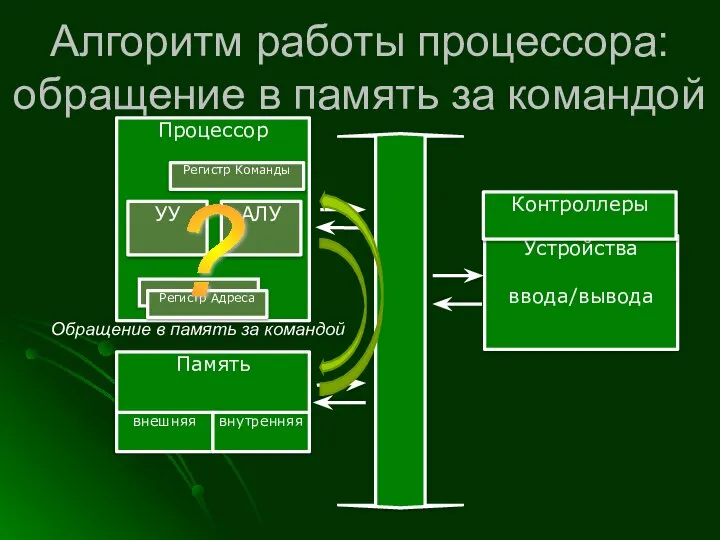

- 17. Алгоритм работы процессора: обращение в память за командой Процессор Память Устройства ввода/вывода внешняя внутренняя Контроллеры УУ

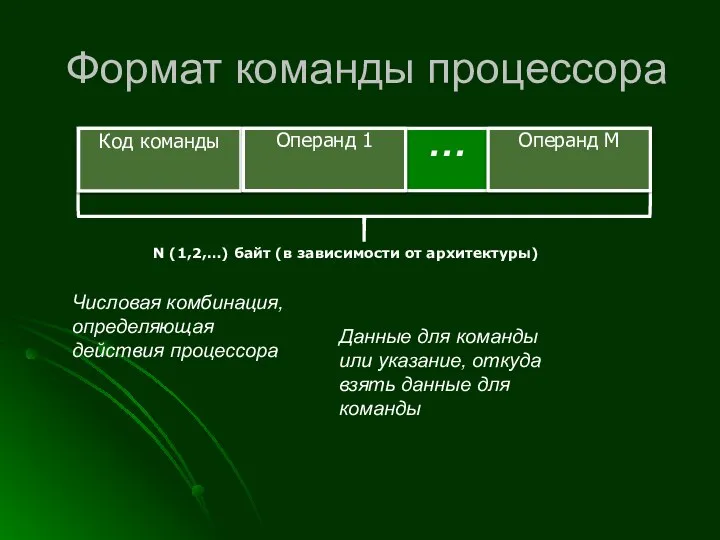

- 18. Формат команды процессора N (1,2,…) байт (в зависимости от архитектуры) Код команды Числовая комбинация, определяющая действия

- 19. Алгоритм работы процессора: обращение в память за данными Процессор Память Устройства ввода/вывода внешняя внутренняя Контроллеры УУ

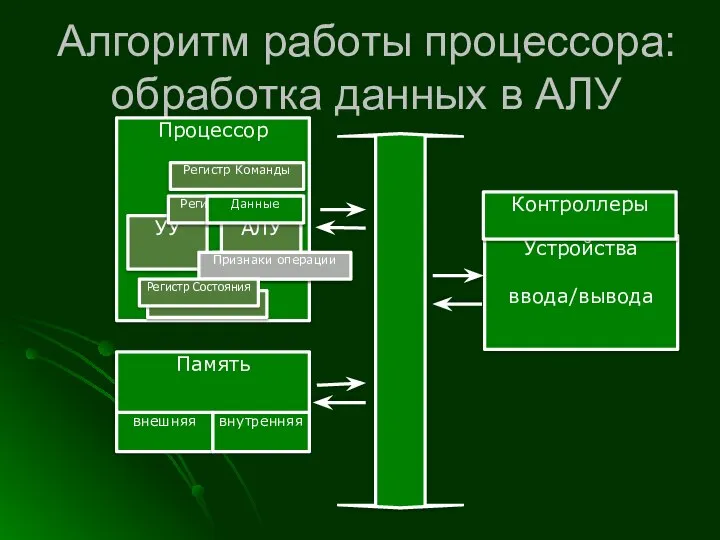

- 20. Алгоритм работы процессора: обработка данных в АЛУ Процессор Память Устройства ввода/вывода внешняя внутренняя Контроллеры УУ Регистр

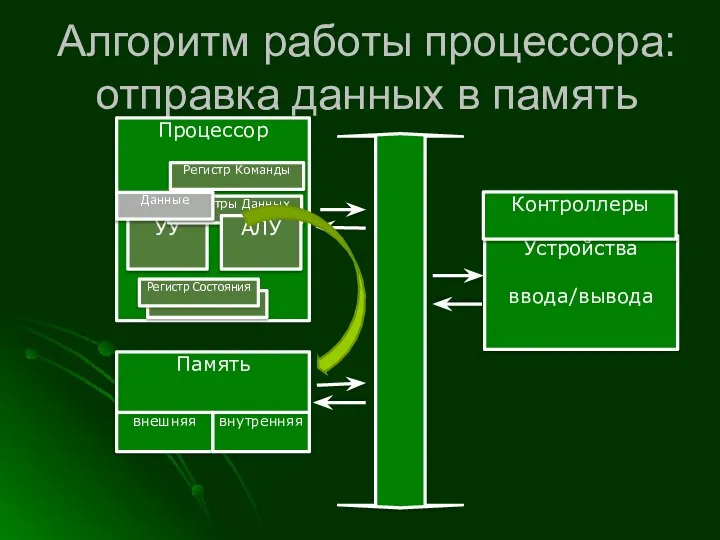

- 21. Алгоритм работы процессора: отправка данных в память Процессор Память Устройства ввода/вывода внешняя внутренняя Контроллеры УУ Регистр

- 22. Алгоритм работы процессора: определение адреса команды Процессор Память Устройства ввода/вывода внешняя внутренняя Контроллеры УУ Регистр Команды

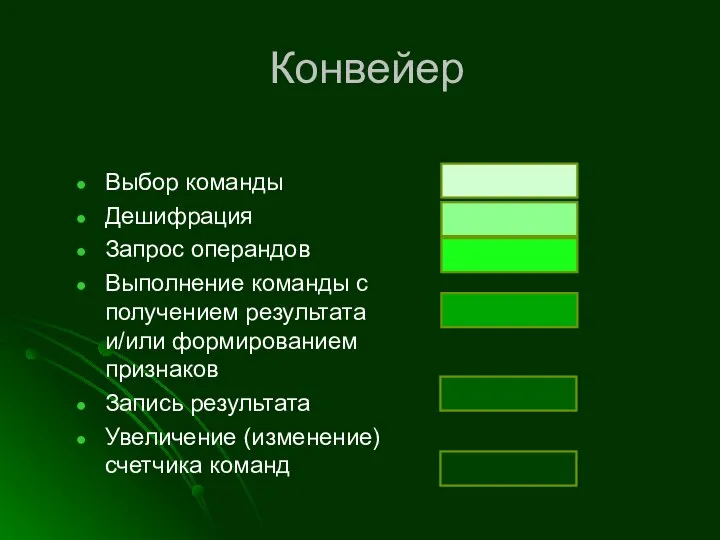

- 23. Алгоритм работы процессора Выбор команды Дешифрация Запрос операндов Выполнение команды с получением результата и/или формированием признаков

- 24. Упрощенная структурная схема процессора (следующий слайд)

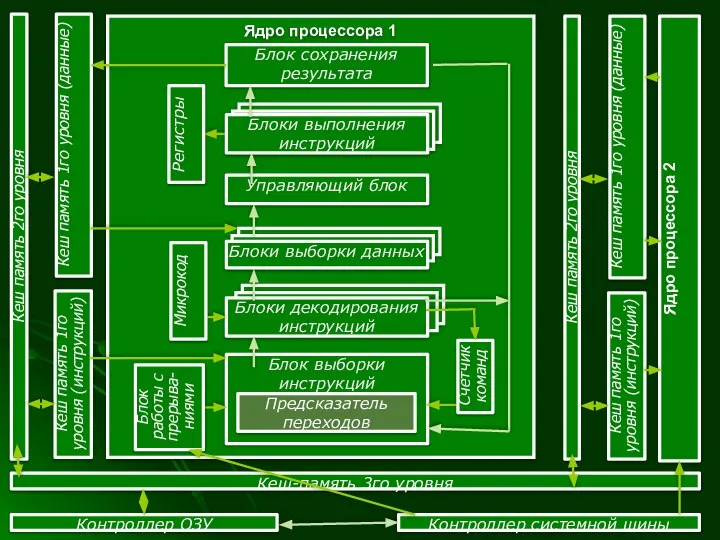

- 25. Блок выборки инструкций Ядро процессора 1 Предсказатель переходов Блоки декодирования инструкций Блоки выборки данных Управляющий блок

- 26. Способы увеличения производительности процессора Конвейеризация Суперскалярность Параллельная обработка данных Технология Hyper-Threading Технология Turbo Boost Эффективность выполнения

- 27. Конвейер Выбор команды Дешифрация Запрос операндов Выполнение команды с получением результата и/или формированием признаков Запись результата

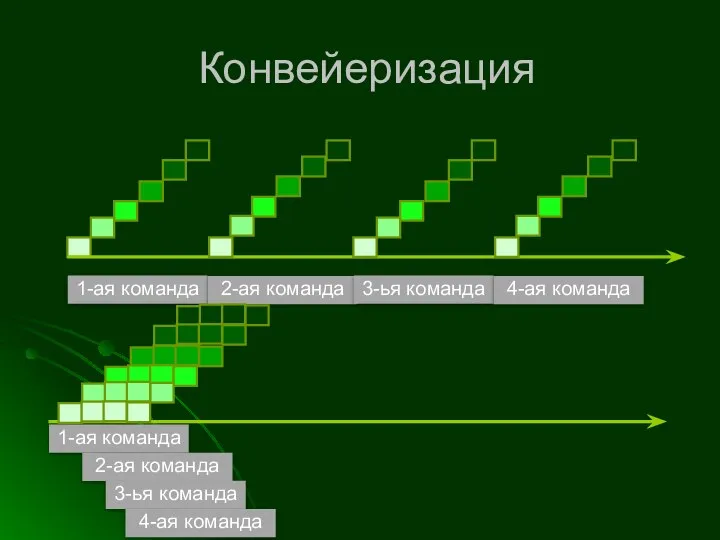

- 28. Конвейеризация 1-ая команда 2-ая команда 1-ая команда 3-ья команда 4-ая команда 2-ая команда 3-ья команда 4-ая

- 29. Суперскалярность Наиболее нагруженные блоки присутствуют в нескольких экземплярах Параллельное выполнение возможно при независимости инструкций

- 30. Параллельная обработка данных Не все программы могут работать на нескольких ядрах Одна программа –одно ядро: а

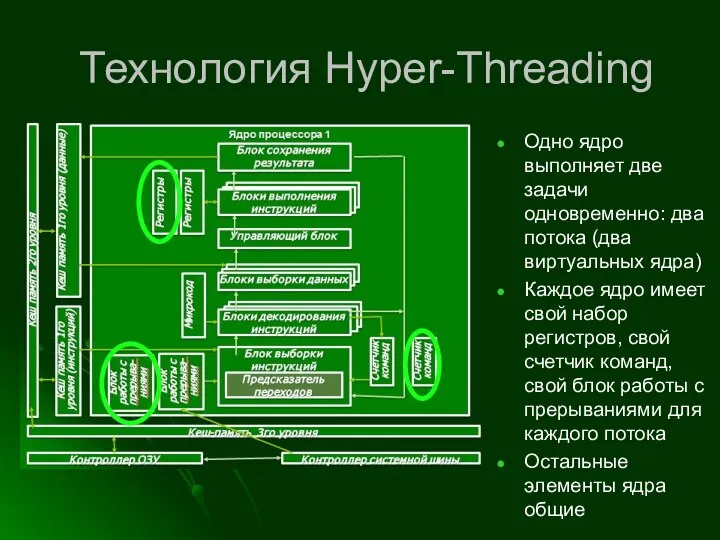

- 31. Технология Hyper-Threading Одно ядро выполняет две задачи одновременно: два потока (два виртуальных ядра) Каждое ядро имеет

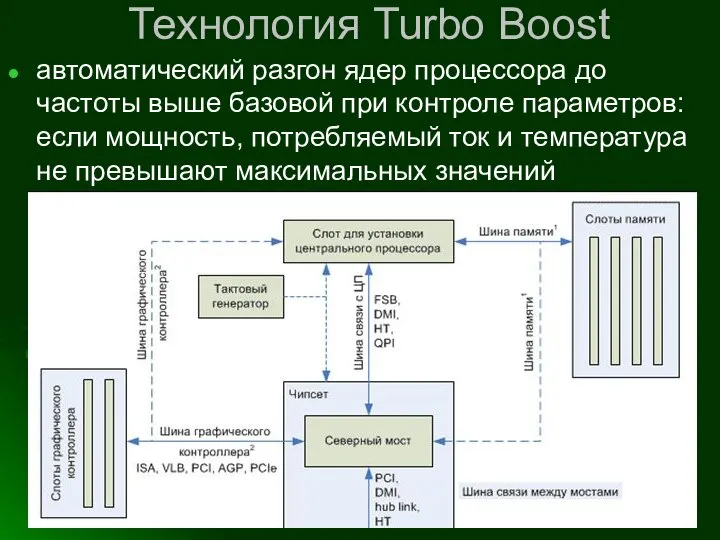

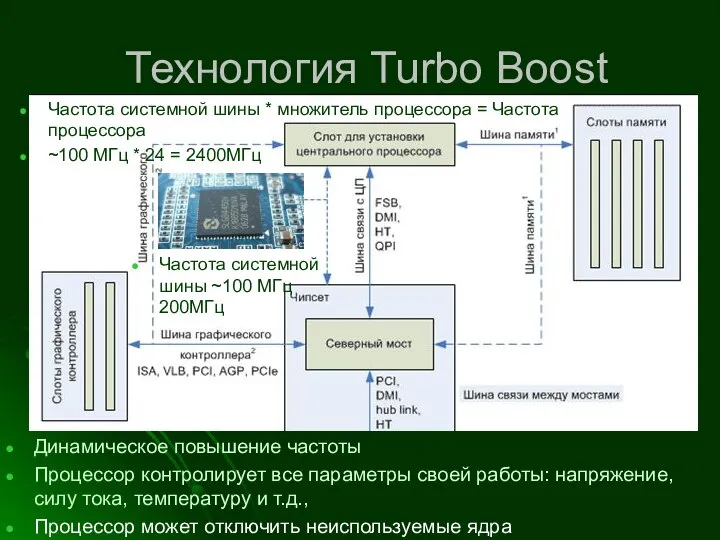

- 32. Технология Turbo Boost автоматический разгон ядер процессора до частоты выше базовой при контроле параметров: если мощность,

- 33. Технология Turbo Boost Динамическое повышение частоты Процессор контролирует все параметры своей работы: напряжение, силу тока, температуру

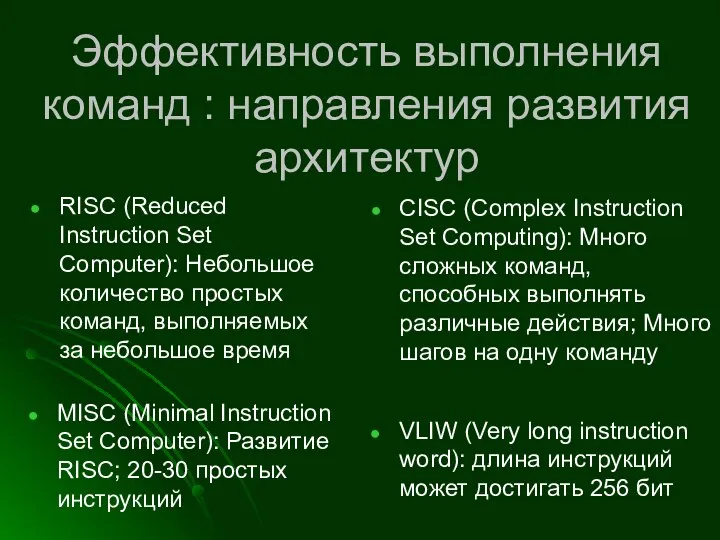

- 34. Эффективность выполнения команд : направления развития архитектур RISC (Reduced Instruction Set Computer): Небольшое количество простых команд,

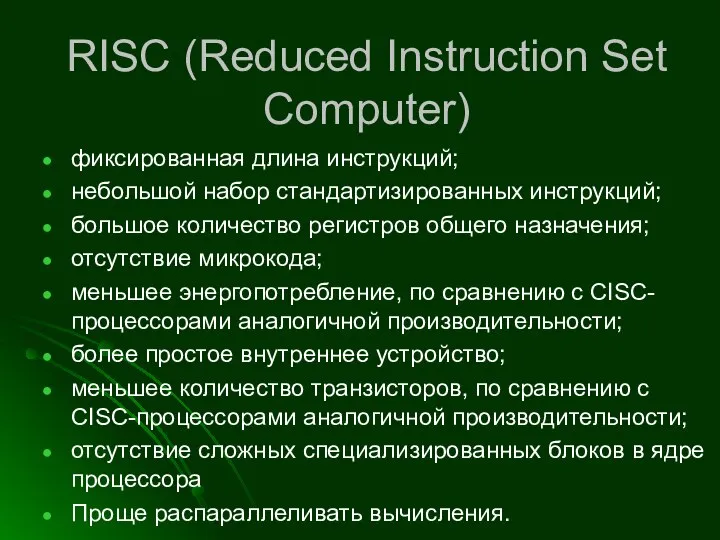

- 35. RISC (Reduced Instruction Set Computer) фиксированная длина инструкций; небольшой набор стандартизированных инструкций; большое количество регистров общего

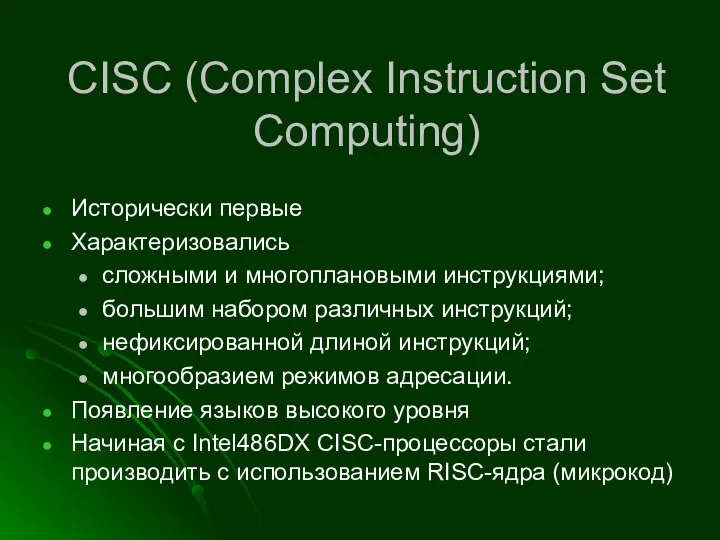

- 36. CISC (Complex Instruction Set Computing) Исторически первые Характеризовались сложными и многоплановыми инструкциями; большим набором различных инструкций;

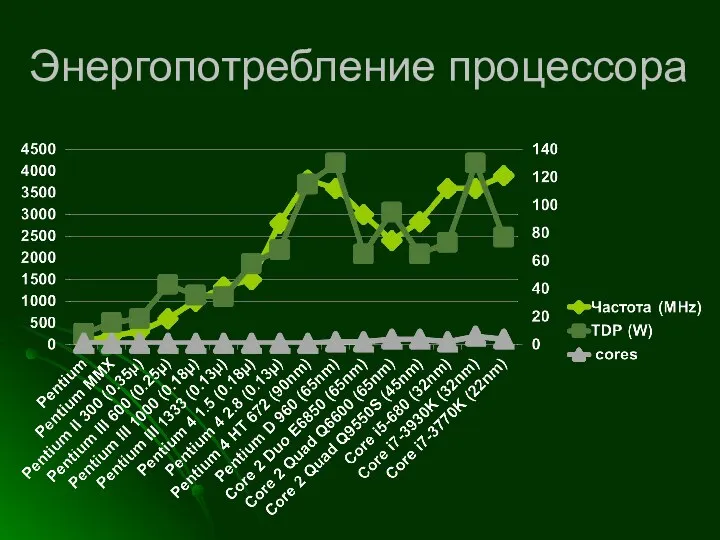

- 37. Энергопотребление процессора

- 38. Энергопотребление процессора

- 39. Способы снижения энергопотребления процессора Портативные устройства Снижение частоты – потеря производительности… Технология EIST (Enhanced Intel SpeedStep

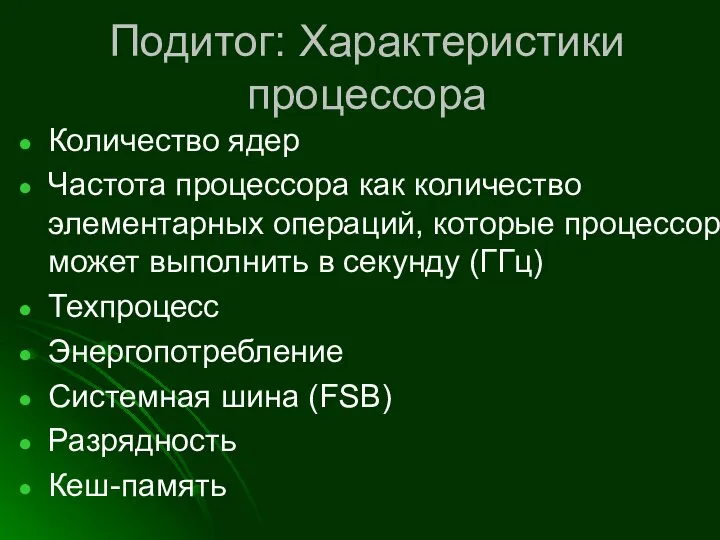

- 40. Подитог: Характеристики процессора Количество ядер Частота процессора как количество элементарных операций, которые процессор может выполнить в

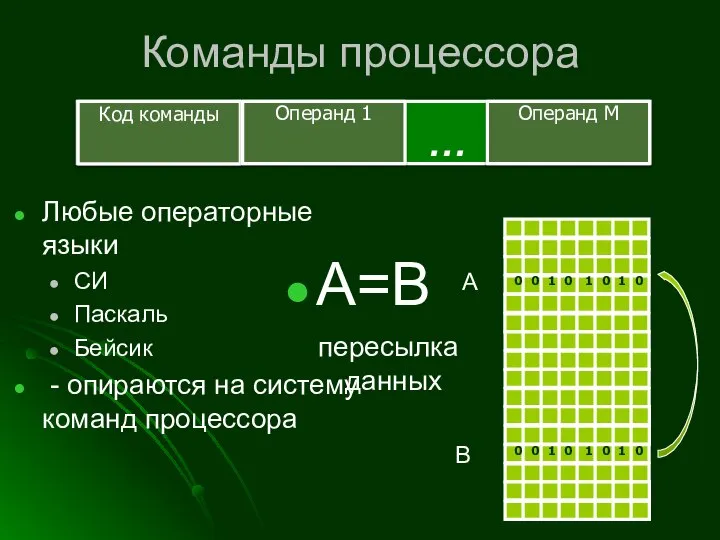

- 41. Любые операторные языки СИ Паскаль Бейсик - опираются на систему команд процессора A=B пересылка данных 0

- 42. Выполнение команды пересылки Процессор Память Устройства ввода/вывода внешняя внутренняя Контроллеры УУ АЛУ Регистр Адреса Регистр Команды

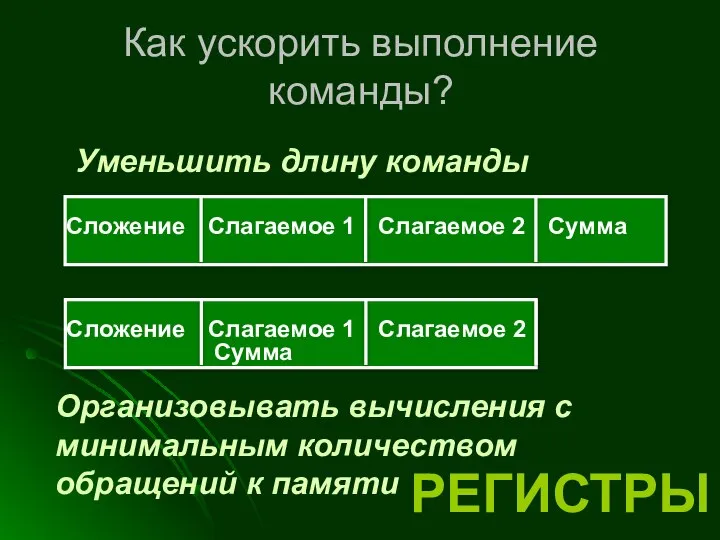

- 43. Как ускорить выполнение команды? Сложение Слагаемое 1 Слагаемое 2 Сумма Уменьшить длину команды Организовывать вычисления с

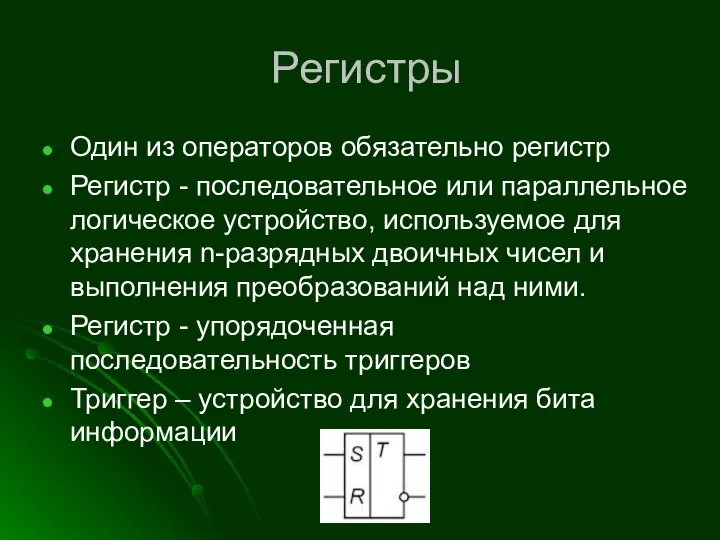

- 44. Регистры Один из операторов обязательно регистр Регистр - последовательное или параллельное логическое устройство, используемое для хранения

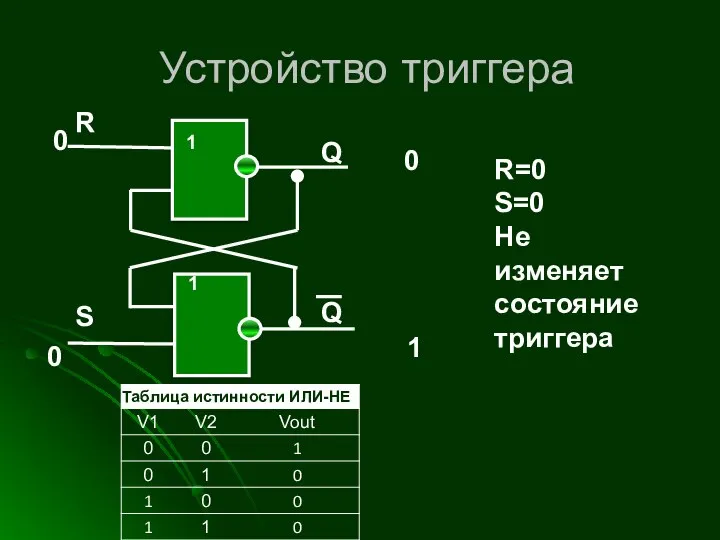

- 45. Устройство триггера 0 1 0 0 R=0 S=0 Не изменяет состояние триггера R S Q Q

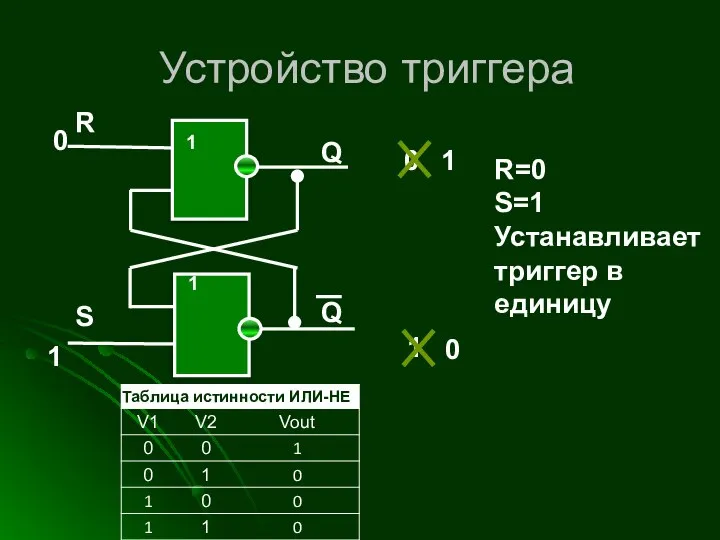

- 46. Устройство триггера 0 1 R=0 S=1 Устанавливает триггер в единицу 0 1 R S Q Q

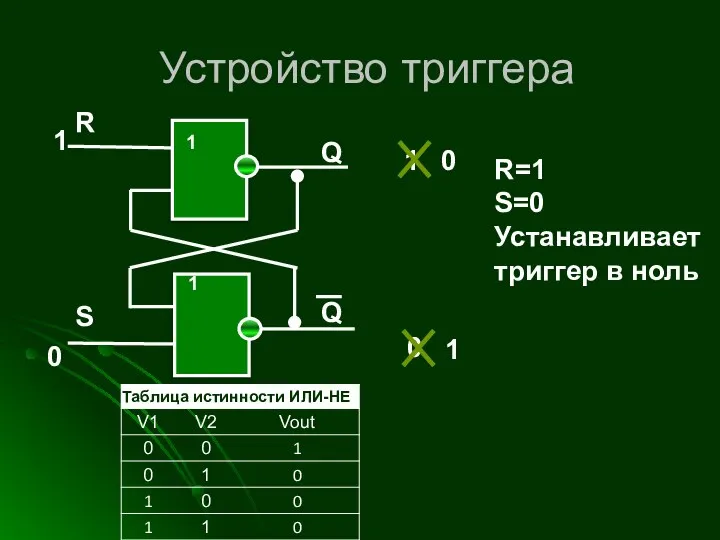

- 47. Устройство триггера 1 0 R=1 S=0 Устанавливает триггер в ноль 1 0 R S Q Q

- 48. Устройство триггера 1 1 R=1 S=1 Запрещенная комбинация R S Q Q

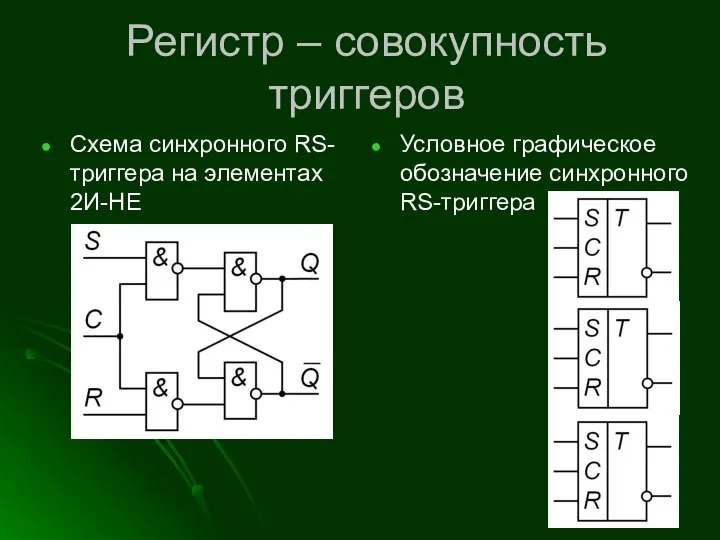

- 49. Регистр – совокупность триггеров Схема синхронного RS-триггера на элементах 2И-НЕ Условное графическое обозначение синхронного RS-триггера

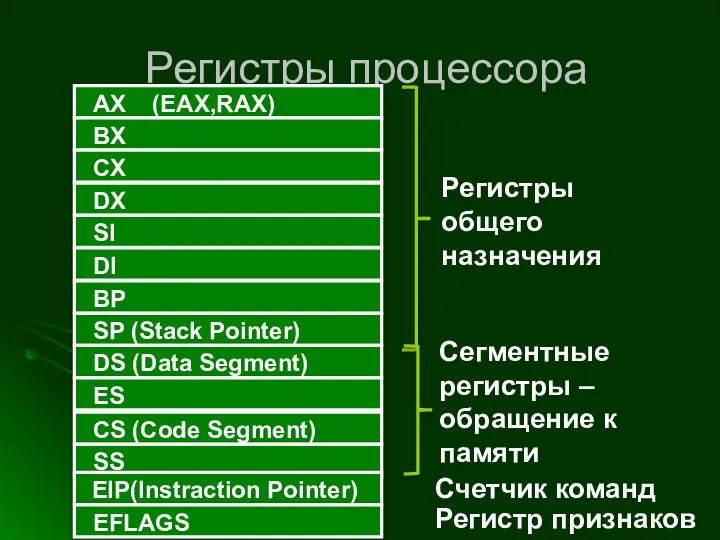

- 50. Регистры процессора Регистры общего назначения Сегментные регистры – обращение к памяти Счетчик команд Регистр признаков

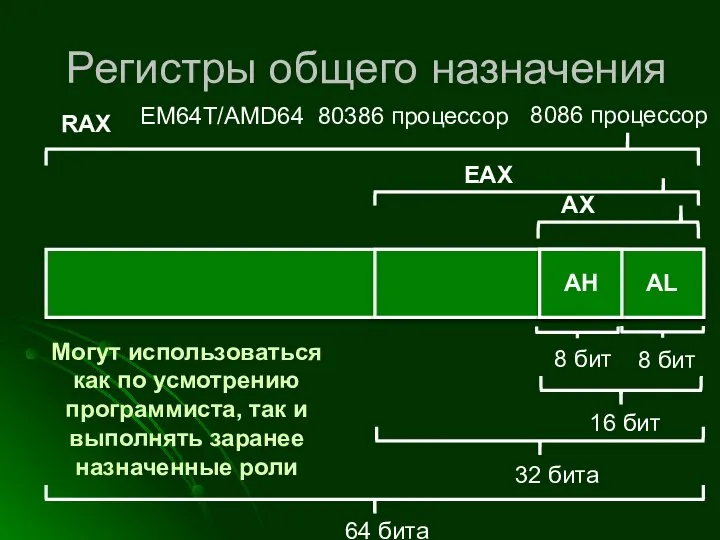

- 51. Регистры общего назначения AL AH 8 бит 8 бит AX 16 бит 8086 процессор EAX 80386

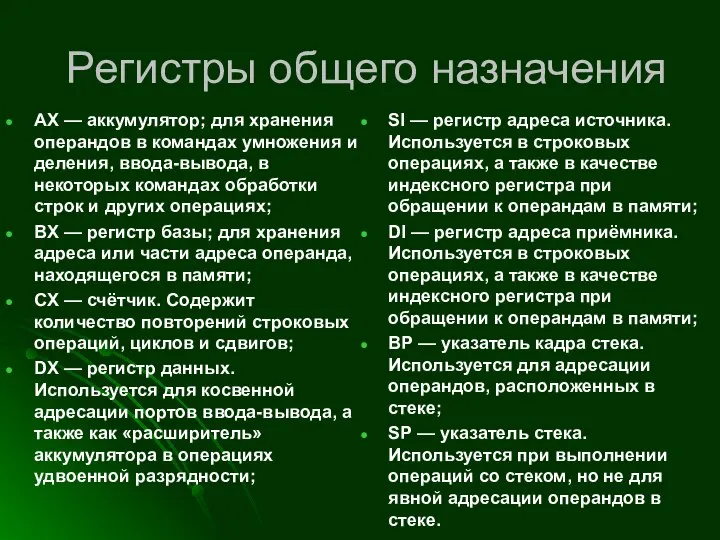

- 52. Регистры общего назначения AX — аккумулятор; для хранения операндов в командах умножения и деления, ввода-вывода, в

- 53. Сегментные регистры CS сегмента кода - в каком месте памяти находится программа DS сегмента данных -

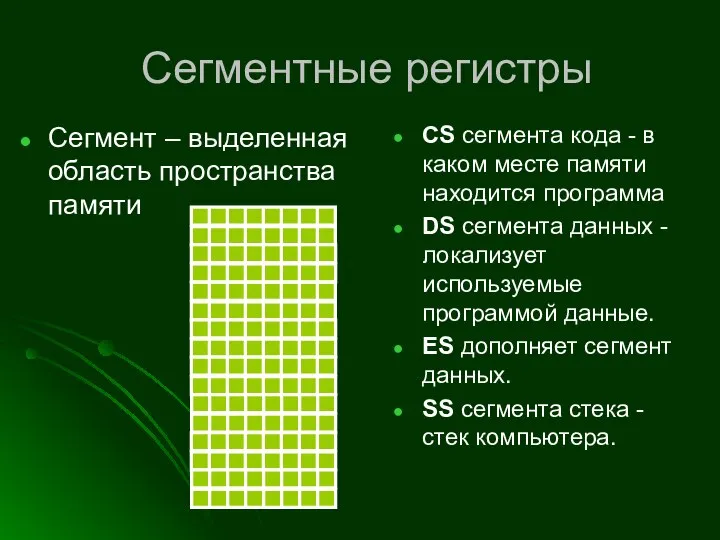

- 54. Регистр признаков Содержит слово состояния процессора

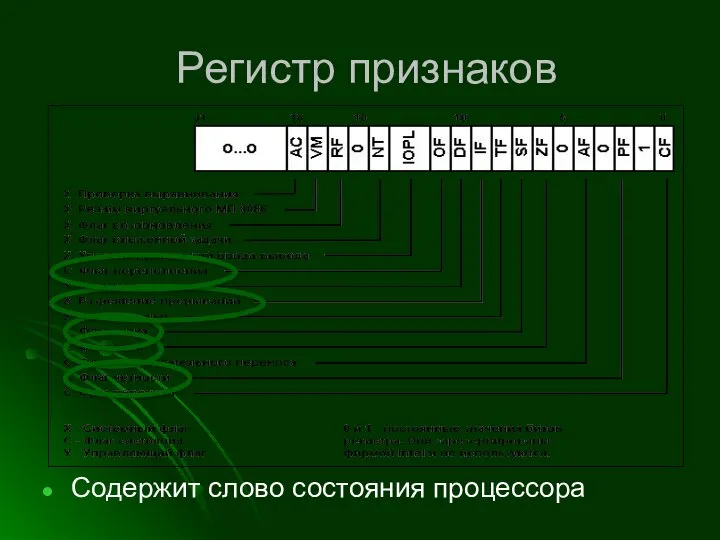

- 55. Стек Специальная область памяти Структура данных с методом доступа к элементам LIFO (Last In — First

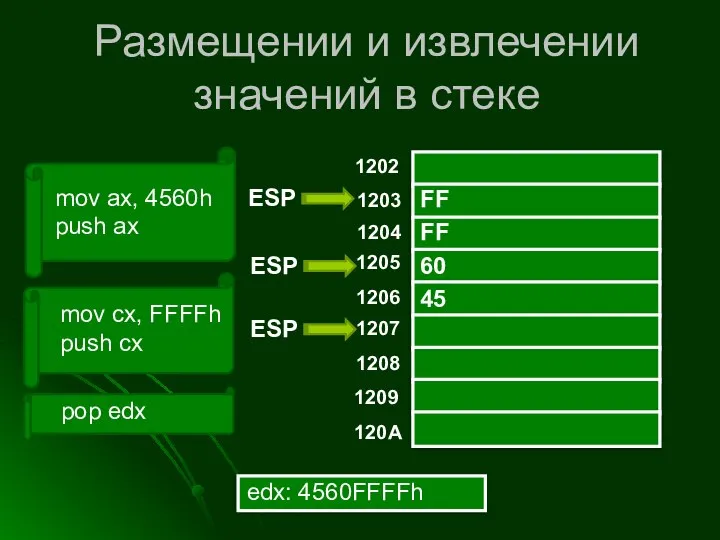

- 56. Размещении и извлечении значений в стеке mov ax, 4560h push ax mov cx, FFFFh push cx

- 57. Система команд Команды пересылки Команды обработки данных: Арифметические Логические команды Команды сдвига Команды ветвления или управления

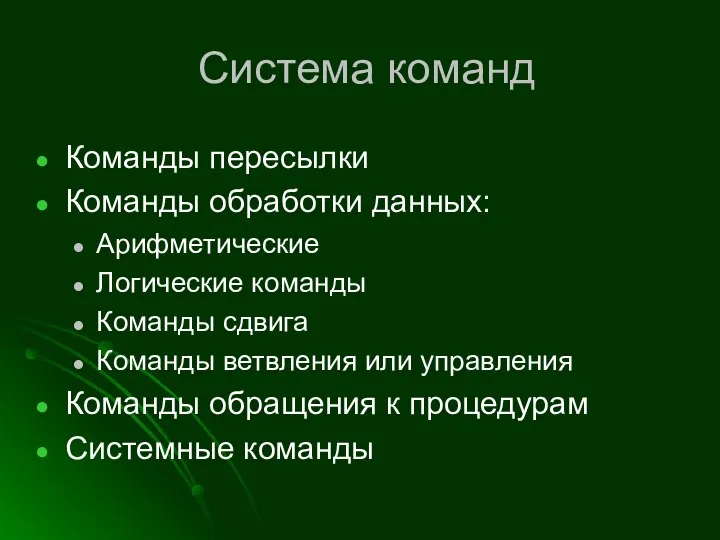

- 58. Команды пересылки Между регистрами Между памятью и регистрами A=B Mov mov ax,1234h AX = 1234h, AH

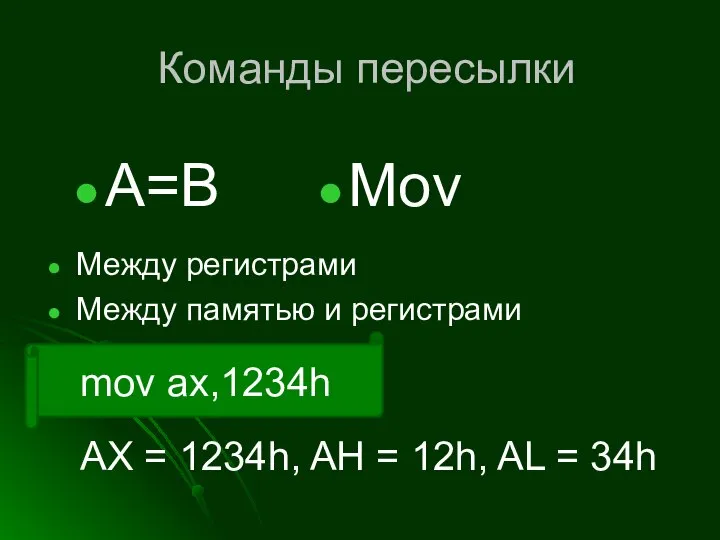

- 59. Арифметические команды i=i+1 A++ Сложение ADD Вычитание SUB Умножение MUL Деление DIV Увеличение INC Уменьшение DEC

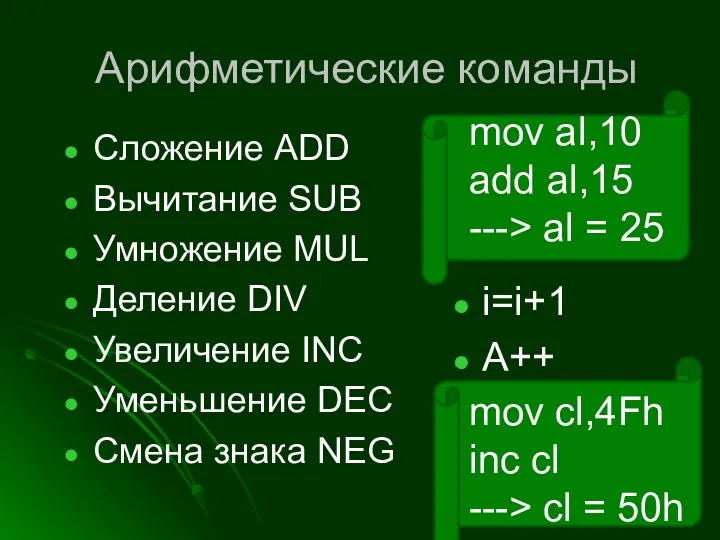

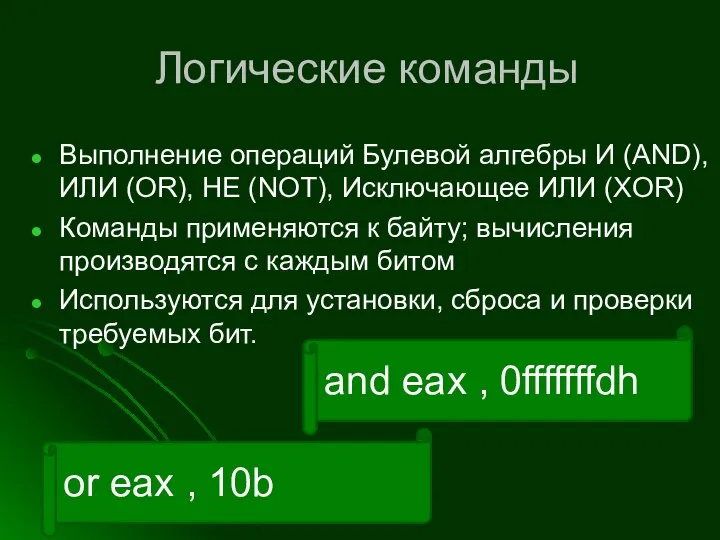

- 60. Логические команды Выполнение операций Булевой алгебры И (AND), ИЛИ (OR), НЕ (NOT), Исключающее ИЛИ (XOR) Команды

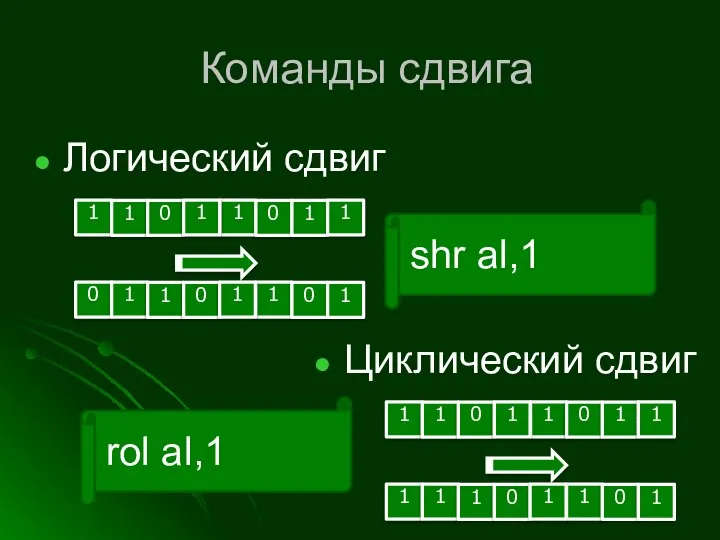

- 61. Команды сдвига Логический сдвиг 1 0 1 1 1 1 0 1 1 0 1 0

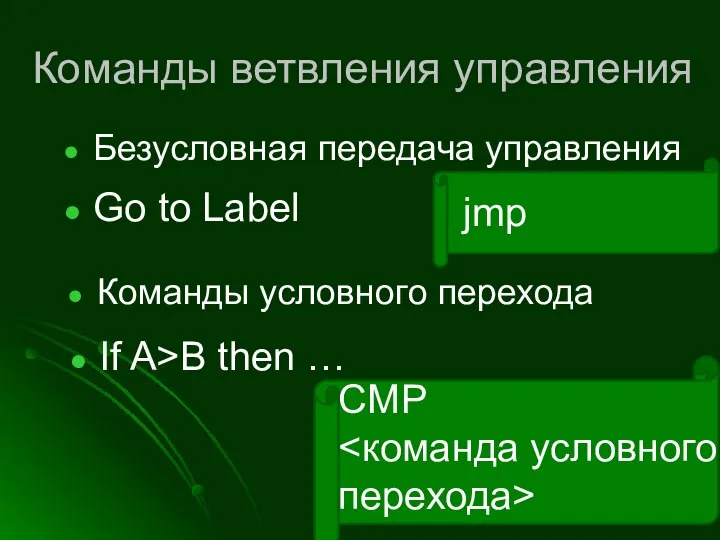

- 62. Команды ветвления управления Безусловная передача управления Go to Label jmp Команды условного перехода If A>B then

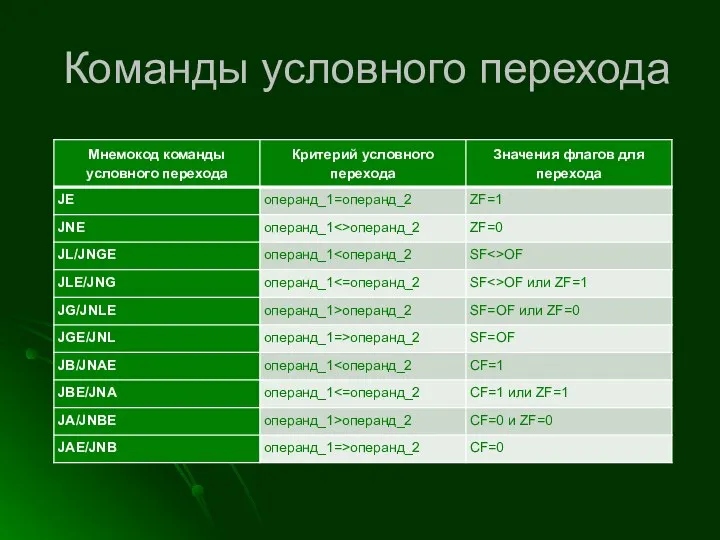

- 63. Команды условного перехода

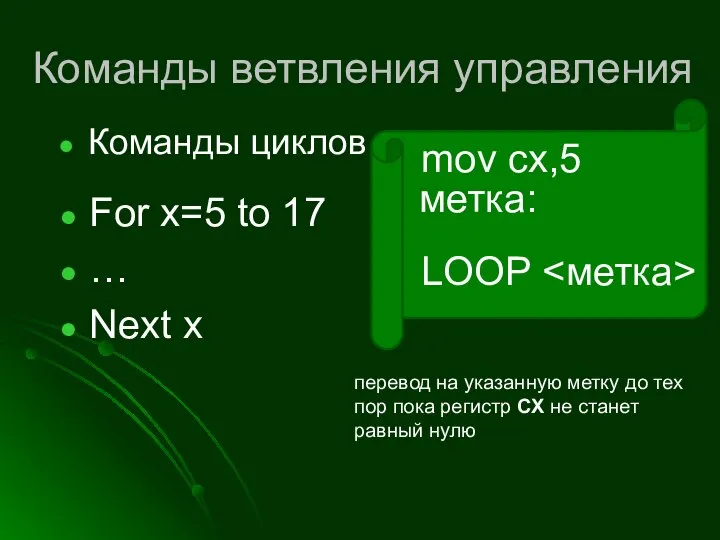

- 64. Команды ветвления управления For x=5 to 17 … Next x Команды циклов LOOP перевод на указанную

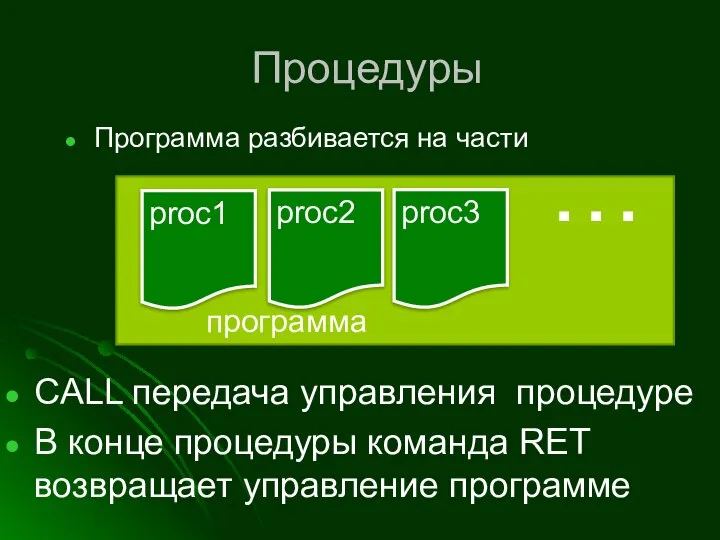

- 65. Процедуры Программа разбивается на части CALL передача управления процедуре В конце процедуры команда RET возвращает управление

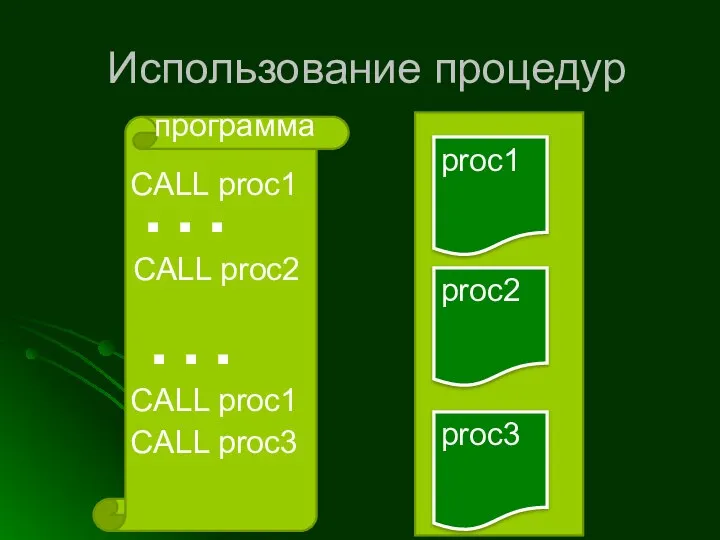

- 66. Использование процедур программа CALL proc1 CALL proc2 CALL proc1 … … CALL proc3

- 67. Обращения к процедурам По завершению процедуры процессор должен уметь вернуть управление программе Адрес возврата записывается в

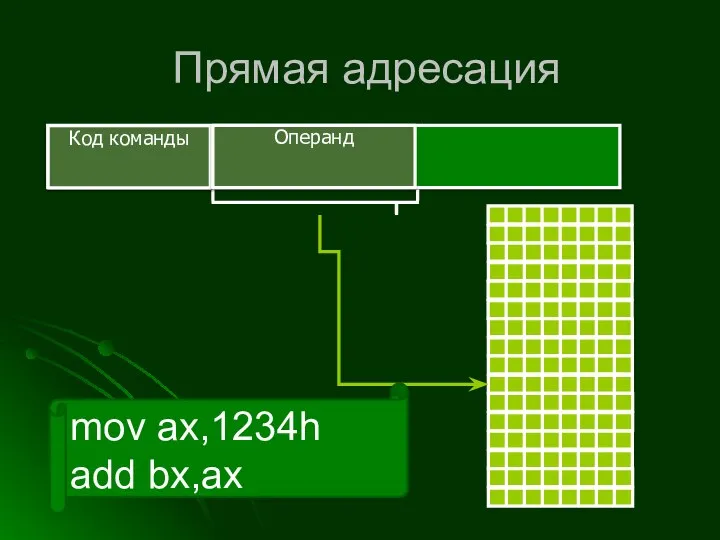

- 68. Адресация N (1,2,…) байт (в зависимости от архитектуры) Код команды Операнд 1 Операнд M … Прямая

- 69. Прямая адресация Код команды Операнд mov ax,1234h add bx,ax

- 71. Скачать презентацию

Великие учёные-химики

Великие учёные-химики советско финская война _1939_-_40_g.g

советско финская война _1939_-_40_g.g Транспортные задачи

Транспортные задачи Мезозойская эра

Мезозойская эра Элементарные сортировки. Сортировка выбором. Сортировка вставками. Сортировка Шелла. Перетасовка

Элементарные сортировки. Сортировка выбором. Сортировка вставками. Сортировка Шелла. Перетасовка Разработка параллельных программ в системах с распределенной памятью

Разработка параллельных программ в системах с распределенной памятью Архитектор. Задача архитектора

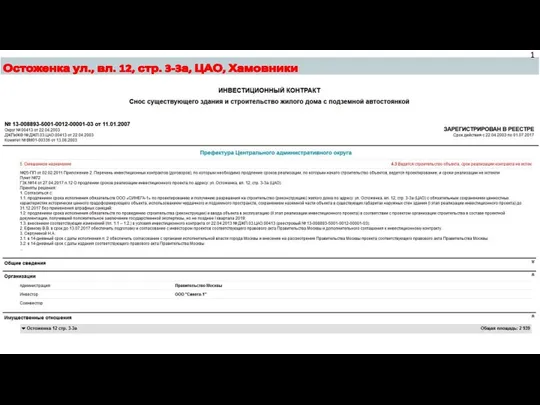

Архитектор. Задача архитектора Генеральны план. Остоженка ул.,вл.12,стр. 3-3а, ЦАО, Хамовники

Генеральны план. Остоженка ул.,вл.12,стр. 3-3а, ЦАО, Хамовники Электронные лампы

Электронные лампы Одномерные массивы целых чисел. Последовательный поиск элементов в массиве

Одномерные массивы целых чисел. Последовательный поиск элементов в массиве Интегрированные системы менеджмента в техносфере

Интегрированные системы менеджмента в техносфере Управление проектами. Лекция 2

Управление проектами. Лекция 2 Motion analysi

Motion analysi Shisha bar

Shisha bar Сказочная страна Сергея Чаплыгина Презентацию выполнил учащийся 6 «А» класса МОУ «СОШ №12 с УИОП» Некрасов Андрей Руководитель п

Сказочная страна Сергея Чаплыгина Презентацию выполнил учащийся 6 «А» класса МОУ «СОШ №12 с УИОП» Некрасов Андрей Руководитель п Основные факторы, вызывающие разрушение искусственных покрытий

Основные факторы, вызывающие разрушение искусственных покрытий Каждое утро жизнь возобновляется. Вечное чудо

Каждое утро жизнь возобновляется. Вечное чудо My favourite season

My favourite season Семейное устройство детей сирот

Семейное устройство детей сирот  Долговая безопасность бизнеса: новые возможности (на примере проекта Реестр должников МГО Деловой России)

Долговая безопасность бизнеса: новые возможности (на примере проекта Реестр должников МГО Деловой России) ЖЕЛЧНОКАМЕННАЯ БОЛЕЗНЬ 7

ЖЕЛЧНОКАМЕННАЯ БОЛЕЗНЬ 7 ОРГАНИЗАЦИЯ И ПРИНЦИПЫ ЭФФЕКТИВНОСТИ X. ЭМЕРСОНА

ОРГАНИЗАЦИЯ И ПРИНЦИПЫ ЭФФЕКТИВНОСТИ X. ЭМЕРСОНА  Почки

Почки толстый кишечник. брюшина

толстый кишечник. брюшина Возможности и основные службы (сервисы) сети Интернет

Возможности и основные службы (сервисы) сети Интернет На Афганской войне. Королёв Николай Иванович

На Афганской войне. Королёв Николай Иванович Презентация Срок временного хранения товаров. Операции с товарами, находящимися на временном хранении.

Презентация Срок временного хранения товаров. Операции с товарами, находящимися на временном хранении. Уровни и организации жизни

Уровни и организации жизни