Содержание

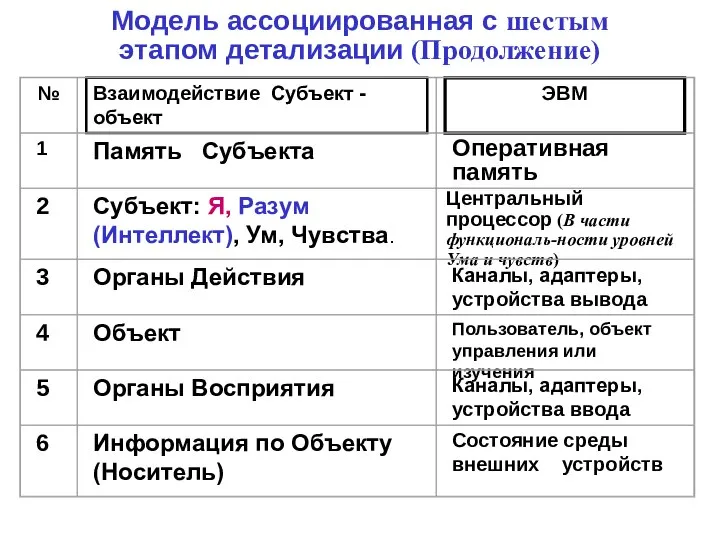

- 2. Модель ассоциированная с шестым этапом детализации (Продолжение)

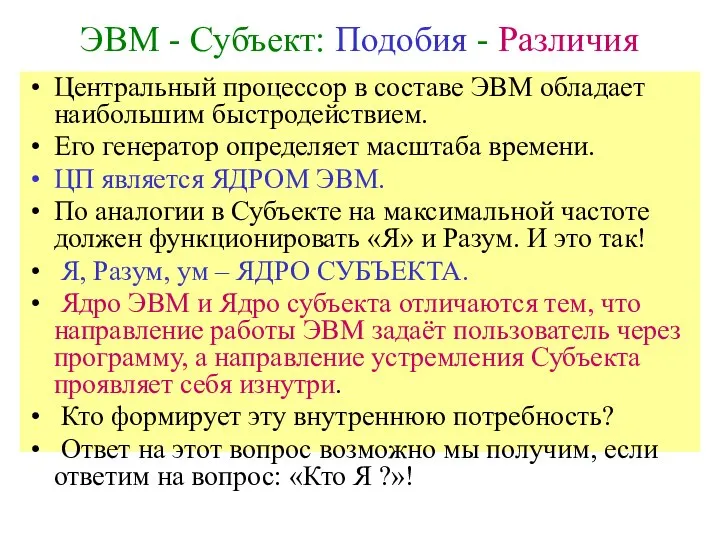

- 3. ЭВМ - Субъект: Подобия - Различия Центральный процессор в составе ЭВМ обладает наибольшим быстродействием. Его генератор

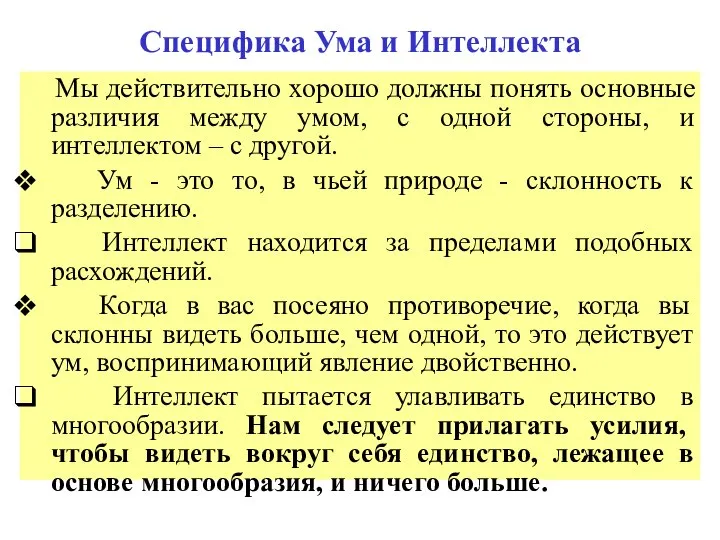

- 4. Специфика Ума и Интеллекта Мы действительно хорошо должны понять основные различия между умом, с одной стороны,

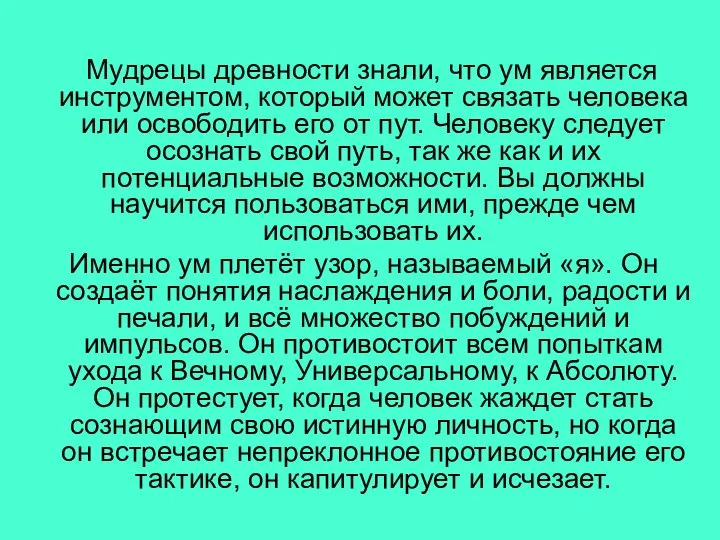

- 5. Мудрецы древности знали, что ум является инструментом, который может связать человека или освободить его от пут.

- 6. Содержание Информация о видах процессоров и разновидность архитектуры. Оперативная память и ее типы. Кэш память и

- 7. Процессор Центра́льный проце́ссор (ЦП; CPU — англ. céntral prócessing únit, дословно — центральное вычислительное устройство) —

- 8. Современные ЦП Современные ЦП, выполняемые в виде отдельных микросхем (чипов), реализующих все особенности, присущие данного рода

- 9. Разновидности Архитектур ЦП Архитектура фон Неймана Конвейерная архитектура Многоядерные процессоры Параллельная архитектура CISC-процессоры RISC-процессоры MISC-процессоры

- 10. Архитектура фон Неймана Большинство современных процессоров для персональных компьютеров в общем основаны на той или иной

- 11. Конвейерная архитектура Конвейерная архитектура (pipelining) была введена в центральный процессор с целью повышения быстродействия. Обычно для

- 12. Многоядерные процессоры Содержат несколько процессорных ядер в одном корпусе (на одном или нескольких кристаллах). Процессоры, предназначенные

- 13. Параллельная архитектура Архитектура фон Неймана обладает тем недостатком, что она последовательная. Какой бы огромный массив данных

- 14. CISC-процессоры Complex Instruction Set Computing — вычисления со сложным набором команд. Процессорная архитектура, основанная на усложнённом

- 15. RISC-процессоры Reduced Instruction Set Computing (technology) — вычисления с сокращённым набором команд. Архитектура процессоров, построенная на

- 16. MISC-процессоры Minimum Instruction Set Computing — вычисления с минимальным набором команд. Дальнейшее развитие идей команды Чака

- 17. Оперативная память Операти́вная па́мять (также ОЗУ — оперативное запоминающее устройство) — в информатике — память, это

- 18. В современных вычислительных устройствах, оперативная память выполнена по технологии динамической памяти с произвольным доступом (англ. dynamic

- 19. Схема взаимодействия ОП и др. элементов

- 20. Кэш память Впервые слово «кэш» в компьютерном контексте было использовано в 1967 году во время подготовки

- 21. Кэш — это память с большей скоростью доступа, предназначенная для ускорения обращения к данным, содержащимся постоянно

- 22. РЕГИСТРОВАЯ КЭШ-ПАМЯТЬ Регистровая КЭШ-память - высокоскоростная память сравнительно большой емкости, являющаяся буфером между ОП и МП

- 23. Два типа КЭШ-памяти КЭШ-память "с обратной записью" - результаты операций прежде, чем их записать в ОП,

- 24. ЭВМ и С Лекция № 6. Реферат. Центральный процессора (ЦП) предназначен для: обработки потока команд и

- 25. К блоку систем-ных средств БК - буфер каналов АП - адаптер памяти УБ- управление буферной памятью

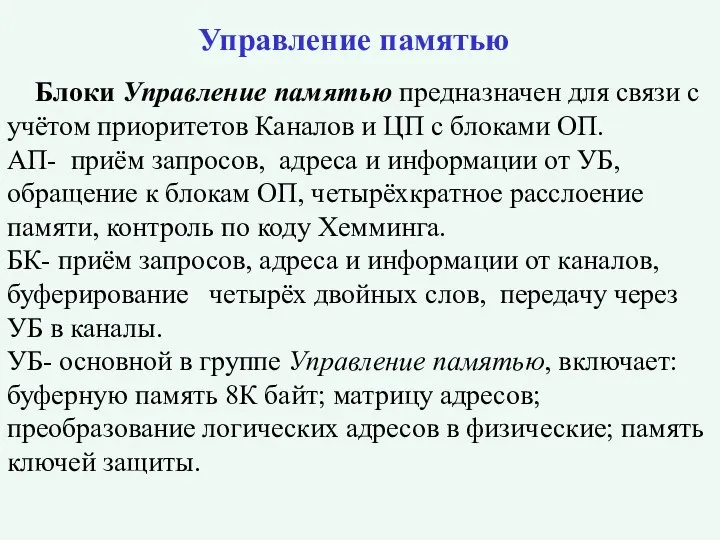

- 26. Управление памятью Блоки Управление памятью предназначен для связи с учётом приоритетов Каналов и ЦП с блоками

- 27. Центральное управление Группа блоков Центральное управление обрабатывает поток команд, адреса операндов, обращение в основную и местную

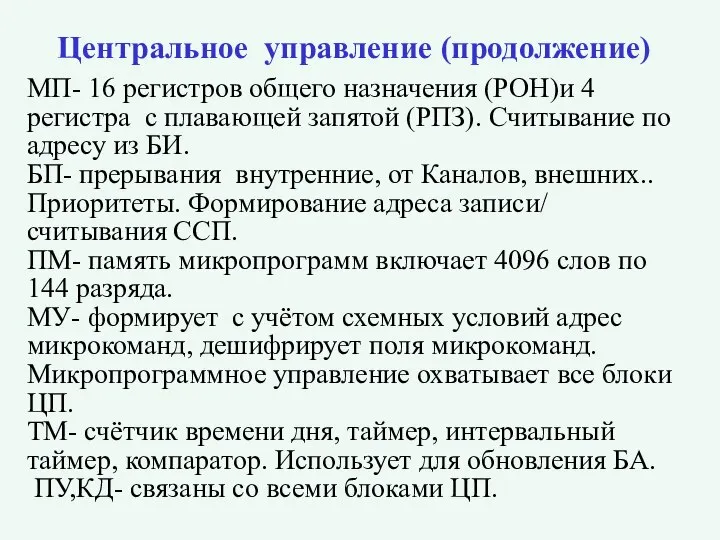

- 28. Центральное управление (продолжение) МП- 16 регистров общего назначения (РОН)и 4 регистра с плавающей запятой (РПЗ). Считывание

- 29. Структурная схема процессора ПЭВМ.

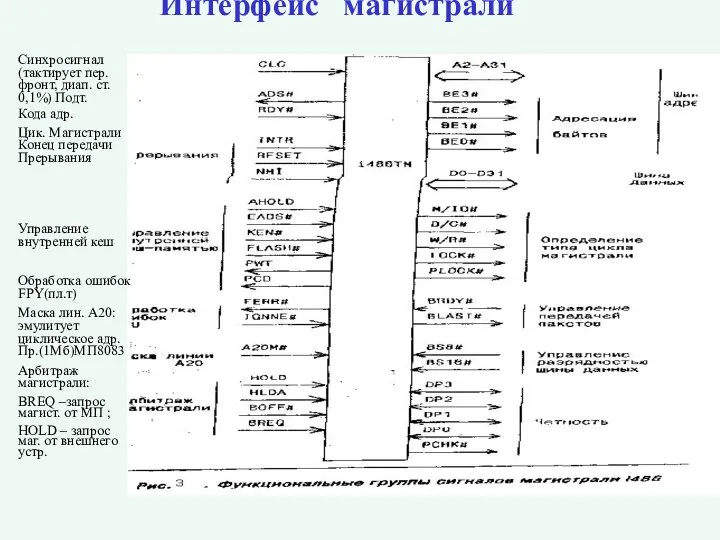

- 30. Интерфейс магистрали Синхросигнал (тактирует пер. фронт, диап. ст. 0,1%) Подт. Кода адр. Цик. Магистрали Конец передачи

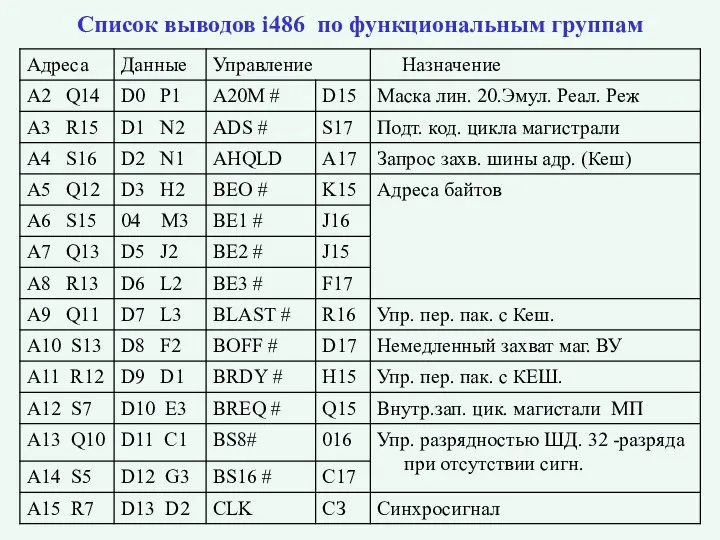

- 31. Список выводов i486 по функциональным группам

- 34. Эффективность ЦП На эффективность ЦП влияют следующие особенности структуры: • разрядность трактов передачи и обработки данных;

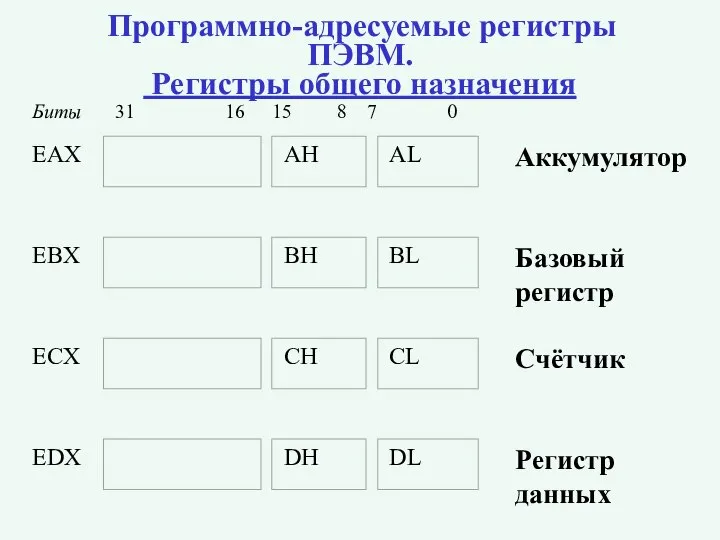

- 35. Программно-адресуемые регистры ПЭВМ. Процессор 80486 содержит 34 программно-адресуемых регистра. с точки зрения программиста 24 из них

- 36. Программно-адресуемые регистры ПЭВМ. Регистры общего назначения

- 37. Регистры-указатели

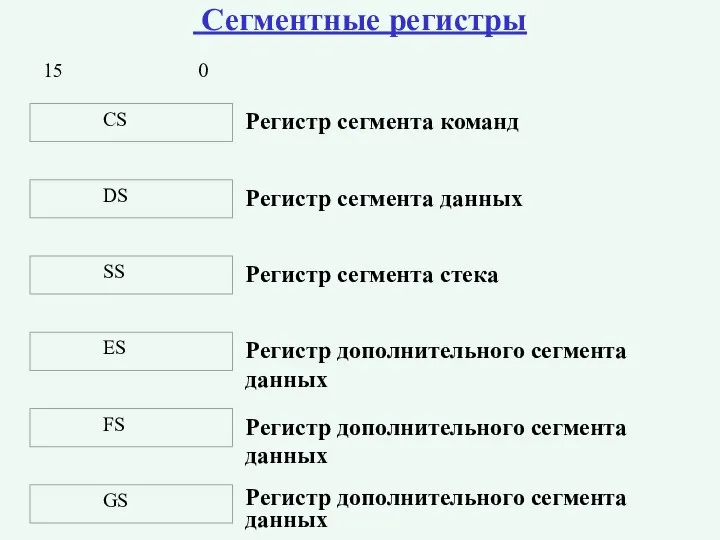

- 38. Сегментные регистры

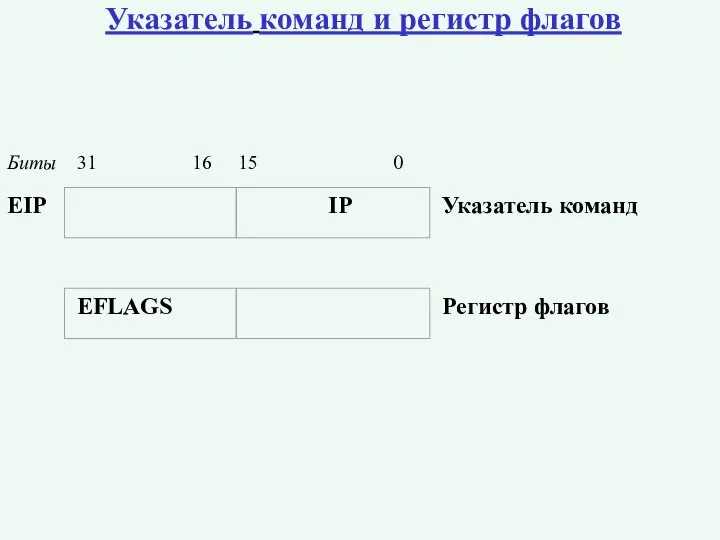

- 39. Указатель команд и регистр флагов

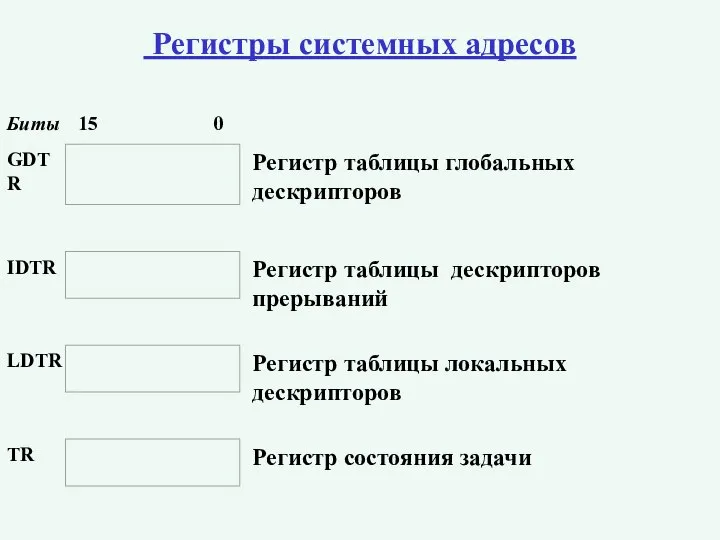

- 40. Регистры системных адресов

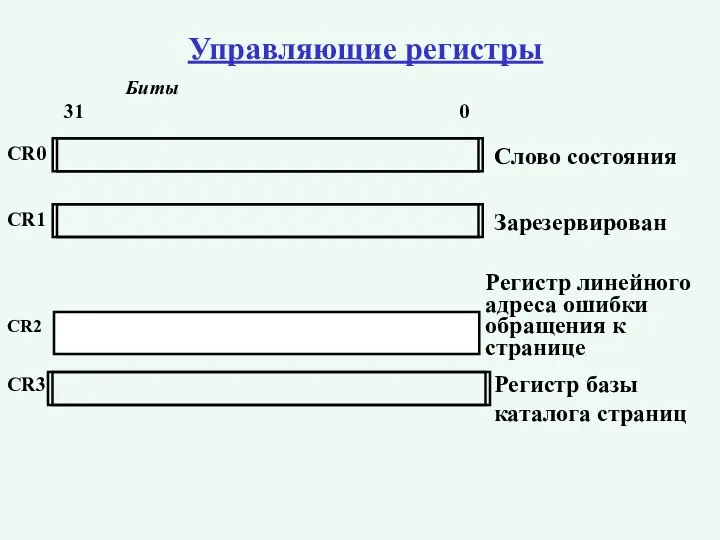

- 41. Управляющие регистры CR2 Биты 31 0 CR0 Слово состояния CR1 Зарезервирован Регистр линейного адреса ошибки обращения

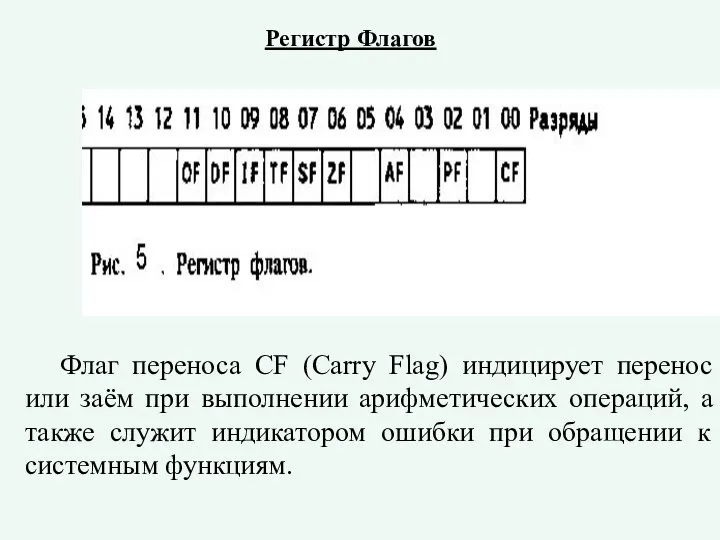

- 42. Регистр Флагов Флаг переноса CF (Carry Flag) индицирует перенос или заём при выполнении арифметических операций, а

- 43. Флаг паритета PF (Parity Flag) устанавливается в 1, если младшие 8 бит результата операции содержат четное

- 44. Флаги состояния автоматически устанавливаются процессором после выполнения каждой команды. Так, если в регистре AX держится число

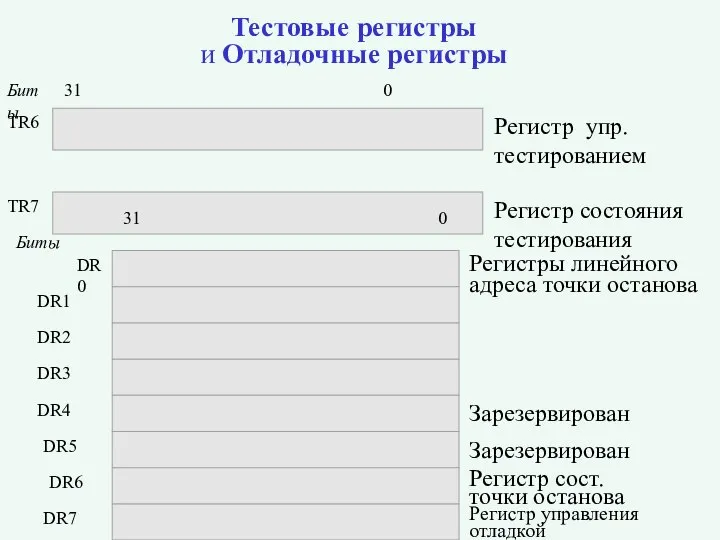

- 45. Тестовые регистры и Отладочные регистры

- 47. Скачать презентацию

Доходы бюджетов

Доходы бюджетов мониторы

мониторы Презентация на тему "Родительская любовь и Воспитание" - скачать презентации по Педагогике

Презентация на тему "Родительская любовь и Воспитание" - скачать презентации по Педагогике Одежда 15-16 веков

Одежда 15-16 веков Старинная русская одежда. (4 класс)

Старинная русская одежда. (4 класс) Расчет строительных конструкций

Расчет строительных конструкций Презентация Роль профсоюзов на рынке труда

Презентация Роль профсоюзов на рынке труда О весенней охоте

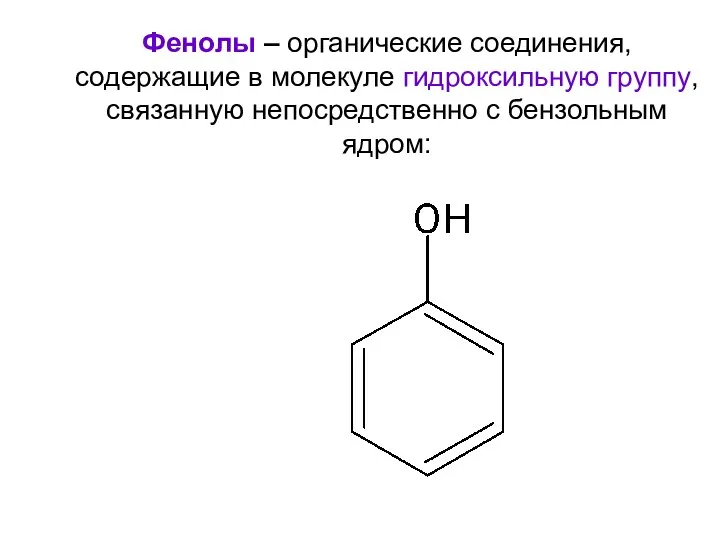

О весенней охоте Фенолы

Фенолы Нарушения обмена белков и нуклеиновых кислот

Нарушения обмена белков и нуклеиновых кислот Алкоголь и алкогольная зависимость

Алкоголь и алкогольная зависимость Презентация "Фонтаны Томска"

Презентация "Фонтаны Томска" День матери 2017

День матери 2017 О святости

О святости Клод Моне

Клод Моне Инфекционный мононуклеоз

Инфекционный мононуклеоз Устройство компьютера

Устройство компьютера  Алгоритмы и структуры данных на Python

Алгоритмы и структуры данных на Python Семейный клуб «РОДНИЧОК» 1 КЛАСС Классный руководитель – Чачина Людмила Васильевна

Семейный клуб «РОДНИЧОК» 1 КЛАСС Классный руководитель – Чачина Людмила Васильевна Снеговик спешит на карнавал - презентация для начальной школы_

Снеговик спешит на карнавал - презентация для начальной школы_ исИстория органов внутренних дел Российской Федерации.тория

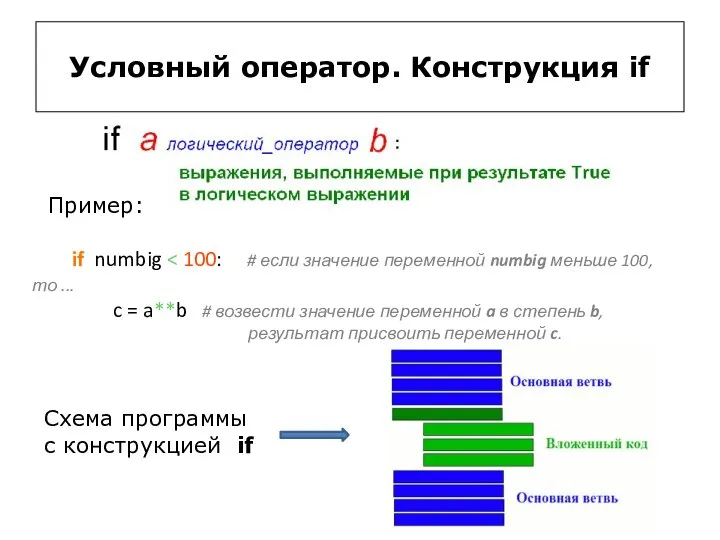

исИстория органов внутренних дел Российской Федерации.тория Условный оператор. Конструкция if

Условный оператор. Конструкция if Экипаж «IT Empire»

Экипаж «IT Empire» Двигатели «Камминз». Диагностика неисправностей

Двигатели «Камминз». Диагностика неисправностей Органы исполнительной власти в РФ

Органы исполнительной власти в РФ ИТ-архитектура предприятия. Применение модели Захмана для решения проблем, возникающих на этапе реализации IT-проекта

ИТ-архитектура предприятия. Применение модели Захмана для решения проблем, возникающих на этапе реализации IT-проекта Культура Средневековой Индии

Культура Средневековой Индии Проект Продвижение комплекса ГТО среди сверстников. Мариинский муниципальный район

Проект Продвижение комплекса ГТО среди сверстников. Мариинский муниципальный район