Содержание

- 2. Общие принципы функционирования КП Кэш-память – представляет собой организованную в виде ассоциативного запоминающего устройства, быстродействующую буферную

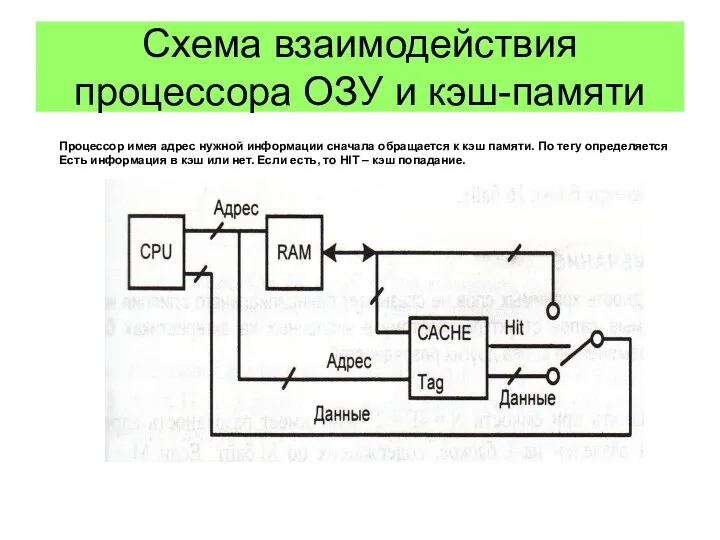

- 3. Схема взаимодействия процессора ОЗУ и кэш-памяти Процессор имея адрес нужной информации сначала обращается к кэш памяти.

- 4. Оценка времени доступа к памяти при кэш попадании Т ср = с + (1 – Н)

- 5. Факторы влияющие на эффективность применения кэш памяти Емкость кэш-памяти. Формат строки. Способ отображения основной памяти на

- 6. Термины Кэш промах. Кэш попадание. Размер кэш – памяти. Строка кэш памяти. Строка кэш-памяти 16-64 байт

- 7. Расположение кэш памяти Кристалл МП Корпус МП Кэш 1 команд Кэш 2 объединенный Кэш 3 объединенный

- 8. Принципы построения многоуровневой кэш-памяти Инклюзивный метод. Вся информация из верхних уровней содержится в нижних уровнях. Быстродействие.

- 9. Классификация КЭШ по способу отображения основной памяти Кэш память прямого отображения. Кэш память ассоциативная с множественным

- 10. Структура оперативной памяти и кэш-памяти Основная память делится на блоки одинакового размера с кратными адресами ячеек.

- 11. Кэш память прямого отображения Строка кэш Бит достоверности Тэг Данные Адреса ячеек ОЗУ Бит достоверности указывает

- 12. Соответствие адресов блоков ОП и строк кэш прямого отображения

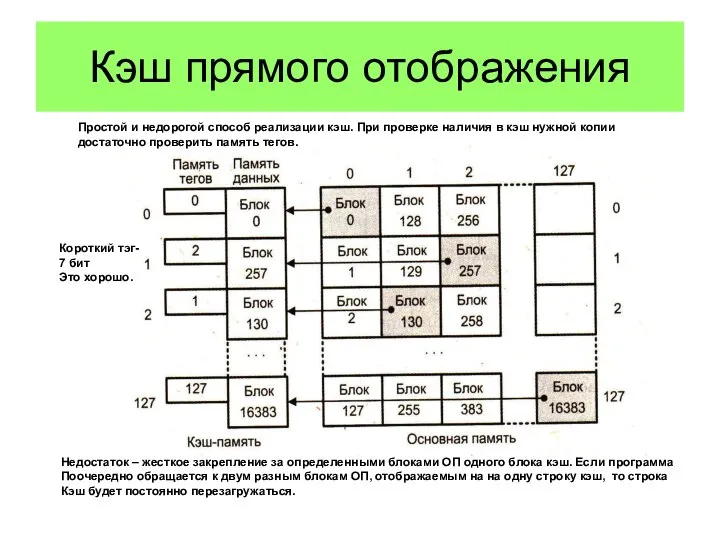

- 13. Кэш прямого отображения Простой и недорогой способ реализации кэш. При проверке наличия в кэш нужной копии

- 14. Организация кэш памяти прямого отображения Кэш Номер тэга Положение нужного байта в строке Строка кэш из

- 15. Кэш прямого отображения Пример: 32 битный виртуальный адрес тег строка слово байт 16 11 3 2

- 16. Полностью ассоциативная кэш память Позволяет преодолеть недостаток прямого кэш, разрешая загрузку любого блока ОП в любой

- 17. Организация полностью ассоциативной кэш памяти Любая ячейка ОЗУ может находится в любом месте КЭШа. Сложная структура,

- 18. Кэш память с частично ассоциативным отображением Сочетает достоинства полностью ассоциативной кэш и кэш прямого отображения. КЭШ

- 19. Соответствие блоков ОП и строк частично-ассоциативной кэш

- 20. Организация частично ассоциативной кэш – двухвходовой

- 21. Пример четырех входовой ассоциативной кэш-памяти Каждая ячейка памяти может храниться в 4 строках кэш Размеры строк

- 22. Стратегии замещения строк в кэш - LRU (Least Recenly Used) - замещается строка, к которой дольше

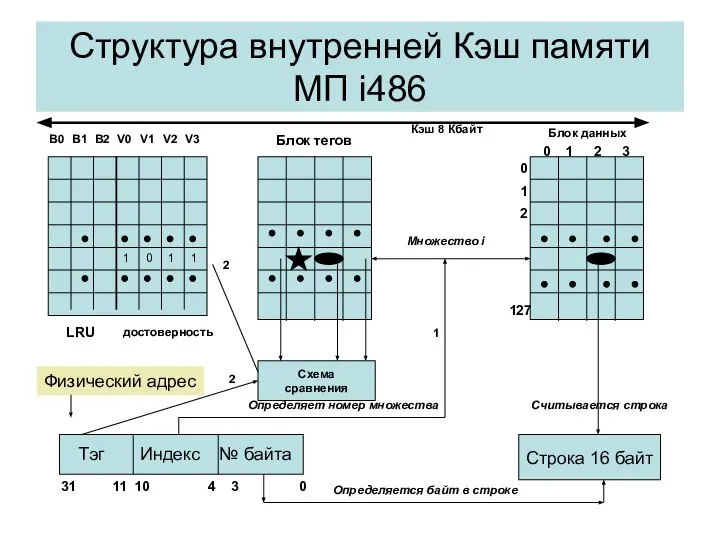

- 23. Структура внутренней Кэш памяти МП i486 B0 B1 B2 V0 V1 V2 V3 1 1 1

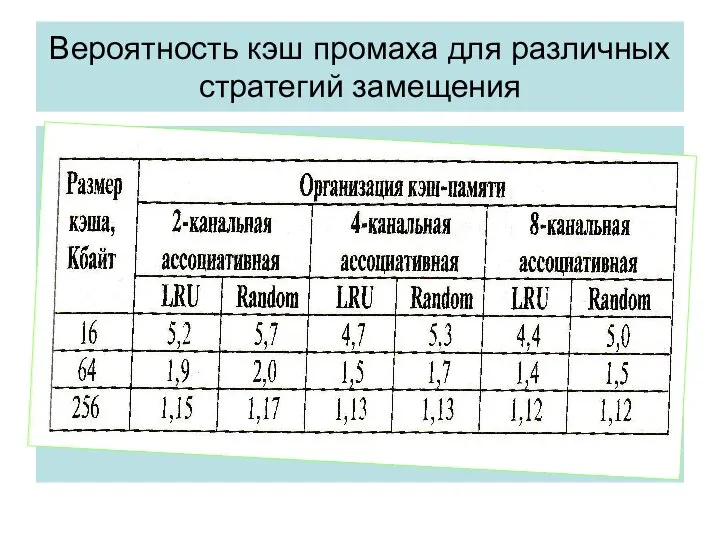

- 24. Вероятность кэш промаха для различных стратегий замещения

- 25. Согласование данных КЭШ и ОЗУ Сквозная запись. Данные ОЗУ обновляются вместе с КЭШ. Недостаток – снижение

- 26. Режим работы кэш Задается программной установкой разрядов CD (запрет кэширования) и NW (запрет сквозной записи) в

- 27. Обеспечение согласованности кэш памяти МП в мультипроцессорных системах МП а МП в ОЗУ Кэш а Кэш

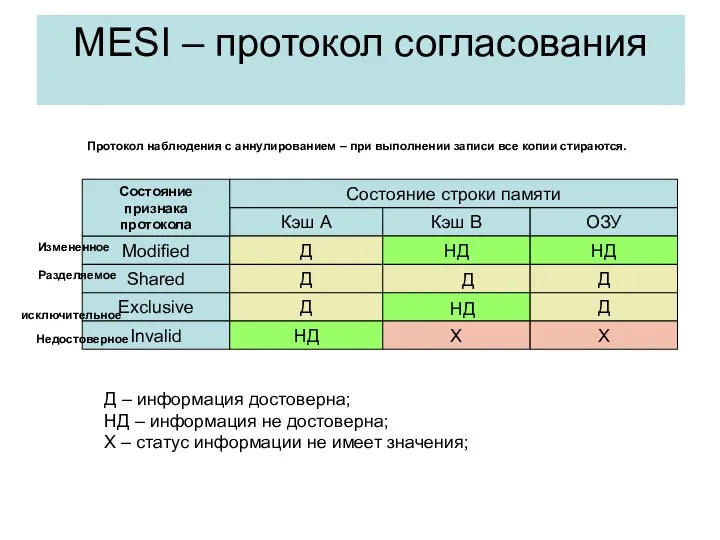

- 28. MESI – протокол согласования Кэш А Д Д Д НД Кэш В НД Х ОЗУ НД

- 30. Скачать презентацию

Русское народное зодчество

Русское народное зодчество Menedżer jako podmiot zarządzania

Menedżer jako podmiot zarządzania Анна Степановна Демидова

Анна Степановна Демидова Алгоритмы и исполнители

Алгоритмы и исполнители Презентация "Бюджет Российской Федерации" - скачать презентации по Экономике

Презентация "Бюджет Российской Федерации" - скачать презентации по Экономике Презентация по алгебре Линейная функция

Презентация по алгебре Линейная функция  Презентация КОММЕРЧЕСКАЯ ОРГАНИЗАЦИЯ С ИНОСТРАННЫМИ ИНВЕСТИЦИЯМИ

Презентация КОММЕРЧЕСКАЯ ОРГАНИЗАЦИЯ С ИНОСТРАННЫМИ ИНВЕСТИЦИЯМИ  Система Техническое обслуживание и ремонт оборудования

Система Техническое обслуживание и ремонт оборудования Разработка рабочих учебных программ педагогами образовательных учреждений

Разработка рабочих учебных программ педагогами образовательных учреждений Исчезающие животные (Англ)

Исчезающие животные (Англ)  Презентация Общие положения о таможенных процедурах в таможенном союзе

Презентация Общие положения о таможенных процедурах в таможенном союзе Классификация глосситов

Классификация глосситов Астрономия - древнейшая из наук

Астрономия - древнейшая из наук  Презентация Разработка миссии, целей и стратегии на примере фирмы «Полярис»

Презентация Разработка миссии, целей и стратегии на примере фирмы «Полярис» Ангиографические системы Toshiba Infinix и GE Innova. Основные компоненты, особенности эксплуатации

Ангиографические системы Toshiba Infinix и GE Innova. Основные компоненты, особенности эксплуатации My idol is Novak Djokovic

My idol is Novak Djokovic Проведение закупок по 223-ФЗ в электронной форме

Проведение закупок по 223-ФЗ в электронной форме Муниципальное общеобразовательное учреждение Белоносовская средняя общеобразовательная школа Урок обществознания в 10 классе

Муниципальное общеобразовательное учреждение Белоносовская средняя общеобразовательная школа Урок обществознания в 10 классе  организация работы детской поликлиники

организация работы детской поликлиники Мультиязычный интернет-каталог с автоматическим наполнением номенклатуры

Мультиязычный интернет-каталог с автоматическим наполнением номенклатуры «Папа, мама, я – спортивная семья». Спортивный праздник средняя школа №29

«Папа, мама, я – спортивная семья». Спортивный праздник средняя школа №29 Активний туризм як соціальне явище. Туризм: поняття та аспекти дослідження (Лекція №1)

Активний туризм як соціальне явище. Туризм: поняття та аспекти дослідження (Лекція №1) Портрет. Изучение нового материала

Портрет. Изучение нового материала Государственная гражданская служба

Государственная гражданская служба Программа кандидата на должность помощника депутата государственной думы РФ

Программа кандидата на должность помощника депутата государственной думы РФ Авиационные генераторы постоянного тока. (Тема 3.2)

Авиационные генераторы постоянного тока. (Тема 3.2) Роль библиотеки в лицензировании и аккредитации вуза

Роль библиотеки в лицензировании и аккредитации вуза  Предварительное расследование и его формы

Предварительное расследование и его формы