Содержание

- 2. Введение Общие принципы функционирования параллельных машин векторно-конвейерные массивно-параллельные компьютеры с широким командным словом систолические массивы гиперкубы

- 3. Классификация Флинна самая ранняя и наиболее известная классификация Классификация базируется на понятии потока - последовательности элементов

- 4. Дополнения Ванга и Бриггса Патч для архитектуры Флинна Детализирует классы архитектур : SIMD,SISD,MIMD Класс SISD разбивается

- 5. Классификация Фенга Классификация вычислительных систем на основе двух простых характеристик Число бит n в машинном слове,

- 6. Классификация Шора Выделение типичных способов компоновки вычислительных систем на основе фиксированного числа базисных блоков: устройства управления,

- 7. Классификация Шора Если объединить принципы построения машин I и II, то получим машину III. Эта машина

- 8. Классификация Шора Если ввести непосредственные линейные связи между соседними процессорными элементами машины IV, например в виде

- 9. Классификация Хендлера основа классификации - явное описание возможностей параллельной и конвейерной обработки информации вычислительной системой способы

- 10. Классификация Хокни Детализация классификции Флинна систематизации компьютеров, попадающих в класс MIMD по систематике Флинна. Множественный поток

- 11. Классификация Джонсона классификацию MIMD архитектур на основе структуры памяти и реализации механизма взаимодействия и синхронизации между

- 12. Классификация Базу Любую параллельную вычислительную систему можно однозначно описать последовательностью решений, принятых на этапе ее проектирования,

- 13. Классификация Кришнамарфи аналог Базу для классификации параллельных вычислительных систем предлагает использовать четыре характеристики степень гранулярности; способ

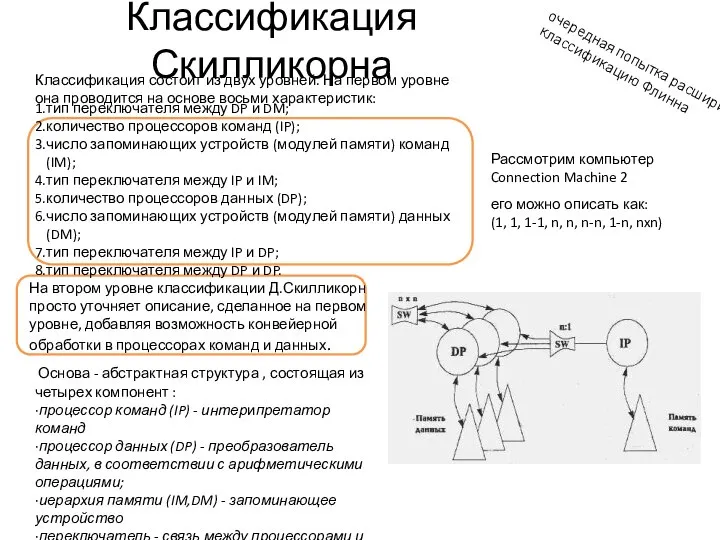

- 14. Классификация Скилликорна очередная попытка расширить классификацию Флинна Классификация состоит из двух уровней. На первом уровне она

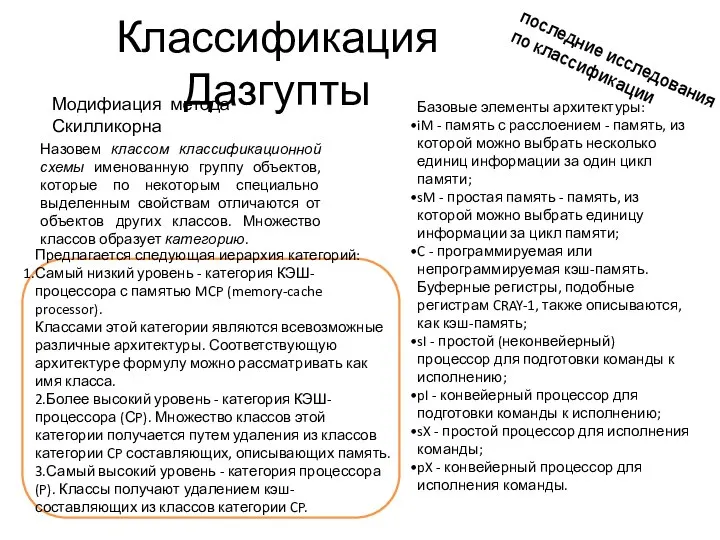

- 15. Классификация Дазгупты последние исследования по классификации Модифиация метода Скилликорна Назовем классом классификационной схемы именованную группу объектов,

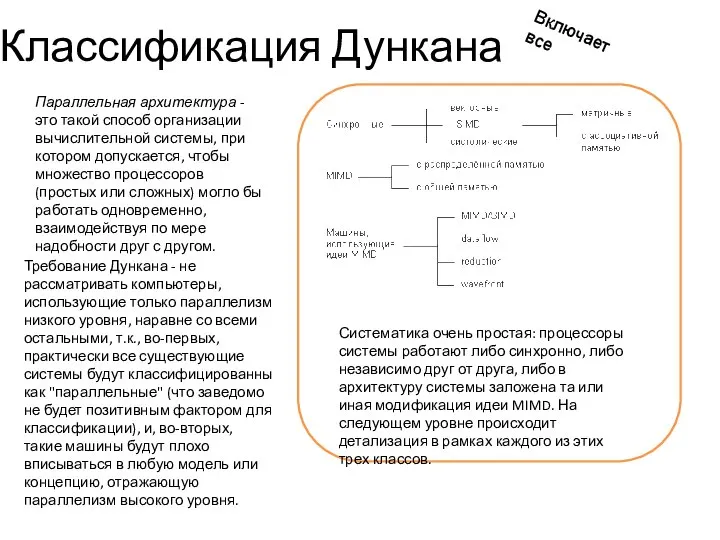

- 16. Классификация Дункана Систематика очень простая: процессоры системы работают либо синхронно, либо независимо друг от друга, либо

- 18. Скачать презентацию

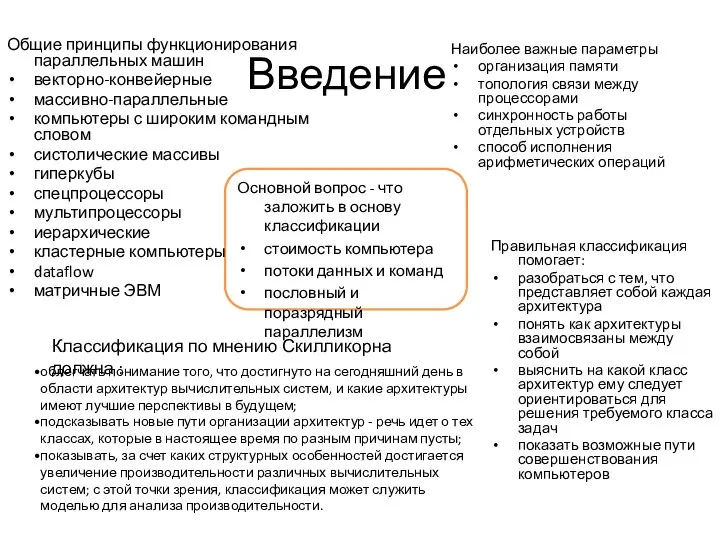

Введение

Общие принципы функционирования параллельных машин

векторно-конвейерные

массивно-параллельные

компьютеры с широким командным словом

систолические массивы

гиперкубы

спецпроцессоры

мультипроцессоры

иерархические

кластерные компьютеры

dataflow

матричные

Введение

Общие принципы функционирования параллельных машин

векторно-конвейерные

массивно-параллельные

компьютеры с широким командным словом

систолические массивы

гиперкубы

спецпроцессоры

мультипроцессоры

иерархические

кластерные компьютеры

dataflow

матричные

Наиболее важные параметры

организация памяти

топология связи между процессорами

синхронность работы отдельных устройств

способ исполнения арифметических операций

Основной вопрос - что заложить в основу классификации

стоимость компьютера

потоки данных и команд

пословный и поразрядный параллелизм

Правильная классификация помогает:

разобраться с тем, что представляет собой каждая архитектура

понять как архитектуры взаимосвязаны между собой

выяснить на какой класс архитектур ему следует ориентироваться для решения требуемого класса задач

показать возможные пути совершенствования компьютеров

облегчать понимание того, что достигнуто на сегодняшний день в области архитектур вычислительных систем, и какие архитектуры имеют лучшие перспективы в будущем;

подсказывать новые пути организации архитектур - речь идет о тех классах, которые в настоящее время по разным причинам пусты;

показывать, за счет каких структурных особенностей достигается увеличение производительности различных вычислительных систем; с этой точки зрения, классификация может служить моделью для анализа производительности.

Классификация по мнению Скилликорна должна :

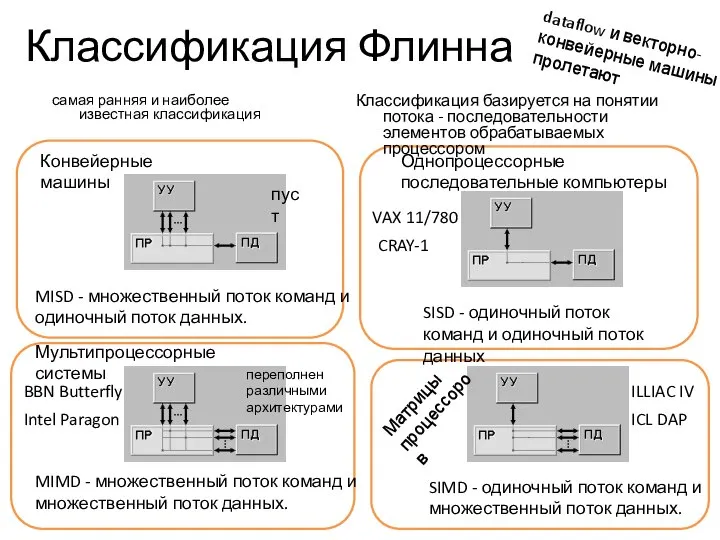

Классификация Флинна

самая ранняя и наиболее известная классификация

Классификация базируется на понятии потока

Классификация Флинна

самая ранняя и наиболее известная классификация

Классификация базируется на понятии потока

SISD - одиночный поток команд и одиночный поток данных

SIMD - одиночный поток команд и множественный поток данных.

MISD - множественный поток команд и одиночный поток данных.

MIMD - множественный поток команд и множественный поток данных.

Однопроцессорные последовательные компьютеры

Матрицы процессоров

Мультипроцессорные системы

Конвейерные машины

VAX 11/780

CRAY-1

ILLIAC IV

ICL DAP

BBN Butterfly

Intel Paragon

dataflow и векторно-конвейерные машины пролетают

переполнен различными архитектурами

пуст

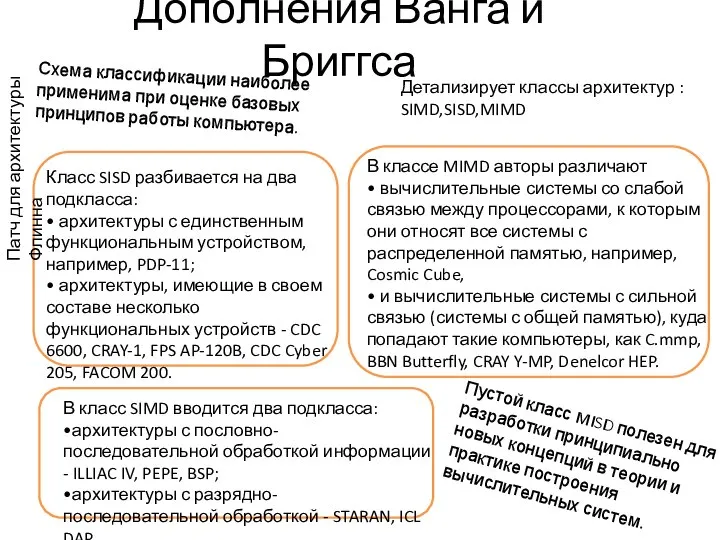

Дополнения Ванга и Бриггса

Патч для архитектуры Флинна

Детализирует классы архитектур : SIMD,SISD,MIMD

Класс

Дополнения Ванга и Бриггса

Патч для архитектуры Флинна

Детализирует классы архитектур : SIMD,SISD,MIMD

Класс

• архитектуры с единственным функциональным устройством, например, PDP-11;

• архитектуры, имеющие в своем составе несколько функциональных устройств - CDC 6600, CRAY-1, FPS AP-120B, CDC Cyber 205, FACOM 200.

В класс SIMD вводится два подкласса:

•архитектуры с пословно-последовательной обработкой информации - ILLIAC IV, PEPE, BSP;

•архитектуры с разрядно-последовательной обработкой - STARAN, ICL DAP.

В классе MIMD авторы различают

• вычислительные системы со слабой связью между процессорами, к которым они относят все системы с распределенной памятью, например, Cosmic Cube,

• и вычислительные системы с сильной связью (системы с общей памятью), куда попадают такие компьютеры, как C.mmp, BBN Butterfly, CRAY Y-MP, Denelcor HEP.

Пустой класс MISD полезен для разработки принципиально новых концепций в теории и практике построения вычислительных систем.

Схема классификации наиболее применима при оценке базовых принципов работы компьютера.

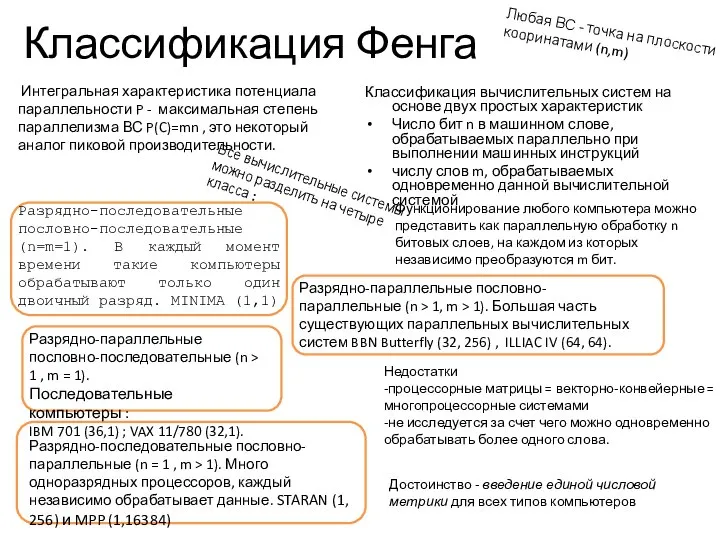

Классификация Фенга

Классификация вычислительных систем на основе двух простых характеристик

Число бит n

Классификация Фенга

Классификация вычислительных систем на основе двух простых характеристик

Число бит n

числу слов m, обрабатываемых одновременно данной вычислительной системой

Функционирование любого компьютера можно представить как параллельную обработку n битовых слоев, на каждом из которых независимо преобразуются m бит.

Интегральная характеристика потенциала параллельности P - максимальная степень параллелизма ВС P(C)=mn , это некоторый аналог пиковой производительности.

Любая ВС - точка на плоскости с кооринатами (n,m)

Все вычислительные системы можно разделить на четыре класса :

Разрядно-последовательные пословно-последовательные (n=m=1). В каждый момент времени такие компьютеры обрабатывают только один двоичный разряд. MINIMA (1,1)

Разрядно-параллельные пословно-последовательные (n > 1 , m = 1).

Последовательные компьютеры :

IBM 701 (36,1) ; VAX 11/780 (32,1).

Разрядно-последовательные пословно-параллельные (n = 1 , m > 1). Много одноразрядных процессоров, каждый независимо обрабатывает данные. STARAN (1, 256) и MPP (1,16384)

Разрядно-параллельные пословно-параллельные (n > 1, m > 1). Большая часть существующих параллельных вычислительных систем BBN Butterfly (32, 256) , ILLIAC IV (64, 64).

Недостатки

-процессорные матрицы = векторно-конвейерные = многопроцессорные системами

-не исследуется за счет чего можно одновременно обрабатывать более одного слова.

Достоинство - введение единой числовой метрики для всех типов компьютеров

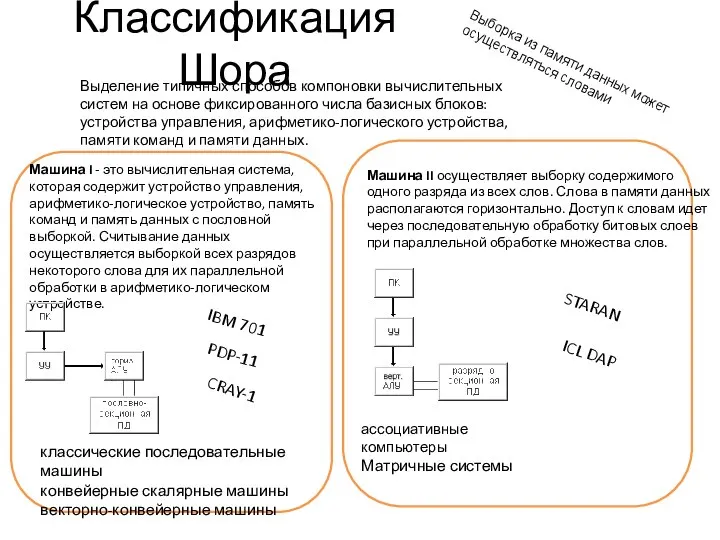

Классификация Шора

Выделение типичных способов компоновки вычислительных систем на основе фиксированного числа

Классификация Шора

Выделение типичных способов компоновки вычислительных систем на основе фиксированного числа

Выборка из памяти данных может осуществляться словами

Машина I - это вычислительная система, которая содержит устройство управления, арифметико-логическое устройство, память команд и память данных с пословной выборкой. Считывание данных осуществляется выборкой всех разрядов некоторого слова для их параллельной обработки в арифметико-логическом устройстве.

классические последовательные машины

конвейерные скалярные машины

векторно-конвейерные машины

IBM 701

PDP-11

CRAY-1

Машина II осуществляет выборку содержимого

одного разряда из всех слов. Слова в памяти данных располагаются горизонтально. Доступ к словам идет через последовательную обработку битовых слоев

при параллельной обработке множества слов.

ассоциативные компьютеры

Матричные системы

STARAN

ICL DAP

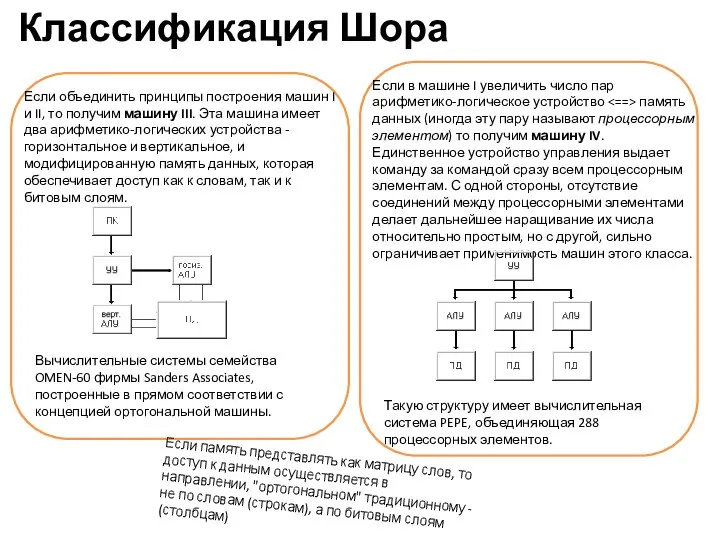

Классификация Шора

Если объединить принципы построения машин I и II, то получим

Классификация Шора

Если объединить принципы построения машин I и II, то получим

Вычислительные системы семейства OMEN-60 фирмы Sanders Associates, построенные в прямом соответствии с концепцией ортогональной машины.

Если память представлять как матрицу слов, то доступ к данным осуществляется в направлении, "ортогональном" традиционному - не по словам (строкам), а по битовым слоям (столбцам)

Если в машине I увеличить число пар арифметико-логическое устройство <==> память данных (иногда эту пару называют процессорным элементом) то получим машину IV. Единственное устройство управления выдает команду за командой сразу всем процессорным элементам. С одной стороны, отсутствие соединений между процессорными элементами делает дальнейшее наращивание их числа относительно простым, но с другой, сильно ограничивает применимость машин этого класса.

Такую структуру имеет вычислительная система PEPE, объединяющая 288 процессорных элементов.

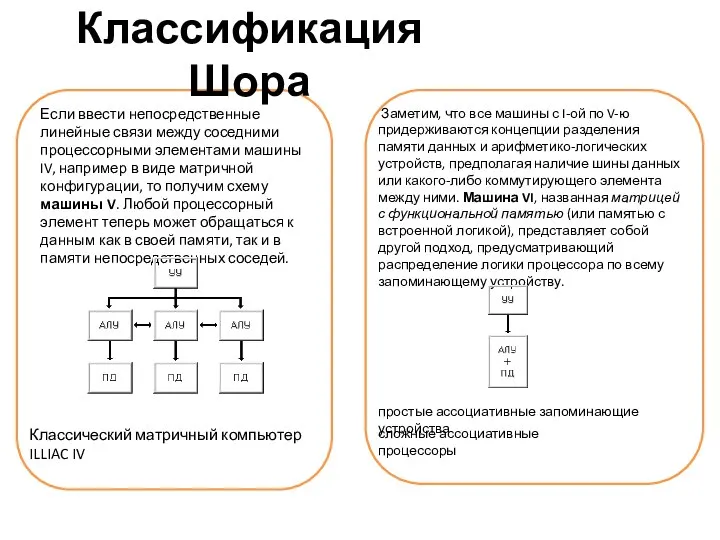

Классификация Шора

Если ввести непосредственные линейные связи между соседними процессорными элементами машины

Классификация Шора

Если ввести непосредственные линейные связи между соседними процессорными элементами машины

Классический матричный компьютер ILLIAC IV

Заметим, что все машины с I-ой по V-ю придерживаются концепции разделения памяти данных и арифметико-логических устройств, предполагая наличие шины данных или какого-либо коммутирующего элемента между ними. Машина VI, названная матрицей с функциональной памятью (или памятью с встроенной логикой), представляет собой другой подход, предусматривающий распределение логики процессора по всему запоминающему устройству.

простые ассоциативные запоминающие устройства

сложные ассоциативные процессоры

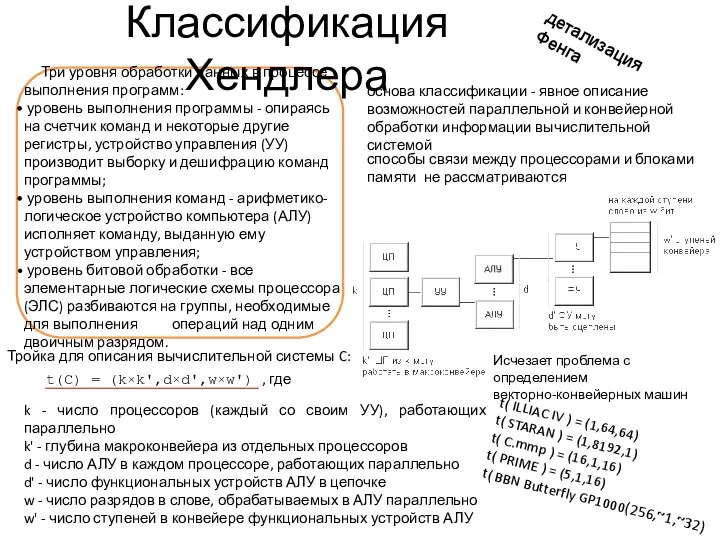

Классификация Хендлера

основа классификации - явное описание возможностей параллельной и конвейерной обработки

Классификация Хендлера

основа классификации - явное описание возможностей параллельной и конвейерной обработки

способы связи между процессорами и блоками памяти не рассматриваются

Три уровня обработки данных в процессе выполнения программ:

уровень выполнения программы - опираясь на счетчик команд и некоторые другие регистры, устройство управления (УУ) производит выборку и дешифрацию команд программы;

уровень выполнения команд - арифметико-логическое устройство компьютера (АЛУ) исполняет команду, выданную ему устройством управления;

уровень битовой обработки - все элементарные логические схемы процессора (ЭЛС) разбиваются на группы, необходимые для выполнения операций над одним двоичным разрядом.

t(С) = (k×k',d×d',w×w') , где

Тройка для описания вычислительной системы C:

k - число процессоров (каждый со своим УУ), работающих параллельно

k' - глубина макроконвейера из отдельных процессоров

d - число АЛУ в каждом процессоре, работающих параллельно

d' - число функциональных устройств АЛУ в цепочке

w - число разрядов в слове, обрабатываемых в АЛУ параллельно

w' - число ступеней в конвейере функциональных устройств АЛУ

детализация Фенга

Исчезает проблема с определением

векторно-конвейерных машин

t( ILLIAC IV ) = (1,64,64)

t( STARAN ) = (1,8192,1)

t( C.mmp ) = (16,1,16)

t( PRIME ) = (5,1,16)

t( BBN Butterfly GP1000(256,~1,~32)

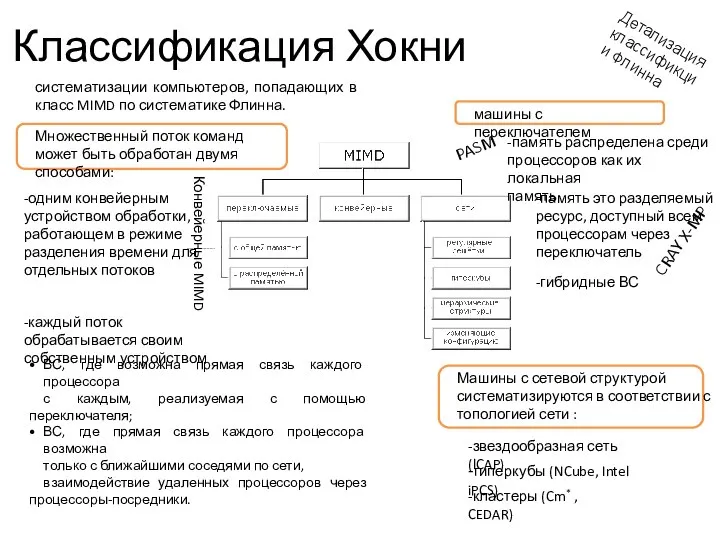

Классификация Хокни

Детализация классификции Флинна

систематизации компьютеров, попадающих в класс MIMD по систематике

Классификация Хокни

Детализация классификции Флинна

систематизации компьютеров, попадающих в класс MIMD по систематике

Множественный поток команд может быть обработан двумя способами:

-одним конвейерным устройством обработки, работающем в режиме разделения времени для отдельных потоков

Конвейерные MIMD

-каждый поток обрабатывается своим собственным устройством

ВС, где возможна прямая связь каждого процессора

с каждым, реализуемая с помощью переключателя;

ВС, где прямая связь каждого процессора возможна

только с ближайшими соседями по сети,

взаимодействие удаленных процессоров через процессоры-посредники.

машины с переключателем

память распределена среди процессоров как их локальная

-память распределена среди процессоров как их локальная

память

-память это разделяемый ресурс, доступный всем процессорам через переключатель

-гибридные ВС

Машины с сетевой структурой систематизируются в соответствии с топологией сети :

-звездообразная сеть (lCAP)

-гиперкубы (NCube, Intel iPCS)

-кластеры (Cm* , CEDAR)

PASM

CRAY X-MP

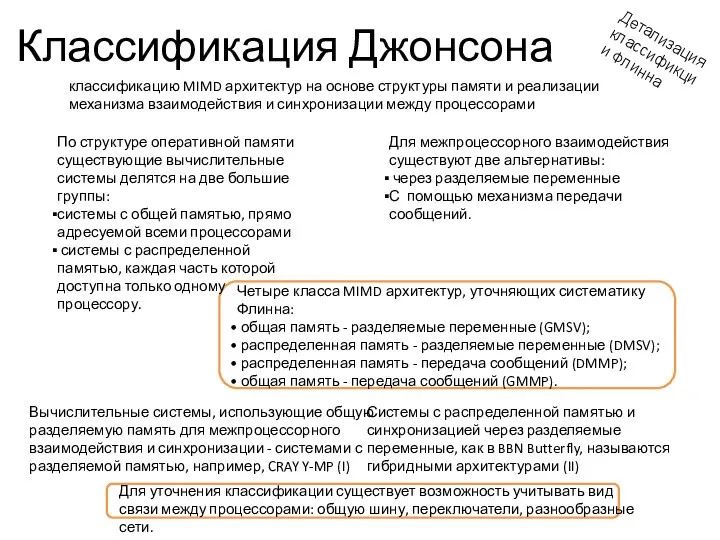

Классификация Джонсона

классификацию MIMD архитектур на основе структуры памяти и реализации механизма

Классификация Джонсона

классификацию MIMD архитектур на основе структуры памяти и реализации механизма

Детализация классификции Флинна

По структуре оперативной памяти существующие вычислительные системы делятся на две большие группы:

системы с общей памятью, прямо адресуемой всеми процессорами

системы с распределенной памятью, каждая часть которой доступна только одному процессору.

Для межпроцессорного взаимодействия существуют две альтернативы:

через разделяемые переменные

С помощью механизма передачи сообщений.

Четыре класса MIMD архитектур, уточняющих систематику Флинна:

общая память - разделяемые переменные (GMSV);

распределенная память - разделяемые переменные (DMSV);

распределенная память - передача сообщений (DMMP);

общая память - передача сообщений (GMMP).

Вычислительные системы, использующие общую разделяемую память для межпроцессорного взаимодействия и синхронизации - системами с разделяемой памятью, например, CRAY Y-MP (I)

Системы с распределенной памятью и синхронизацией через разделяемые переменные, как в BBN Butterfly, называются гибридными архитектурами (II)

Для уточнения классификации существует возможность учитывать вид связи между процессорами: общую шину, переключатели, разнообразные сети.

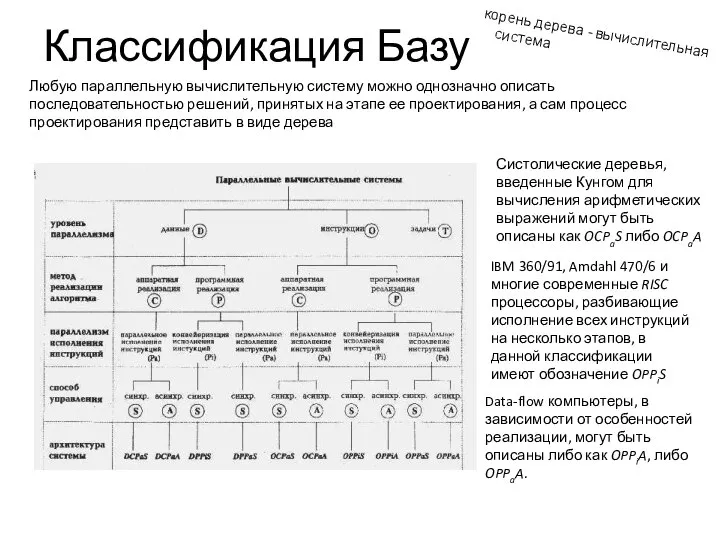

Классификация Базу

Любую параллельную вычислительную систему можно однозначно описать последовательностью решений, принятых

Классификация Базу

Любую параллельную вычислительную систему можно однозначно описать последовательностью решений, принятых

корень дерева - вычислительная

система

Систолические деревья, введенные Кунгом для вычисления арифметических выражений могут быть описаны как OCPaS либо OCPaA

IBM 360/91, Amdahl 470/6 и многие современные RISC процессоры, разбивающие исполнение всех инструкций на несколько этапов, в данной классификации имеют обозначение OPPiS

Data-flow компьютеры, в зависимости от особенностей реализации, могут быть описаны либо как OPPiA, либо OPPaA.

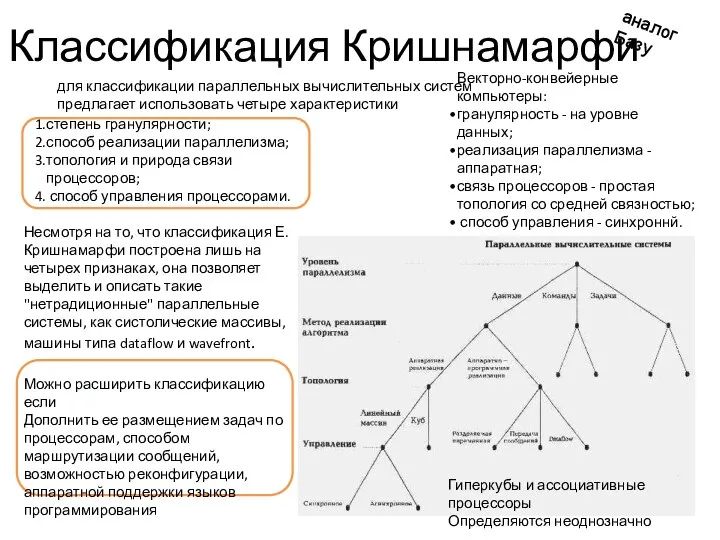

Классификация Кришнамарфи

аналог Базу

для классификации параллельных вычислительных систем предлагает использовать четыре характеристики

Классификация Кришнамарфи

аналог Базу

для классификации параллельных вычислительных систем предлагает использовать четыре характеристики

степень гранулярности;

способ реализации параллелизма;

топология и природа связи процессоров;

способ управления процессорами.

Гиперкубы и ассоциативные процессоры

Определяются неоднозначно

Векторно-конвейерные компьютеры:

гранулярность - на уровне данных;

реализация параллелизма - аппаратная;

связь процессоров - простая топология со средней связностью;

способ управления - синхроннй.

Несмотря на то, что классификация Е. Кришнамарфи построена лишь на четырех признаках, она позволяет выделить и описать такие "нетрадиционные" параллельные системы, как систолические массивы, машины типа dataflow и wavefront.

Можно расширить классификацию если

Дополнить ее размещением задач по процессорам, способом маршрутизации сообщений, возможностью реконфигурации, аппаратной поддержки языков программирования

Классификация Скилликорна

очередная попытка расширить классификацию Флинна

Классификация состоит из двух уровней. На

Классификация Скилликорна

очередная попытка расширить классификацию Флинна

Классификация состоит из двух уровней. На

тип переключателя между DP и DM;

количество процессоров команд (IP);

число запоминающих устройств (модулей памяти) команд (IM);

тип переключателя между IP и IM;

количество процессоров данных (DP);

число запоминающих устройств (модулей памяти) данных (DM);

тип переключателя между IP и DP;

тип переключателя между DP и DP.

На втором уровне классификации Д.Скилликорн просто уточняет описание, сделанное на первом уровне, добавляя возможность конвейерной обработки в процессорах команд и данных.

Рассмотрим компьютер Connection Machine 2

его можно описать как:

(1, 1, 1-1, n, n, n-n, 1-n, nxn)

Основа - абстрактная структура , состоящая из четырех компонент :

·процессор команд (IP) - интерипретатор команд

·процессор данных (DP) - преобразователь данных, в соответствии с арифметическими операциями;

·иерархия памяти (IM,DM) - запоминающее устройство

·переключатель - связь между процессорами и памятью.

Классификация Дазгупты

последние исследования по классификации

Модифиация метода Скилликорна

Назовем классом классификационной схемы именованную

Классификация Дазгупты

последние исследования по классификации

Модифиация метода Скилликорна

Назовем классом классификационной схемы именованную

Предлагается следующая иерархия категорий:

Самый низкий уровень - категория КЭШ-процессора с памятью MCP (memory-cache processor).

Классами этой категории являются всевозможные различные архитектуры. Соответствующую архитектуре формулу можно рассматривать как имя класса.

2.Более высокий уровень - категория КЭШ-процессора (СP). Множество классов этой категории получается путем удаления из классов категории CP составляющих, описывающих память.

3.Самый высокий уровень - категория процессора (P). Классы получают удалением кэш-составляющих из классов категории CP.

Базовые элементы архитектуры:

iM - память с расслоением - память, из которой можно выбрать несколько единиц информации за один цикл памяти;

sM - простая память - память, из которой можно выбрать единицу информации за цикл памяти;

C - программируемая или непрограммируемая кэш-память. Буферные регистры, подобные регистрам CRAY-1, также описываются, как кэш-память;

sI - простой (неконвейерный) процессор для подготовки команды к исполнению;

pI - конвейерный процессор для подготовки команды к исполнению;

sX - простой процессор для исполнения команды;

pX - конвейерный процессор для исполнения команды.

Классификация Дункана

Систематика очень простая: процессоры системы работают либо синхронно, либо независимо

Классификация Дункана

Систематика очень простая: процессоры системы работают либо синхронно, либо независимо

Параллельная архитектура - это такой способ организации вычислительной системы, при котором допускается, чтобы множество процессоров (простых или сложных) могло бы работать одновременно, взаимодействуя по мере надобности друг с другом.

Требование Дункана - не рассматривать компьютеры, использующие только параллелизм низкого уровня, наравне со всеми остальными, т.к., во-первых, практически все существующие системы будут классифицированны как "параллельные" (что заведомо не будет позитивным фактором для классификации), и, во-вторых, такие машины будут плохо вписываться в любую модель или концепцию, отражающую параллелизм высокого уровня.

Включает все

Инструментарий веб-студии: от брифа до презентации Балахтин Кирилл Руководитель отдела по работе с клиентами Интерактивное аген

Инструментарий веб-студии: от брифа до презентации Балахтин Кирилл Руководитель отдела по работе с клиентами Интерактивное аген Обобщения знаний о частях речи 3 класс - презентация для начальной школы_____________________________________________________________________________________________________________

Обобщения знаний о частях речи 3 класс - презентация для начальной школы_____________________________________________________________________________________________________________ Physical education communication

Physical education communication Визитная карточка

Визитная карточка Концепция предвыборного плаката партии КПРФ

Концепция предвыборного плаката партии КПРФ Бізнес-план кафе "White&black"

Бізнес-план кафе "White&black" НАША МОСКВА - презентация для начальной школы_

НАША МОСКВА - презентация для начальной школы_ Формы трудовой деятельности

Формы трудовой деятельности  02Извещение о НС

02Извещение о НС Портфолио дисциплины

Портфолио дисциплины Презентация____

Презентация____ Нелинейная оптика

Нелинейная оптика  Строительство здания производственного назначения

Строительство здания производственного назначения Язык и речь

Язык и речь Дозиметрические единицы и защита от радиоактивных излучений.

Дозиметрические единицы и защита от радиоактивных излучений. Источники финансирования инвестиций

Источники финансирования инвестиций Воспаление. ГЕМАТОЛОГИЧЕСКИЙ ССИНДРОМ ОТВЕТ ОСТРОЙ ФАЗЫ ЛИХОРАДКА

Воспаление. ГЕМАТОЛОГИЧЕСКИЙ ССИНДРОМ ОТВЕТ ОСТРОЙ ФАЗЫ ЛИХОРАДКА презентация коррупция

презентация коррупция Строение и функции нервной системы человека Подготовила Ученицы 9-в класса Горловского УВК №22 Оклей Виктория

Строение и функции нервной системы человека Подготовила Ученицы 9-в класса Горловского УВК №22 Оклей Виктория Архитектурно-планировочные приемы при реконструкции жилых зданий

Архитектурно-планировочные приемы при реконструкции жилых зданий Дифференциальная диагностика нарушений ритма сердца

Дифференциальная диагностика нарушений ритма сердца  Принцип черного ящика

Принцип черного ящика Тема: «Порядок прекращения деятельности юридических лиц» Выполнил: Студент 2-го курса Группа Юб 03/1303 Якушенко Игорь

Тема: «Порядок прекращения деятельности юридических лиц» Выполнил: Студент 2-го курса Группа Юб 03/1303 Якушенко Игорь  франция мәдениеті

франция мәдениеті Теоретические распределения в анализе вариационных рядов

Теоретические распределения в анализе вариационных рядов становление туризма в СССР

становление туризма в СССР  Магнезиальные вяжущие

Магнезиальные вяжущие Волоконно-оптические линии связи. Основные характеристики электромагнитного поля и среды его распространения.

Волоконно-оптические линии связи. Основные характеристики электромагнитного поля и среды его распространения.