Содержание

- 2. Механизм процессов и концепция сигнала В VHDL При программировании на VHDL нужно учитывать две особенности: моделирование

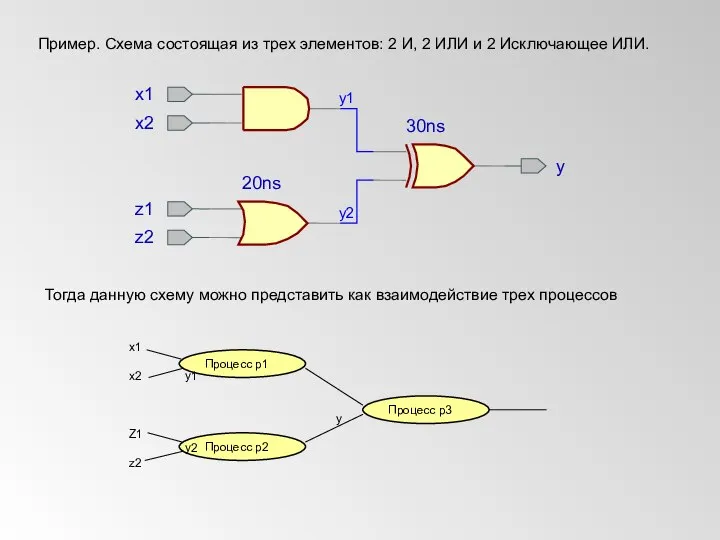

- 3. Пример. Схема состоящая из трех элементов: 2 И, 2 ИЛИ и 2 Исключающее ИЛИ. Тогда данную

- 4. Процессы p1,p2,p3 описываются в VHDL следующим образом: P1: process (x1,x2) begin . . . функционирование элемента

- 5. В VHDL есть два типа сигналов: ports - порты - это внешние входы и выходы ОП:

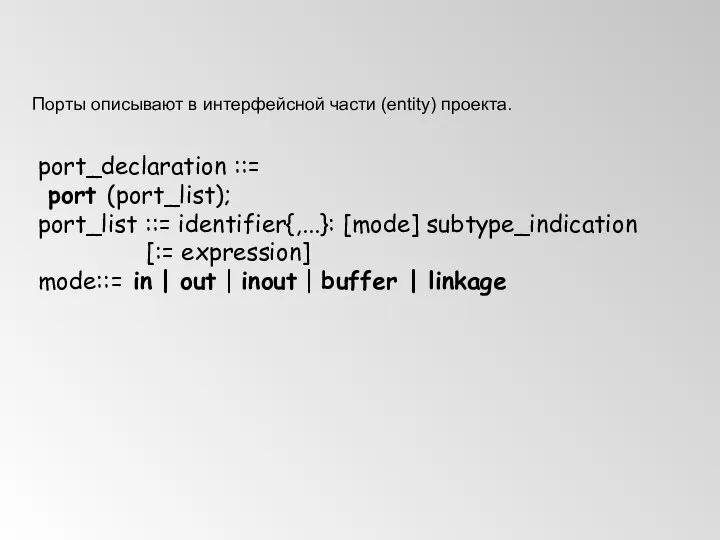

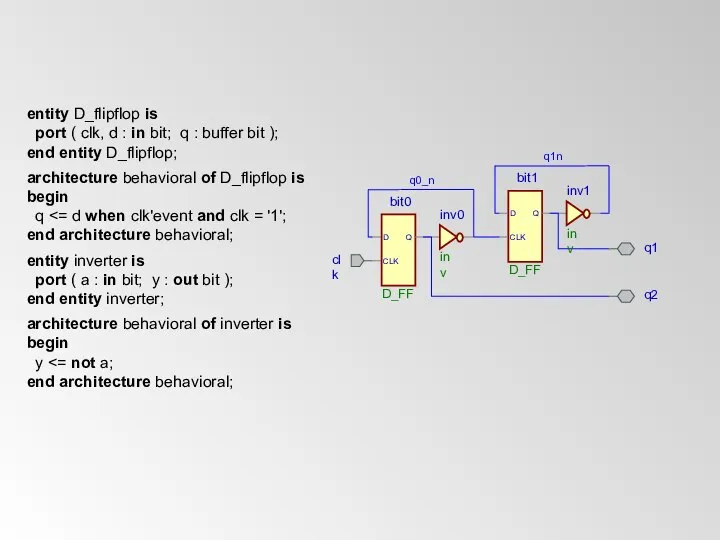

- 6. Порты описывают в интерфейсной части (entity) проекта. port_declaration ::= port (port_list); port_list ::= identifier{,...}: [mode] subtype_indication

- 8. Декларация внутреннего сигнала signal_declaration ::= signal identifier{,...}: subtype_indication [:= expression] architecture arch_name of entity_name is {

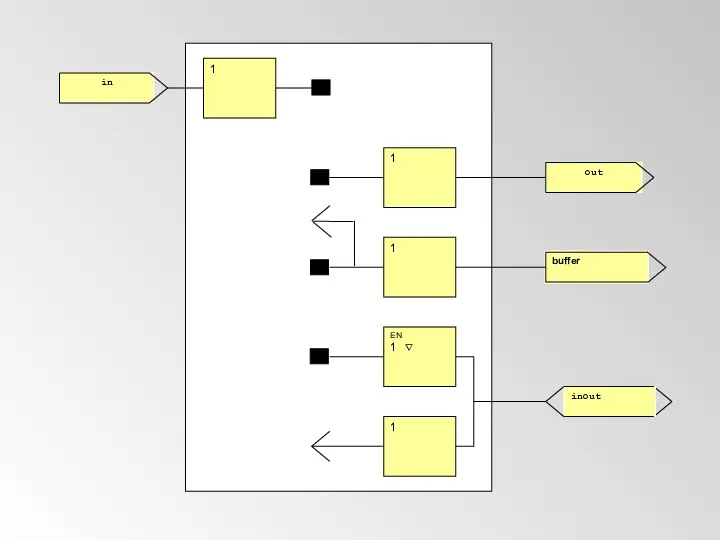

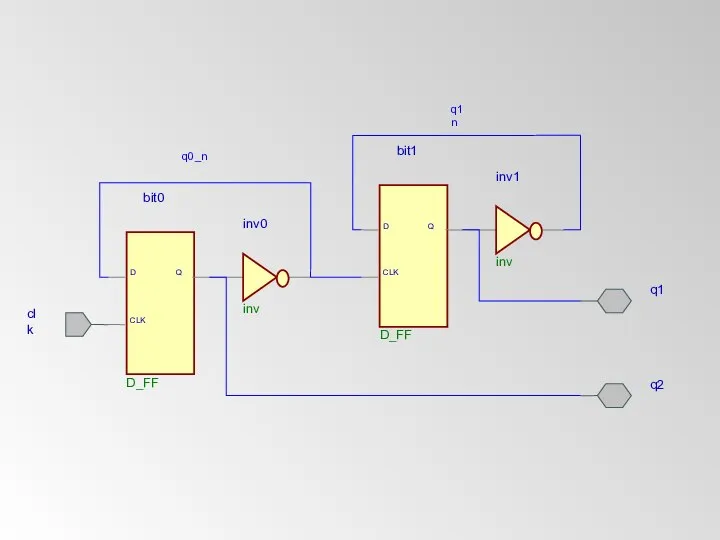

- 10. entity D_flipflop is port ( clk, d : in bit; q : buffer bit ); end

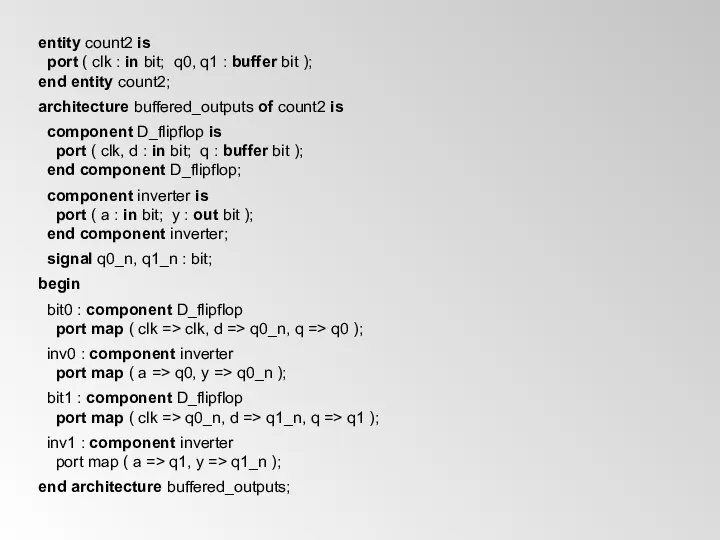

- 11. entity count2 is port ( clk : in bit; q0, q1 : buffer bit ); end

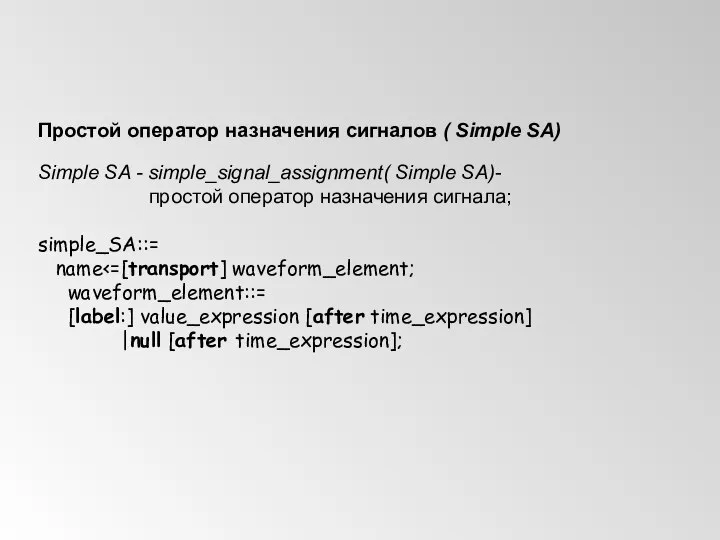

- 12. Простой оператор назначения сигналов ( Simple SA) Simple SA - simple_signal_assignment( Simple SA)- простой оператор назначения

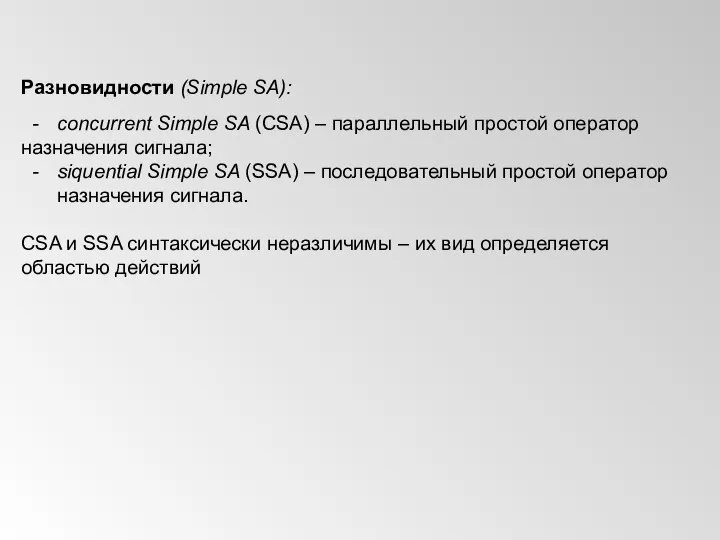

- 13. Разновидности (Simple SA): - concurrent Simple SA (CSA) – параллельный простой оператор назначения сигнала; - siquential

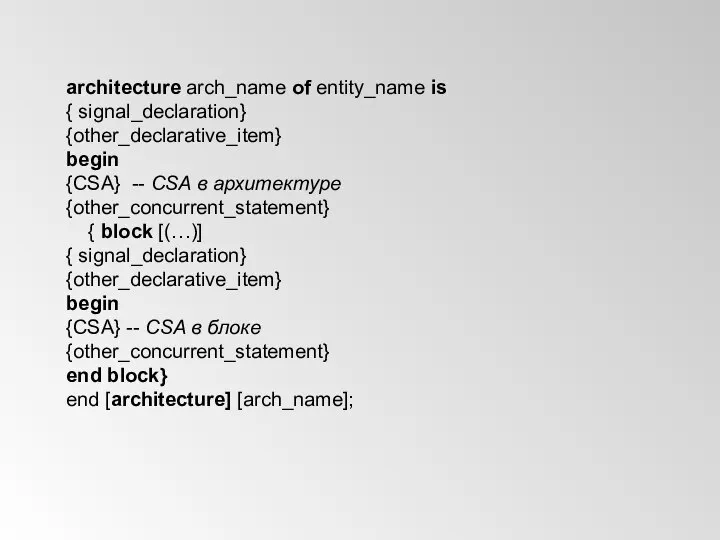

- 14. Область действий CSA: - архитектура - блок

- 15. architecture arch_name of entity_name is { signal_declaration} {other_declarative_item} begin {CSA} -- CSA в архитектуре {other_concurrent_statement} {

- 16. Область действий SSA: - процесс - процедура - функция

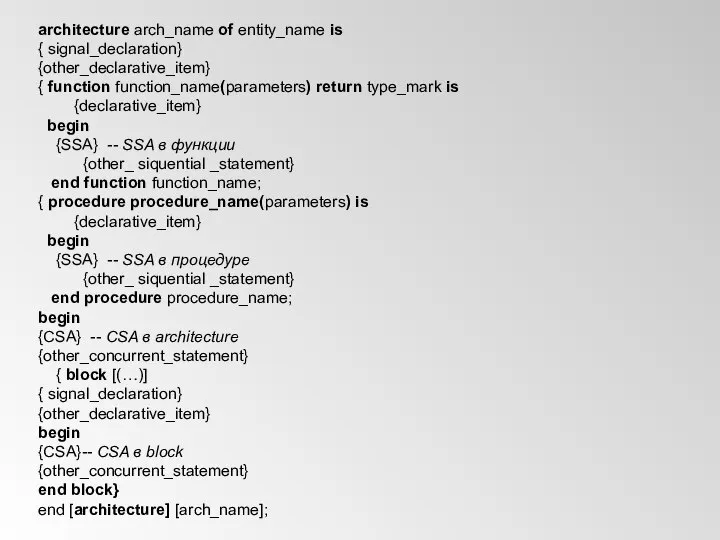

- 17. architecture arch_name of entity_name is { signal_declaration} {other_declarative_item} { function function_name(parameters) return type_mark is {declarative_item} begin

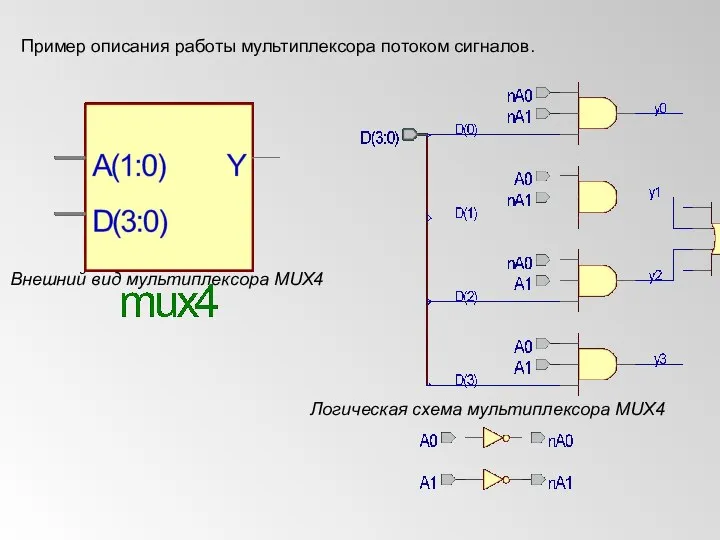

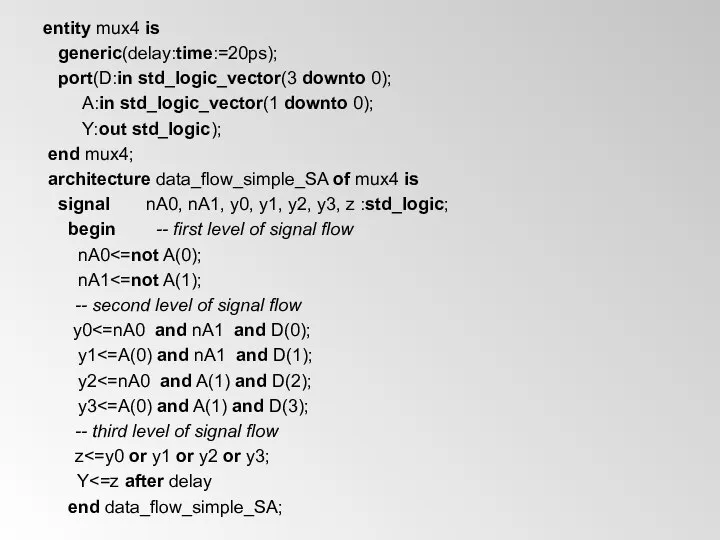

- 18. Пример описания работы мультиплексора потоком сигналов. Внешний вид мультиплексора MUX4 Логическая схема мультиплексора MUX4

- 19. entity mux4 is generic(delay:time:=20ps); port(D:in std_logic_vector(3 downto 0); A:in std_logic_vector(1 downto 0); Y:out std_logic); end mux4;

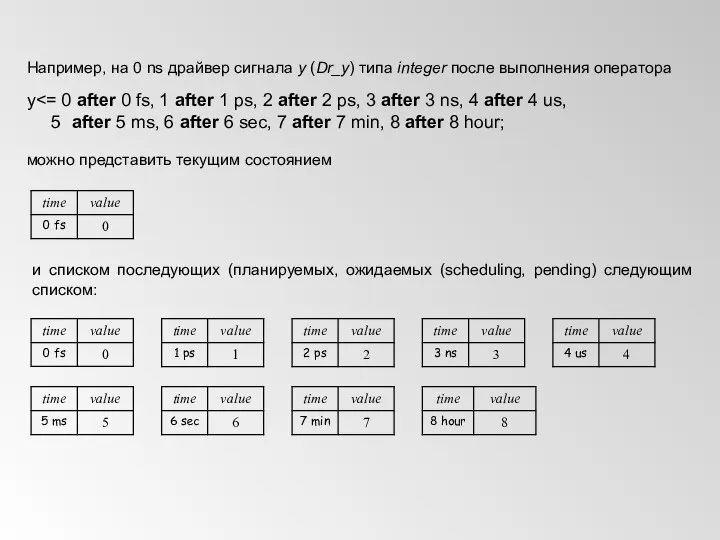

- 20. Драйвер сигнала Каждый сигнал имеет один или несколько так называемых драйверов. Драйвер содержит текущее значение сигнала

- 21. Например, на 0 ns драйвер сигнала y (Dr_y) типа integer после выполнения оператора y 5 after

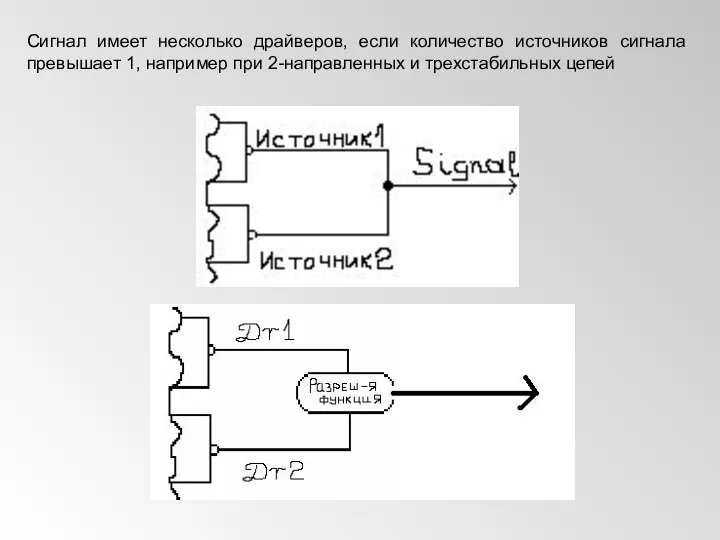

- 22. Сигнал имеет несколько драйверов, если количество источников сигнала превышает 1, например при 2-направленных и трехстабильных цепей

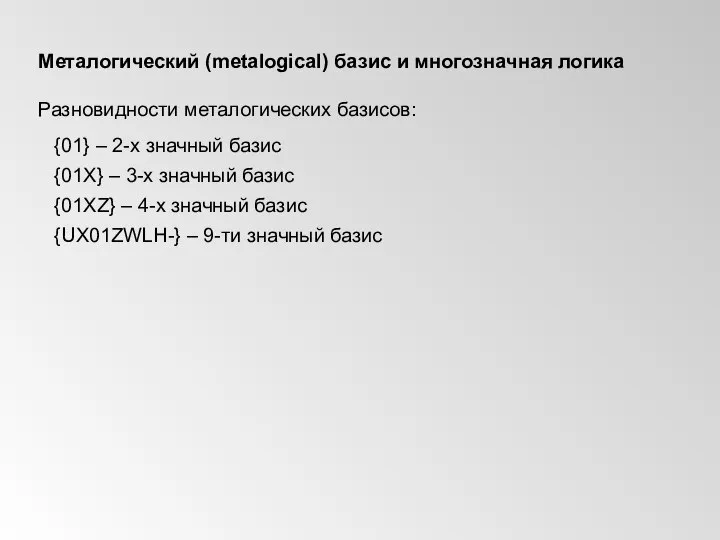

- 23. Металогический (metalogical) базис и многозначная логика Разновидности металогических базисов: {01} – 2-х значный базис {01Х} –

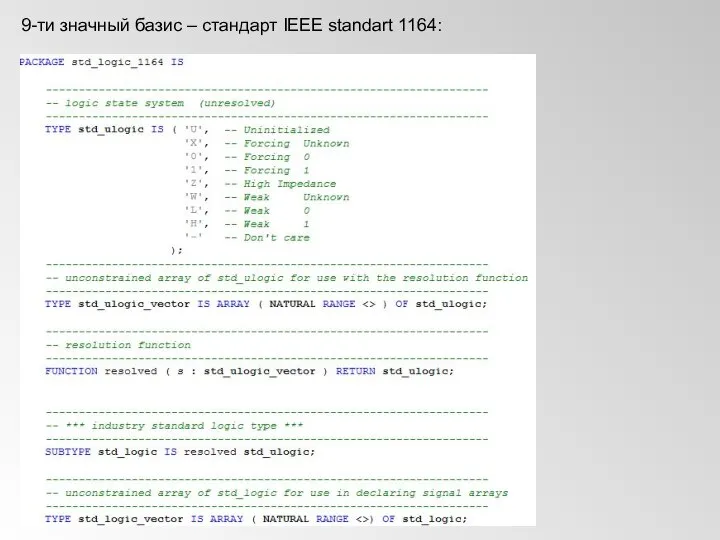

- 24. 9-ти значный базис – стандарт IEEE standart 1164:

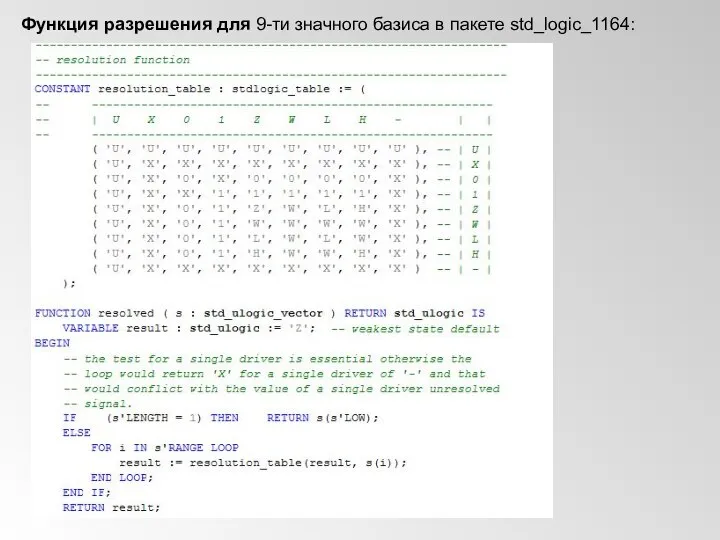

- 25. Функция разрешения для 9-ти значного базиса в пакете std_logic_1164:

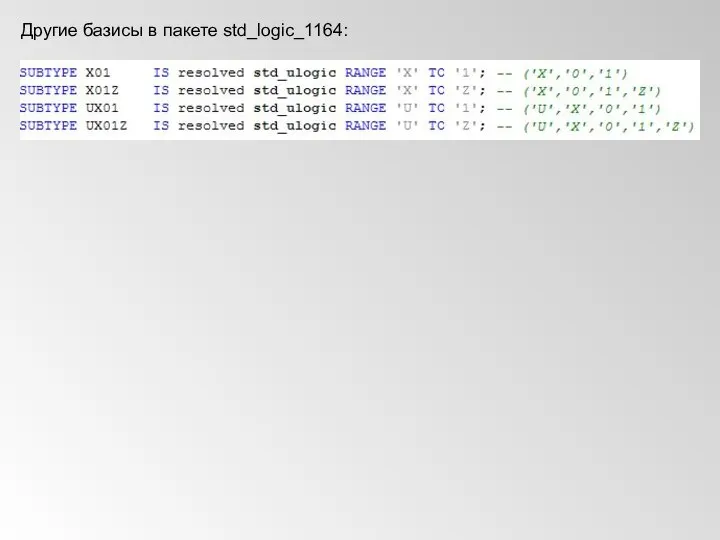

- 26. Другие базисы в пакете std_logic_1164:

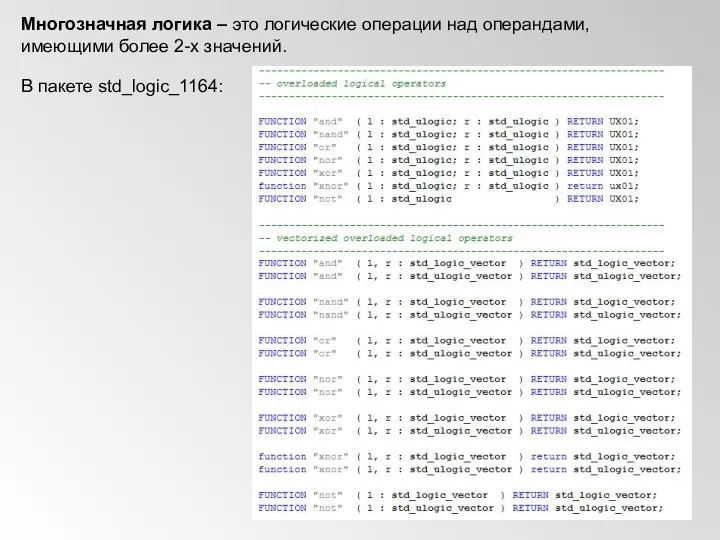

- 27. Многозначная логика – это логические операции над операндами, имеющими более 2-х значений. В пакете std_logic_1164:

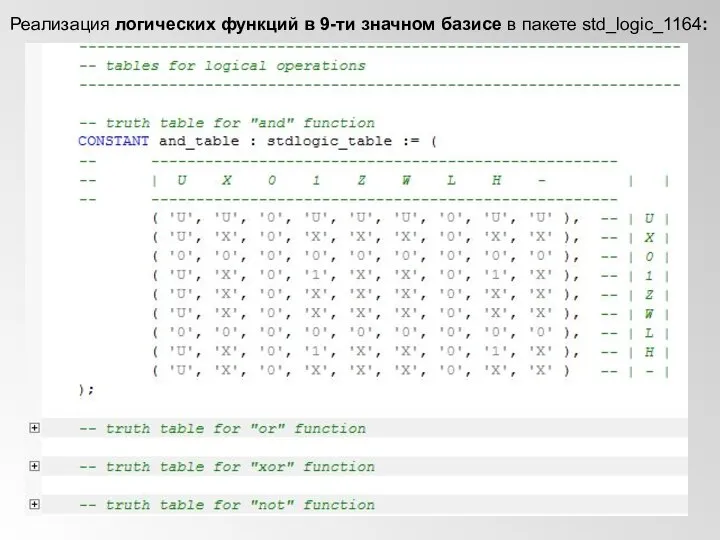

- 28. Реализация логических функций в 9-ти значном базисе в пакете std_logic_1164:

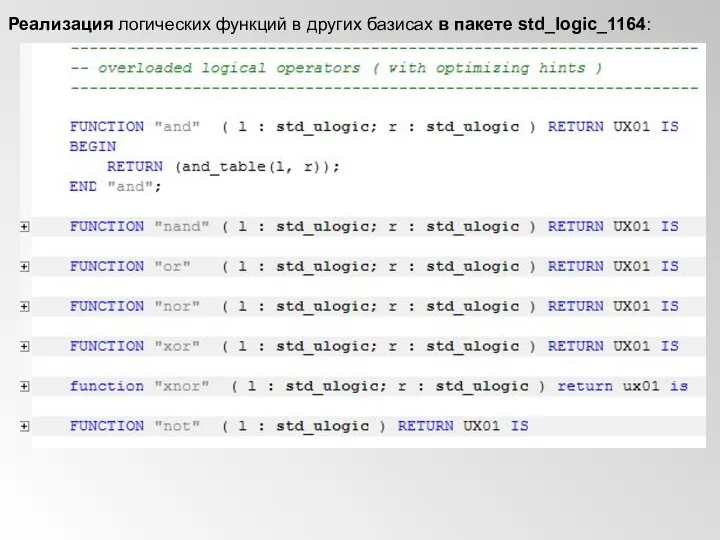

- 29. Реализация логических функций в других базисах в пакете std_logic_1164:

- 30. Моделирование задержек сигналов Простой оператор назначения сигналов simple_SA::= [Label:] signal_name waveform ::= {transaction} {,transaction} transaction::= value_expression

- 31. Разновидности задержек сигналов: - transport - транспортная - inertial - инерционная - reject inertial – инерционная

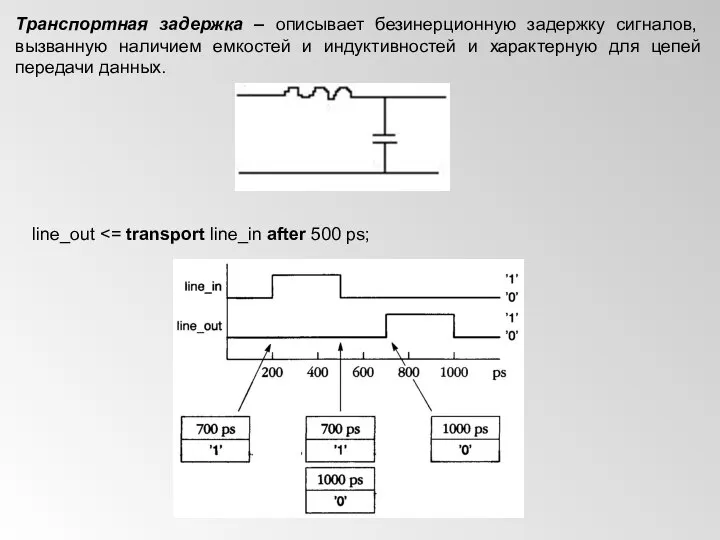

- 32. Транспортная задержка – описывает безинерционную задержку сигналов, вызванную наличием емкостей и индуктивностей и характерную для цепей

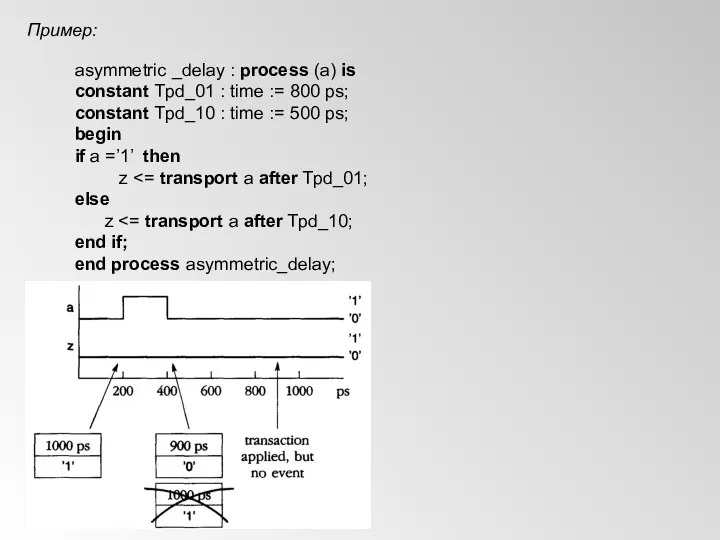

- 33. Пример: asymmetric _delay : process (a) is constant Tpd_01 : time := 800 ps; constant Tpd_10

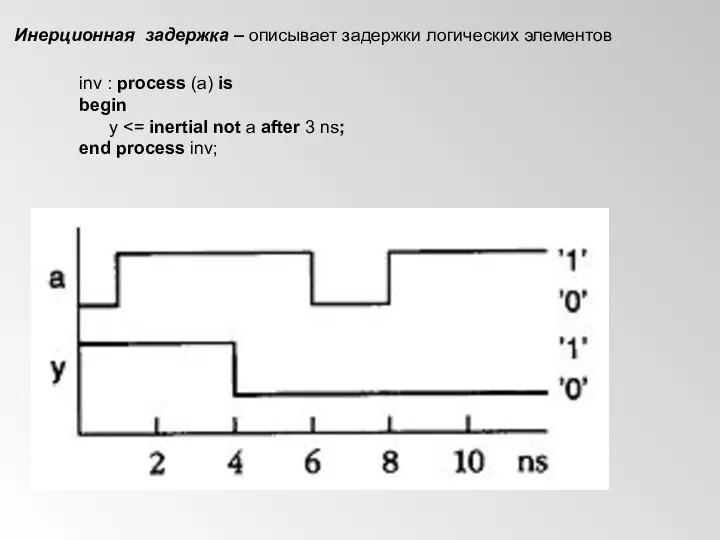

- 34. Инерционная задержка – описывает задержки логических элементов inv : process (a) is begin y end process

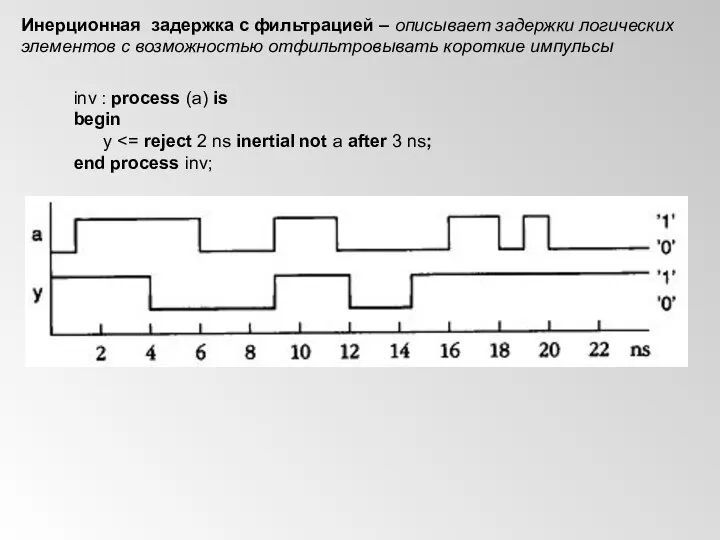

- 35. Инерционная задержка с фильтрацией – описывает задержки логических элементов с возможностью отфильтровывать короткие импульсы inv :

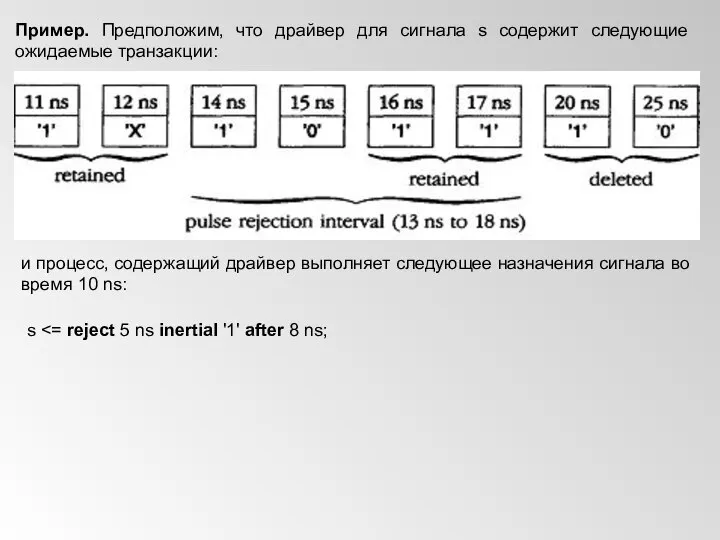

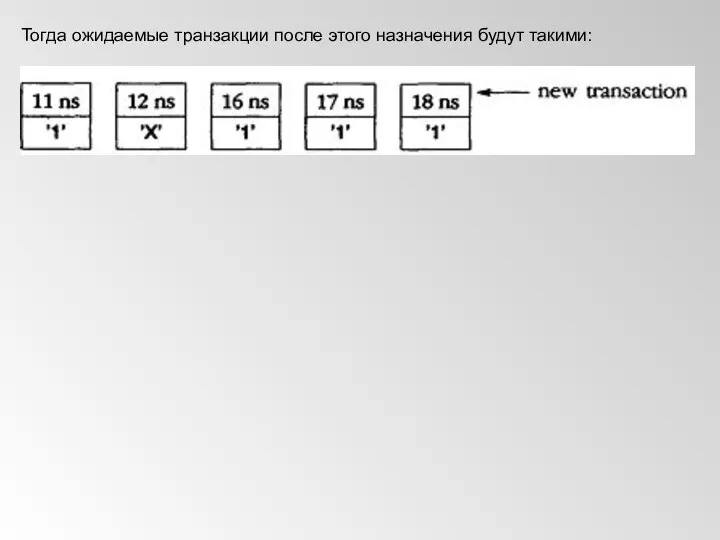

- 36. Пример. Предположим, что драйвер для сигнала s содержит следующие ожидаемые транзакции: и процесс, содержащий драйвер выполняет

- 37. Тогда ожидаемые транзакции после этого назначения будут такими:

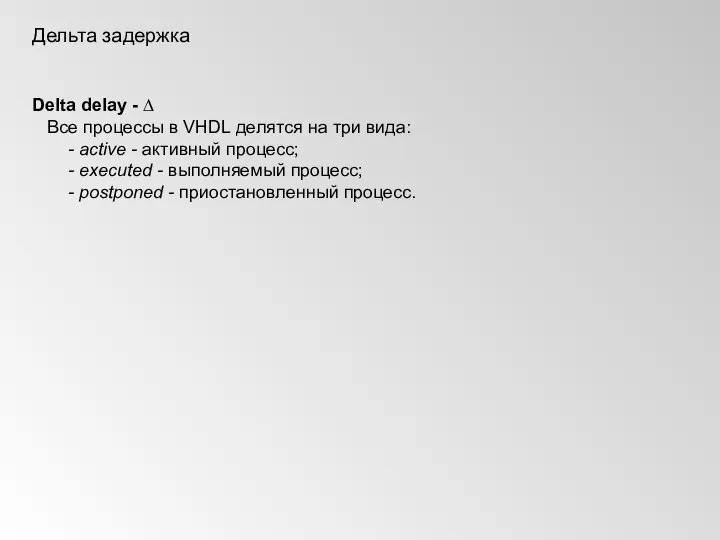

- 38. Дельта задержка Delta delay - ∆ Все процессы в VHDL делятся на три вида: - active

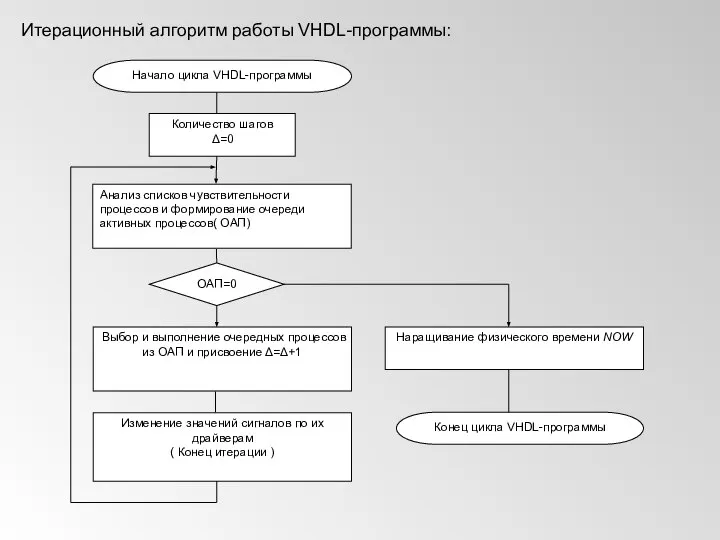

- 39. Итерационный алгоритм работы VHDL-программы:

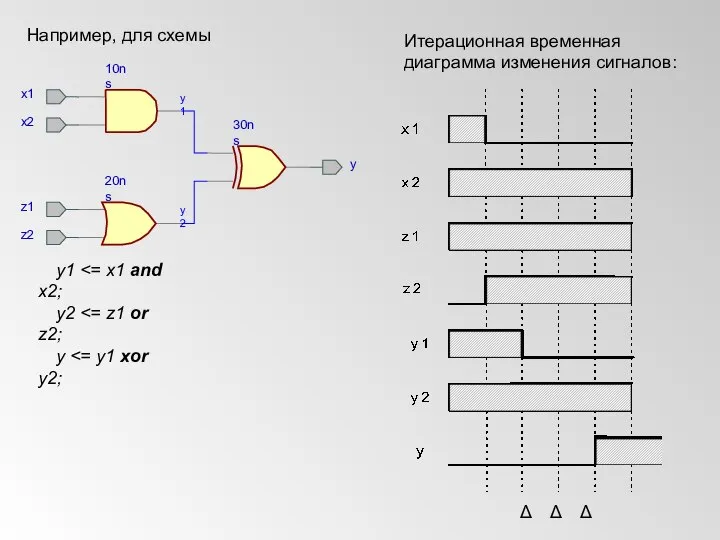

- 40. Например, для схемы y1 y2 y Итерационная временная диаграмма изменения сигналов: Δ Δ Δ

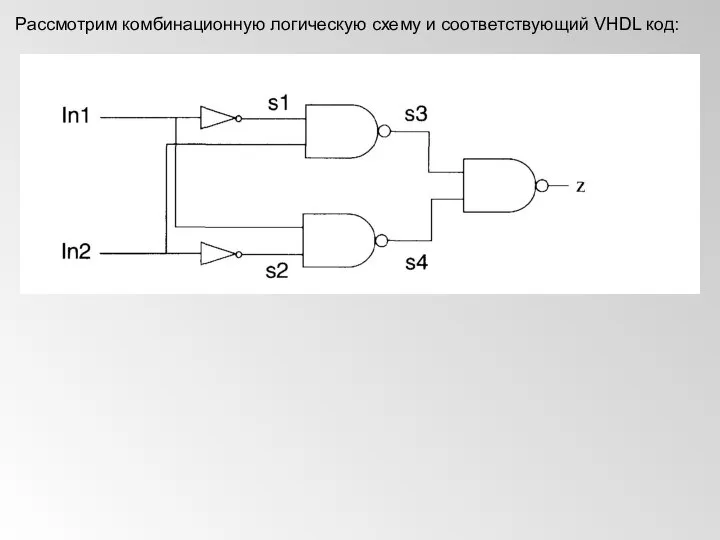

- 41. Рассмотрим комбинационную логическую схему и соответствующий VHDL код:

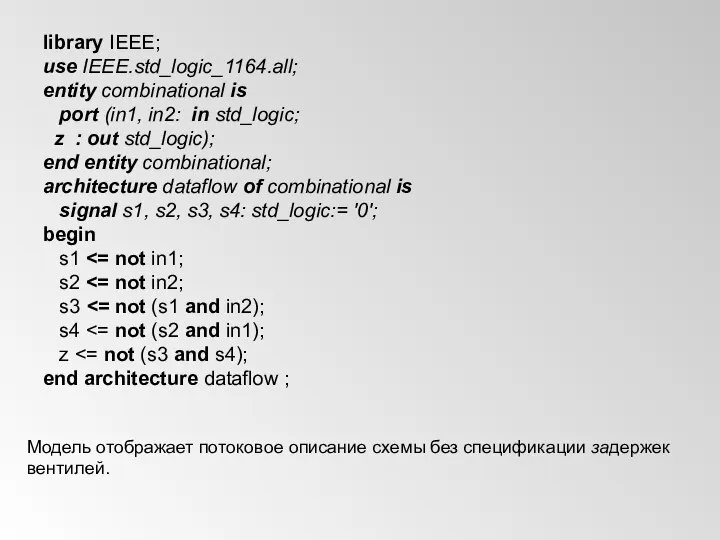

- 42. library IEEE; use IEEE.std_logic_1164.all; entity combinational is port (in1, in2: in std_logic; z : out std_logic);

- 43. Результаты моделирования комбинационной схемы

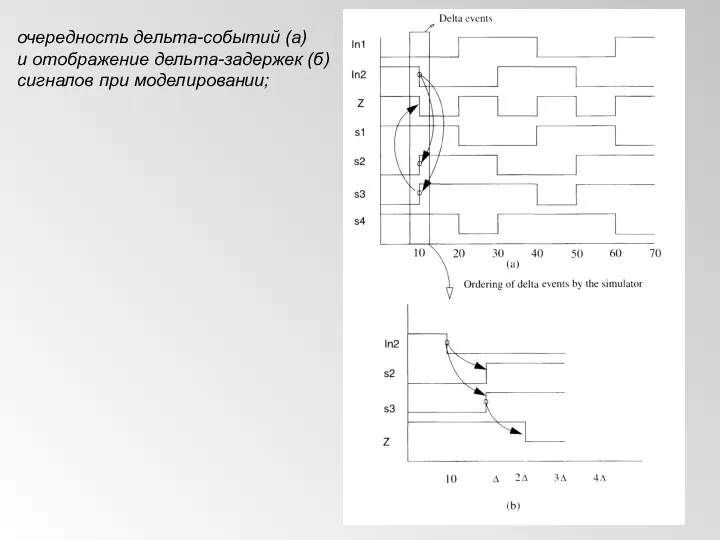

- 44. очередность дельта-событий (a) и отображение дельта-задержек (б) сигналов при моделировании;

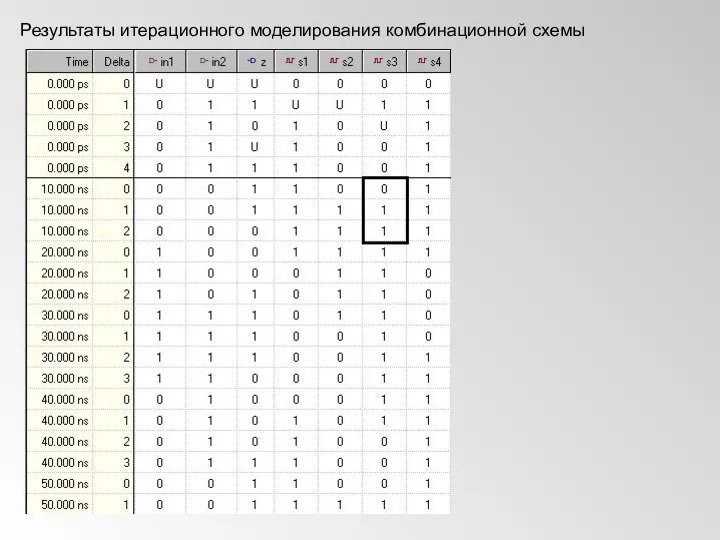

- 45. Результаты итерационного моделирования комбинационной схемы

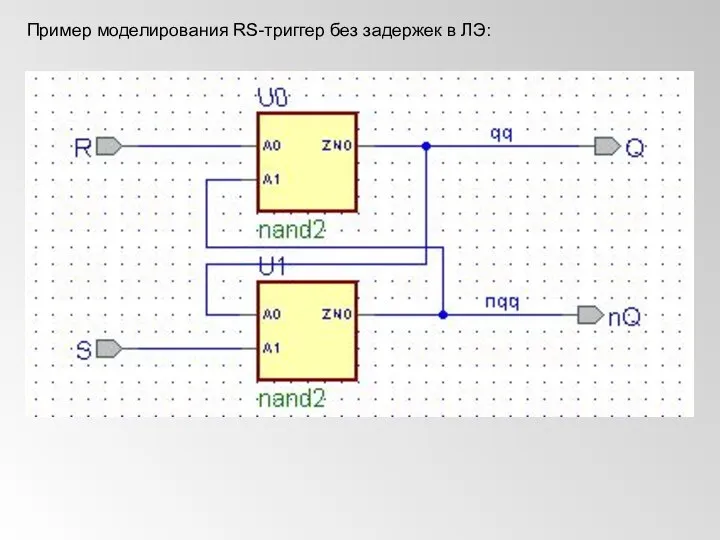

- 46. Пример моделирования RS-триггер без задержек в ЛЭ:

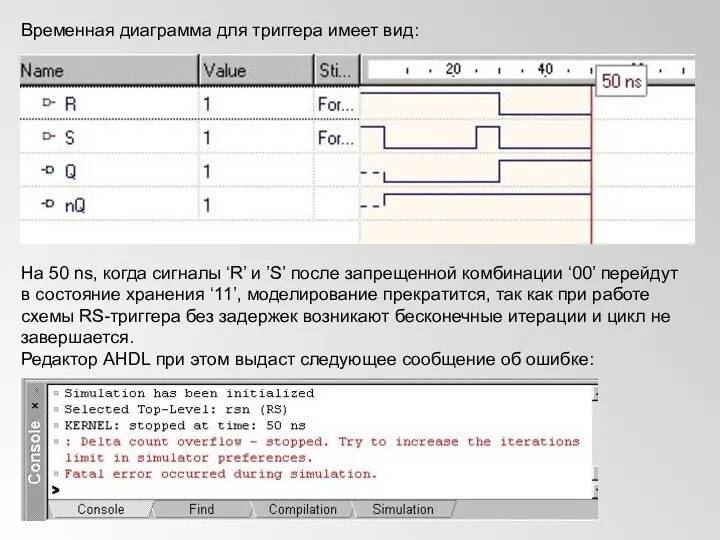

- 47. Временная диаграмма для триггера имеет вид: На 50 ns, когда сигналы ‘R’ и ’S’ после запрещенной

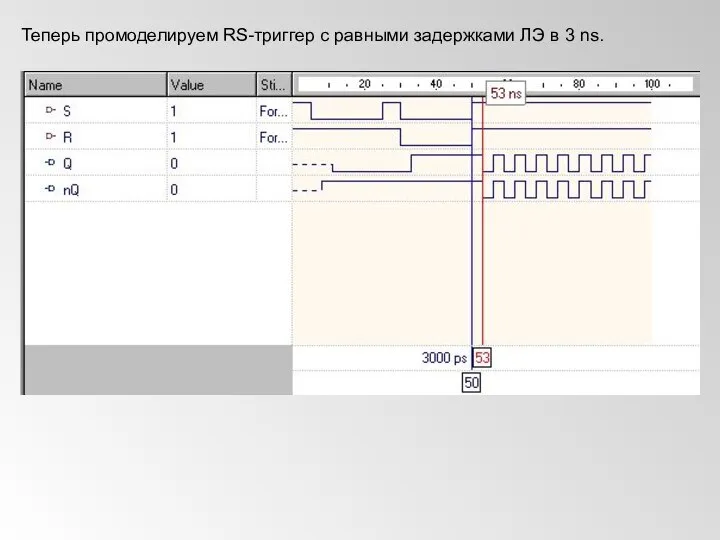

- 48. Теперь промоделируем RS-триггер с равными задержками ЛЭ в 3 ns.

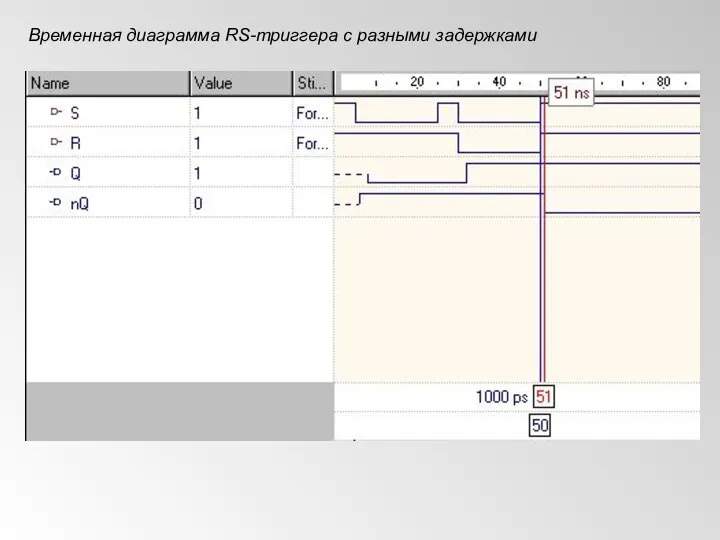

- 49. Временная диаграмма RS-триггера с разными задержками

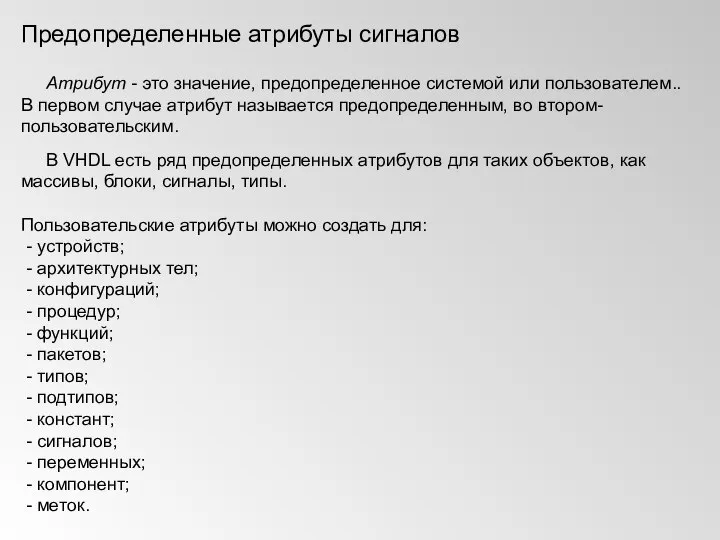

- 50. Предопределенные атрибуты сигналов Атрибут - это значение, предопределенное системой или пользователем.. В первом случае атрибут называется

- 51. attribute ::= prefix’ attribute_name[( expression )]

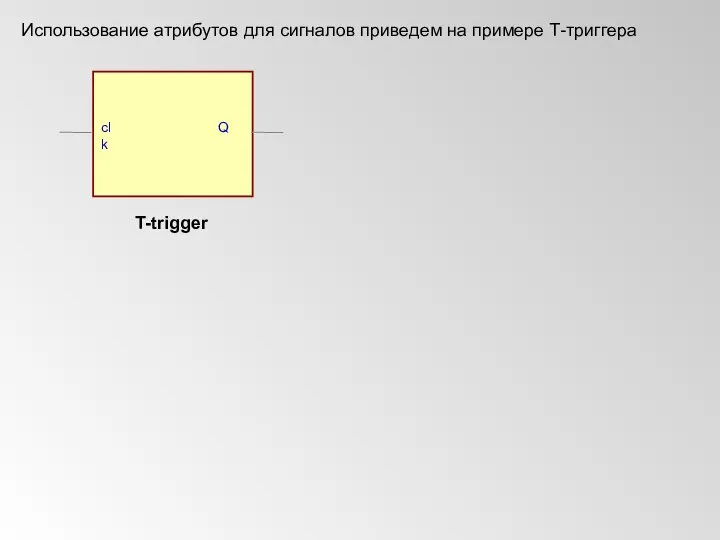

- 52. Использование атрибутов для сигналов приведем на примере Т-триггера T-trigger

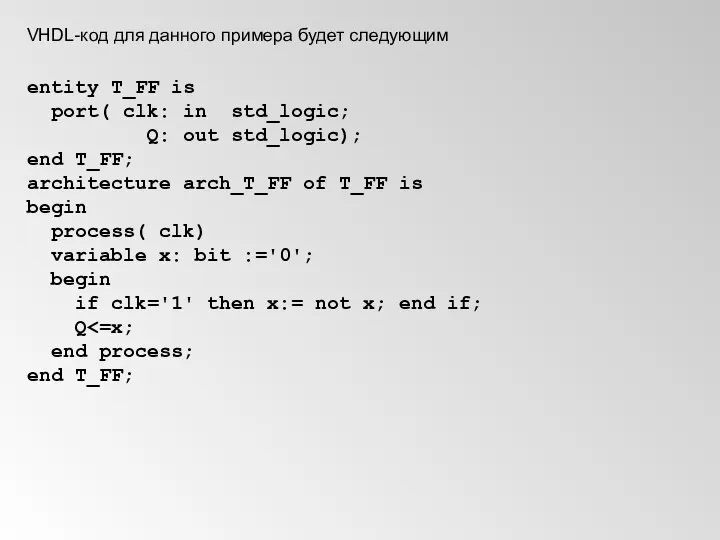

- 53. VHDL-код для данного примера будет следующим entity T_FF is port( clk: in std_logic; Q: out std_logic);

- 55. Скачать презентацию

![Декларация внутреннего сигнала signal_declaration ::= signal identifier{,...}: subtype_indication [:= expression] architecture](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1374405/slide-7.jpg)

![Моделирование задержек сигналов Простой оператор назначения сигналов simple_SA::= [Label:] signal_name waveform](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1374405/slide-29.jpg)

![attribute ::= prefix’ attribute_name[( expression )]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1374405/slide-50.jpg)

Маркетинг в социально-культурной сфере

Маркетинг в социально-культурной сфере Основы программирования в среде Visual Basic for Application (VBA)

Основы программирования в среде Visual Basic for Application (VBA) 30-й юбилейный форум электротехники и систем безопасности. ТМК «Гринн»,17 октября 2019 г. г. Орел

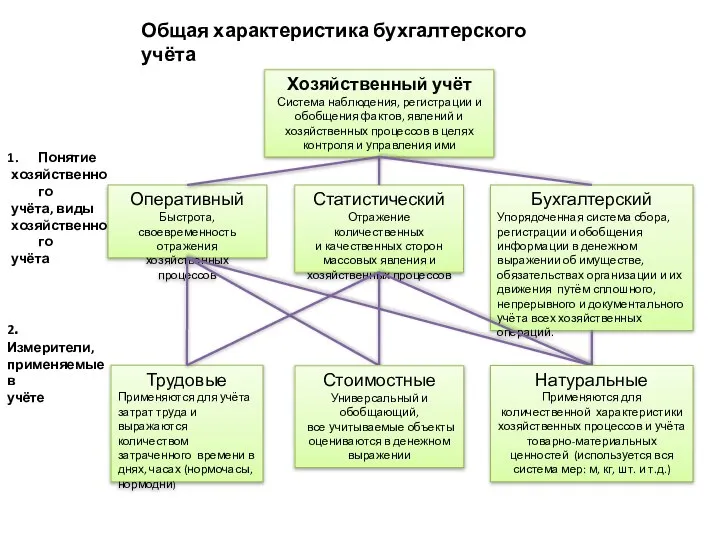

30-й юбилейный форум электротехники и систем безопасности. ТМК «Гринн»,17 октября 2019 г. г. Орел Характеристика бухгалтерского учета

Характеристика бухгалтерского учета  Исторический жанр, тесты для 7 класса, по программе Б. Неменского

Исторический жанр, тесты для 7 класса, по программе Б. Неменского Задания по курсу Теория организации и организационное поведение «Анализ деятельности региональной компании»

Задания по курсу Теория организации и организационное поведение «Анализ деятельности региональной компании» Современные методы и техники «выведывания» информации

Современные методы и техники «выведывания» информации Графика конструирование программ и языки программирования

Графика конструирование программ и языки программирования Фильтрация информационных сигналов. Современные модели помехоподавляющих фильтров, их основные характеристики и возможности

Фильтрация информационных сигналов. Современные модели помехоподавляющих фильтров, их основные характеристики и возможности Презентация Классификация стран мира(методические подходы и критерии)

Презентация Классификация стран мира(методические подходы и критерии) Физиологическая характеристика двигательных качеств

Физиологическая характеристика двигательных качеств Мировой океан как среда обитания Kothla-Järve Tammiku Gümaasium Kostja : Pavelkovitš Oksana 8 klass

Мировой океан как среда обитания Kothla-Järve Tammiku Gümaasium Kostja : Pavelkovitš Oksana 8 klass Обществознание. Программа «11 класс»

Обществознание. Программа «11 класс» ПРЯМОУГОЛЬНИК И КВАДРАТ Андрианова Н.Н., учитель начальных классов МОУ СОШ №12 г.Балашова Саратовской области

ПРЯМОУГОЛЬНИК И КВАДРАТ Андрианова Н.Н., учитель начальных классов МОУ СОШ №12 г.Балашова Саратовской области Презентация Тест по философии

Презентация Тест по философии Звонкова Мира Михайловна - старейший житель деревни Клещёво

Звонкова Мира Михайловна - старейший житель деревни Клещёво ФОРМИРОВАНИЕ МОДЕЛИ ФУНКЦИОНИРОВАНИЯ ПРОГРАММНОГО СРЕДСТВА С ИСПОЛЬЗОВАНИЕМ UML

ФОРМИРОВАНИЕ МОДЕЛИ ФУНКЦИОНИРОВАНИЯ ПРОГРАММНОГО СРЕДСТВА С ИСПОЛЬЗОВАНИЕМ UML Художні напрями ХХ ст.

Художні напрями ХХ ст. Я познаю мир - презентация для начальной школы

Я познаю мир - презентация для начальной школы Презентация к уроку русского языка по теме «Однокоренные слова». «Путешествие в страну родственных слов» Подготовила учитель на

Презентация к уроку русского языка по теме «Однокоренные слова». «Путешествие в страну родственных слов» Подготовила учитель на Главное и важное

Главное и важное Координатная плоскость. Урок-лекция 6 класс.

Координатная плоскость. Урок-лекция 6 класс. Музейная педагогика в дошкольном образовании в свете Федеральных государственных требований Е. В. Францужан, методист НМЦ Невс

Музейная педагогика в дошкольном образовании в свете Федеральных государственных требований Е. В. Францужан, методист НМЦ Невс GUO DI LEATHER product collection. 广州国帝皮具有限公司

GUO DI LEATHER product collection. 广州国帝皮具有限公司 Avram Noam Chomsky

Avram Noam Chomsky Презентация по алгебре Системы двух линейных уравнений с двумя переменными

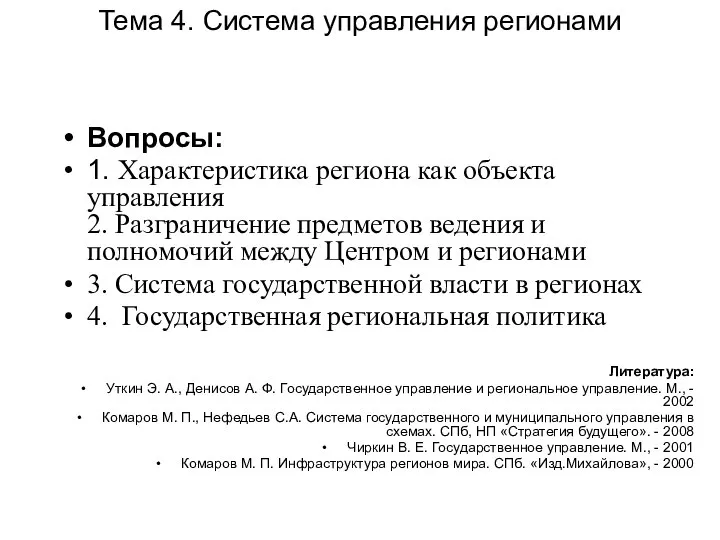

Презентация по алгебре Системы двух линейных уравнений с двумя переменными  Система управления регионами. (Тема 4)

Система управления регионами. (Тема 4) 0017328d-4c4c098f

0017328d-4c4c098f