Содержание

- 2. 7. МС и ШИМ 4) Вариант реализация скалярной ШИМ в МПСУ: Задать режимы работы МС и

- 3. где Т1, Т2, Т0, Т7 - время существования одноименных векторов. Векторы состояния: 000 − V0 и

- 4. Порядок распределения векторов (и их длительностей) на интервале усреднения Где ϕ' – угловое положение обобщенного вектора

- 5. Порядок распределения векторов (и их длительностей) на интервале усреднения на Ts располагается только один нулевой вектор

- 6. 6) Вариант реализация векторной ШИМ в МПСУ: Задать режимы работы МС и ШИМ. Задать период и

- 7. 7) ПЛМ МС и ШИМ: - COMCONx – регистр управления сравнения МнСА/В; - ACTRx – регистр

- 8. D15 – CENABLE – бит разрешение сравнения: = 0/1 ⇒ работа сравнения запрещена/разрешена. D14-D13 – CLD1,

- 9. D9 – FCMPOE – бит разрешения выходов МСиШИМ. Бит активен, когда EXTCONA(0)=0, иначе – резерв. В

- 10. 9) Регистр управления работой сравнения ACTRА Регистр управление работой сравнения ACTRA управляет действием, которое происходит на

- 11. D11, D10 - CMP6ACT1, CMP6ACT0 – бит воздействия на выходной вывод сравнения PWM6. =00 – форсированный

- 12. D15-D12 – резерв. D11-D8 – DBT3–DBT0 – биты определяют величину периода трех 4-битных таймеров МВ. Тмв=(0…15)Тпдч.

- 14. Скачать презентацию

7. МС и ШИМ

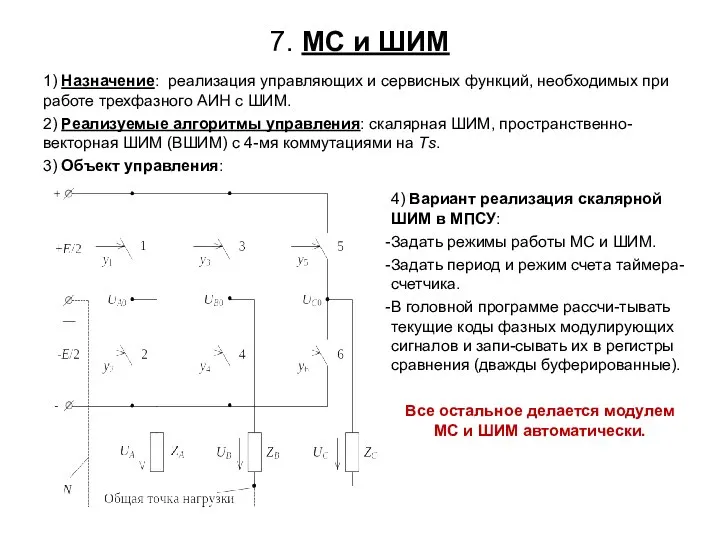

4) Вариант реализация скалярной ШИМ в МПСУ:

Задать режимы

7. МС и ШИМ

4) Вариант реализация скалярной ШИМ в МПСУ:

Задать режимы

Задать период и режим счета таймера-счетчика.

В головной программе рассчи-тывать текущие коды фазных модулирующих сигналов и запи-сывать их в регистры сравнения (дважды буферированные).

Все остальное делается модулем МС и ШИМ автоматически.

1) Назначение: реализация управляющих и сервисных функций, необходимых при работе трехфазного АИН с ШИМ.

2) Реализуемые алгоритмы управления: скалярная ШИМ, пространственно-векторная ШИМ (ВШИМ) с 4-мя коммутациями на Тs.

3) Объект управления:

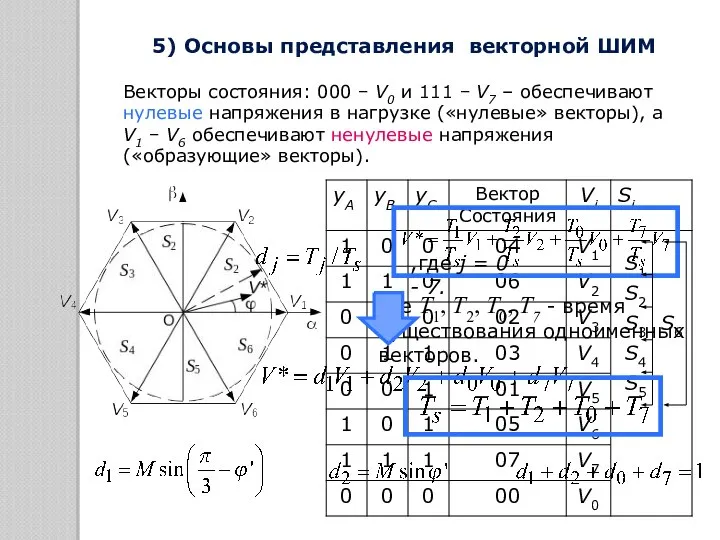

где Т1, Т2, Т0, Т7 - время существования одноименных векторов.

Векторы состояния:

где Т1, Т2, Т0, Т7 - время существования одноименных векторов.

Векторы состояния:

,где j = 0 - 7.

5) Основы представления векторной ШИМ

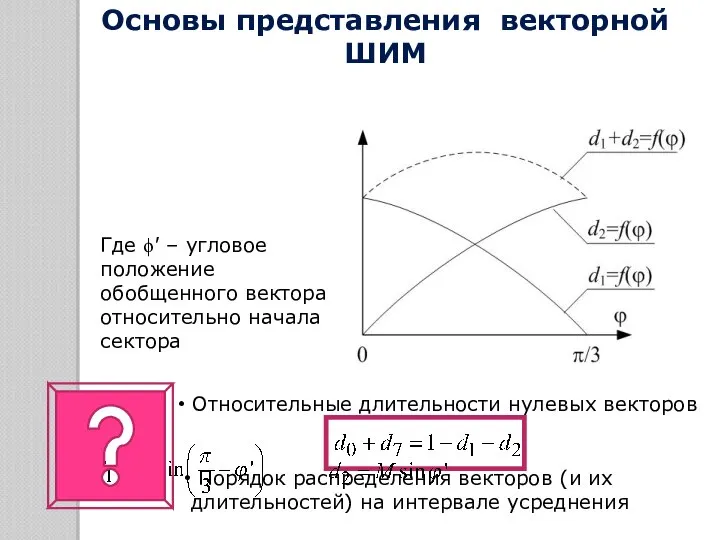

Порядок распределения векторов (и их длительностей) на интервале усреднения

Где ϕ'

Порядок распределения векторов (и их длительностей) на интервале усреднения

Где ϕ'

Основы представления векторной ШИМ

Относительные длительности нулевых векторов

Порядок распределения векторов (и их длительностей) на интервале усреднения

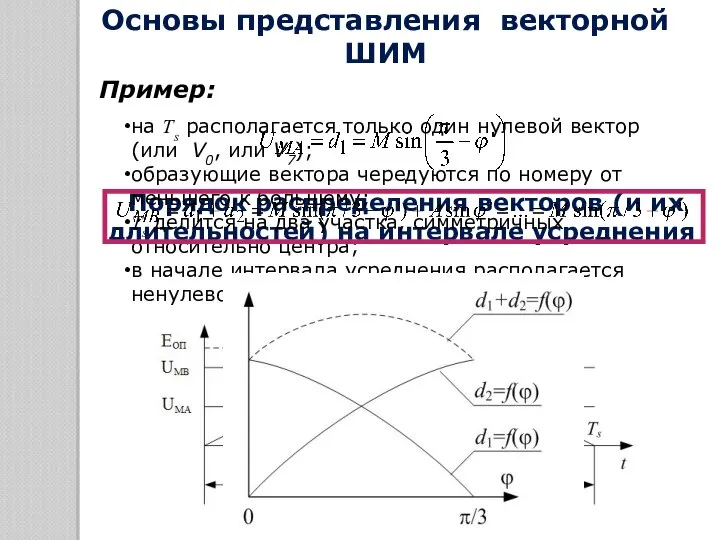

на Ts

Порядок распределения векторов (и их длительностей) на интервале усреднения

на Ts

образующие вектора чередуются по номеру от меньшего к большему;

Ts делится на два участка, симметричных относительно центра;

в начале интервала усреднения располагается ненулевой вектор.

Основы представления векторной ШИМ

Пример:

6) Вариант реализация векторной ШИМ в МПСУ:

Задать режимы работы МС и

6) Вариант реализация векторной ШИМ в МПСУ:

Задать режимы работы МС и

Задать период и режим счета таймера-счетчика.

В головной программе рассчитывать текущие коды двух модулирующих сигналов формирования состояния АИН и записывать их в соответствующие регистры сравнения (дважды буферированные).

Записывать также трехразрядный начальный вектор и устанавливать направления вращения обобщенного вектора (по или против часовой стрелки).

Все остальное делается модулем МС и ШИМ автоматически.

7) ПЛМ МС и ШИМ:

- COMCONx – регистр управления сравнения МнСА/В;

-

7) ПЛМ МС и ШИМ:

- COMCONx – регистр управления сравнения МнСА/В;

-

- DBTCONx – регистр управления таймером МВ МнСА/В;

- CMPR1(2,3) – 1(2,3)-й регистр сравнения (дважды буфериро-ванный).

8) Регистр управления сравнения COMCONА

Данный регистр определяет:

- является ли работа сравнения разрешенной;

- являются ли выходы сравнения разрешенными;

- условия загрузки рабочих регистров сравнения и регистра управления сравнением из программно-доступных регистров;

- разрешен ли режим ВШИМ.

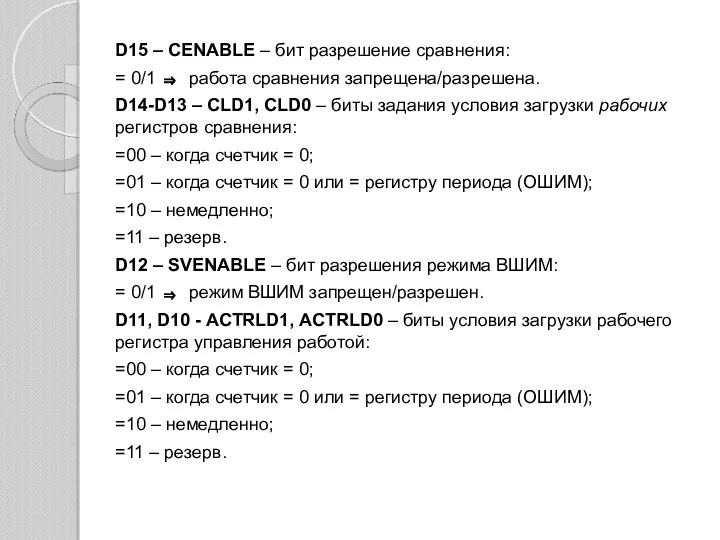

D15 – CENABLE – бит разрешение сравнения:

= 0/1 ⇒ работа сравнения

D15 – CENABLE – бит разрешение сравнения:

= 0/1 ⇒ работа сравнения

D14-D13 – CLD1, CLD0 – биты задания условия загрузки рабочих регистров сравнения:

=00 – когда счетчик = 0;

=01 – когда счетчик = 0 или = регистру периода (ОШИМ);

=10 – немедленно;

=11 – резерв.

D12 – SVENABLE – бит разрешения режима ВШИМ:

= 0/1 ⇒ режим ВШИМ запрещен/разрешен.

D11, D10 - ACTRLD1, ACTRLD0 – биты условия загрузки рабочего регистра управления работой:

=00 – когда счетчик = 0;

=01 – когда счетчик = 0 или = регистру периода (ОШИМ);

=10 – немедленно;

=11 – резерв.

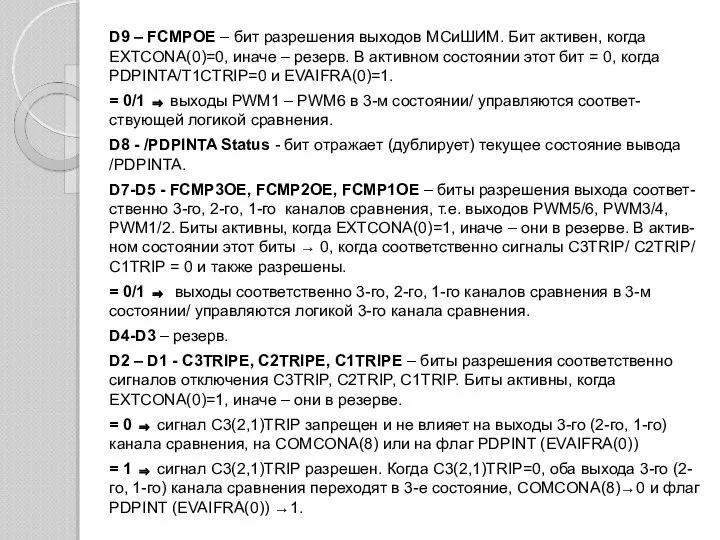

D9 – FCMPOE – бит разрешения выходов МСиШИМ. Бит активен, когда

D9 – FCMPOE – бит разрешения выходов МСиШИМ. Бит активен, когда

= 0/1 ⇒ выходы PWM1 – PWM6 в 3-м состоянии/ управляются соответ-ствующей логикой сравнения.

D8 - /PDPINTA Status - бит отражает (дублирует) текущее состояние вывода /PDPINTA.

D7-D5 - FCMP3OE, FCMP2OE, FCMP1OE – биты разрешения выхода соответ-ственно 3-го, 2-го, 1-го каналов сравнения, т.е. выходов PWM5/6, PWM3/4, PWM1/2. Биты активны, когда EXTCONA(0)=1, иначе – они в резерве. В актив-ном состоянии этот биты → 0, когда соответственно сигналы C3TRIP/ C2TRIP/ C1TRIP = 0 и также разрешены.

= 0/1 ⇒ выходы соответственно 3-го, 2-го, 1-го каналов сравнения в 3-м состоянии/ управляются логикой 3-го канала сравнения.

D4-D3 – резерв.

D2 – D1 - C3TRIPE, C2TRIPE, C1TRIPE – биты разрешения соответственно сигналов отключения C3TRIP, C2TRIP, C1TRIP. Биты активны, когда EXTCONA(0)=1, иначе – они в резерве.

= 0 ⇒ сигнал C3(2,1)TRIP запрещен и не влияет на выходы 3-го (2-го, 1-го) канала сравнения, на COMCONA(8) или на флаг PDPINT (EVAIFRA(0))

= 1 ⇒ сигнал C3(2,1)TRIP разрешен. Когда C3(2,1)TRIP=0, оба выхода 3-го (2-го, 1-го) канала сравнения переходят в 3-е состояние, COMCONA(8)→0 и флаг PDPINT (EVAIFRA(0)) →1.

9) Регистр управления работой сравнения ACTRА

Регистр управление работой сравнения ACTRA

9) Регистр управления работой сравнения ACTRА

Регистр управление работой сравнения ACTRA

ACTRA - дважды буферированный регистр. Условия, по которому этот регистр перезагружаются, определяется битами в COMCONА. ACTRA также содержит биты SVRDIR, D2, D1, D0, необходимые для работы ВШИМ.

D15 – SVRDIR – бит направления вращения обобщенного вектора. Исполь-зуется только при генерации ВШИМ.

= 0/1 ⇒ положительное (против ЧС)/ отрицательное (по ЧС) вращение.

D14-D12 – D2-D0 - Биты основных пространственных векторов. Используют-ся только при генерации ВШИМ.

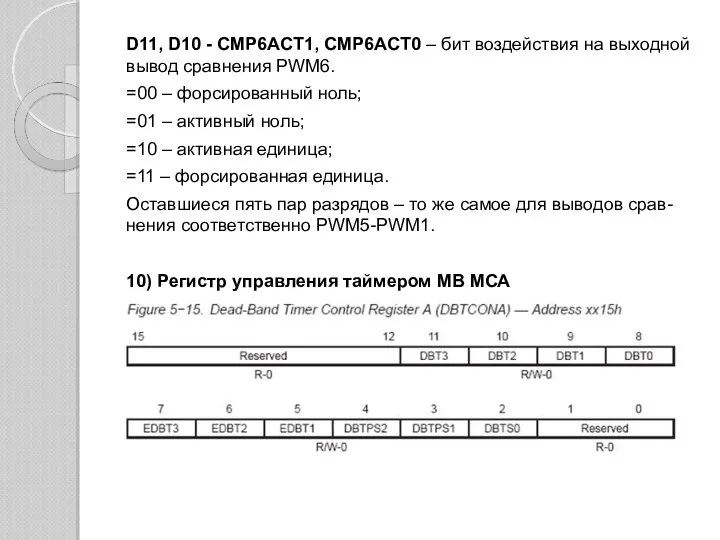

D11, D10 - CMP6ACT1, CMP6ACT0 – бит воздействия на выходной вывод

D11, D10 - CMP6ACT1, CMP6ACT0 – бит воздействия на выходной вывод

=00 – форсированный ноль;

=01 – активный ноль;

=10 – активная единица;

=11 – форсированная единица.

Оставшиеся пять пар разрядов – то же самое для выводов срав-нения соответственно PWM5-PWM1.

10) Регистр управления таймером МВ МСА

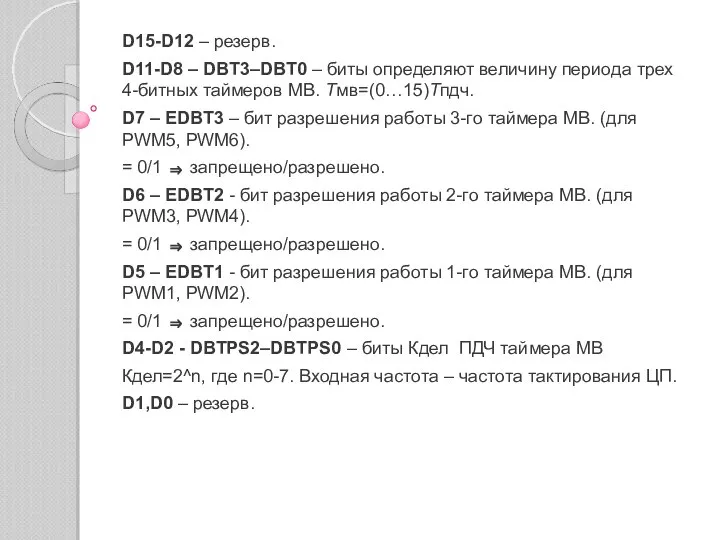

D15-D12 – резерв.

D11-D8 – DBT3–DBT0 – биты определяют величину периода трех

D15-D12 – резерв.

D11-D8 – DBT3–DBT0 – биты определяют величину периода трех

D7 – EDBT3 – бит разрешения работы 3-го таймера МВ. (для PWM5, PWM6).

= 0/1 ⇒ запрещено/разрешено.

D6 – EDBT2 - бит разрешения работы 2-го таймера МВ. (для PWM3, PWM4).

= 0/1 ⇒ запрещено/разрешено.

D5 – EDBT1 - бит разрешения работы 1-го таймера МВ. (для PWM1, PWM2).

= 0/1 ⇒ запрещено/разрешено.

D4-D2 - DBTPS2–DBTPS0 – биты Кдел ПДЧ таймера МВ

Кдел=2^n, где n=0-7. Входная частота – частота тактирования ЦП.

D1,D0 – резерв.

Тема 1 «Банковская система Российской Федерации»

Тема 1 «Банковская система Российской Федерации»  Регистрация опасных производственных объектов

Регистрация опасных производственных объектов Возле леса.

Возле леса. Структурное программирование в Step7

Структурное программирование в Step7 Множественные выравнивания

Множественные выравнивания Компоненты (виды) адаптивной физической культуры

Компоненты (виды) адаптивной физической культуры Изменения углекислого газа в классе

Изменения углекислого газа в классе

OptoGaN Enabling bulb-like brightness for LEDs

OptoGaN Enabling bulb-like brightness for LEDs Транспорт. Урок ИЗО

Транспорт. Урок ИЗО Презентация "Автомобили" - скачать презентации по Экономике

Презентация "Автомобили" - скачать презентации по Экономике Альтернативные источники энергии: их использование в современной архитектуре. Ветровая и солнечная энергия

Альтернативные источники энергии: их использование в современной архитектуре. Ветровая и солнечная энергия Технология ремонта кузовов автомобиля

Технология ремонта кузовов автомобиля Основные элементы языка программирования

Основные элементы языка программирования Внутренние войска МВД РФ Понятие, структура, полномочия Подготовил Студент юридического факультета Группы ЮБ-1401 Страшнов А.

Внутренние войска МВД РФ Понятие, структура, полномочия Подготовил Студент юридического факультета Группы ЮБ-1401 Страшнов А.  Презентация Microsoft PowerPoint (2)

Презентация Microsoft PowerPoint (2) СЕРОЛОГИЧЕСКИЕ РЕАКЦИИ СПбГУ 2013г.

СЕРОЛОГИЧЕСКИЕ РЕАКЦИИ СПбГУ 2013г.  Музейная практика

Музейная практика Презентация на тему "ЖЕСТОКОЕ ОБРАЩЕНИЕ С ДЕТЬМИ" - скачать презентации по Педагогике

Презентация на тему "ЖЕСТОКОЕ ОБРАЩЕНИЕ С ДЕТЬМИ" - скачать презентации по Педагогике Практическое занятие. Центрально-сжатый элемент

Практическое занятие. Центрально-сжатый элемент Справочные правовые системы, распространяемые на коммерческой основе

Справочные правовые системы, распространяемые на коммерческой основе Искусство полиграфии poly – много grafo - пишу

Искусство полиграфии poly – много grafo - пишу  Презентация "Виды монументальной живописи" - скачать презентации по МХК

Презентация "Виды монументальной живописи" - скачать презентации по МХК Рисуем пасхальное яичко Составила Учитель начальных классов МАОУ Ильинской СОШ Белозёрова Татьяна Владимировна

Рисуем пасхальное яичко Составила Учитель начальных классов МАОУ Ильинской СОШ Белозёрова Татьяна Владимировна  Высокоуровневое тестирование

Высокоуровневое тестирование  Коронарное кровообращение

Коронарное кровообращение  Политология и политическая теория. Проблемы истории и теории политической науки

Политология и политическая теория. Проблемы истории и теории политической науки Эффективная коммуникация

Эффективная коммуникация Двигатель внутреннего сгорания. Устройство

Двигатель внутреннего сгорания. Устройство