Содержание

- 2. Список литературы 1. В.Ф. Мелехин. Вычислительные машины системы и сети.

- 3. Иерархия запоминающих устройств Память наряду с процессором в значительной мере определяет основные возможности ВМ — ее

- 4. Иерархия запоминающих устройств

- 5. Иерархия запоминающих устройств ГОУ ОГУ 2008 Закономерности: • чем меньше время доступа, тем выше стоимость хранения

- 6. Иерархия запоминающих устройств ГОУ ОГУ 2008 По мере движения вниз по иерархической структуре: 1. Уменьшается соотношение

- 7. Структура микросхемы памяти ГОУ ОГУ 2008

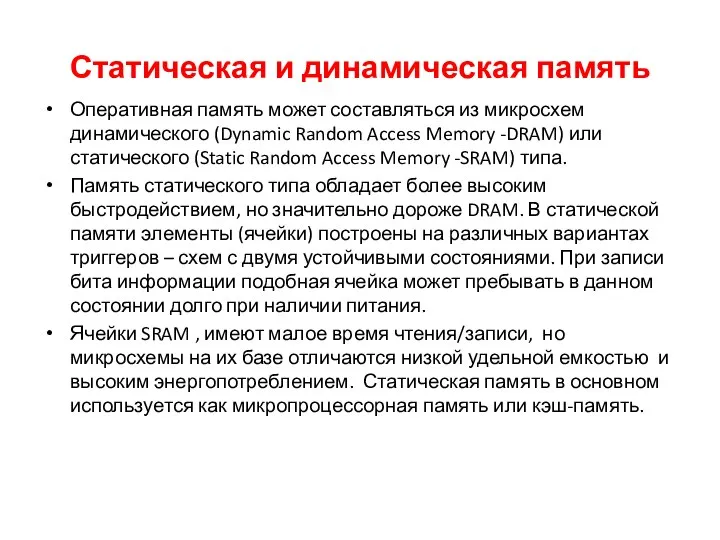

- 8. Статическая и динамическая память Оперативная память может составляться из микросхем динамического (Dynamic Random Access Memory -DRAM)

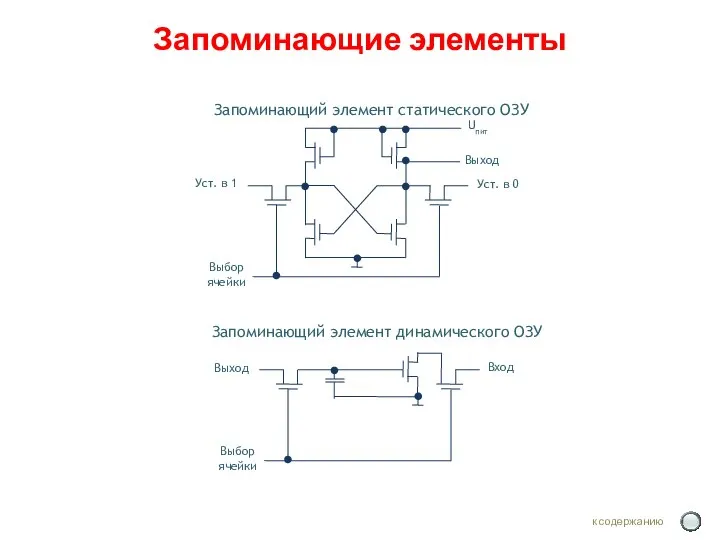

- 9. Запоминающие элементы ГОУ ОГУ 2008 Запоминающий элемент динамического ОЗУ Запоминающий элемент статического ОЗУ

- 10. Кэш-память Кэш-память представляет собой быстродействующее ЗУ, размещенное на одном кристалле с ЦП или внешнее по отношению

- 11. В структуре кэш-памяти выделяют два типа блоков данных: - память отображения данных (собственно сами данные, дублированные

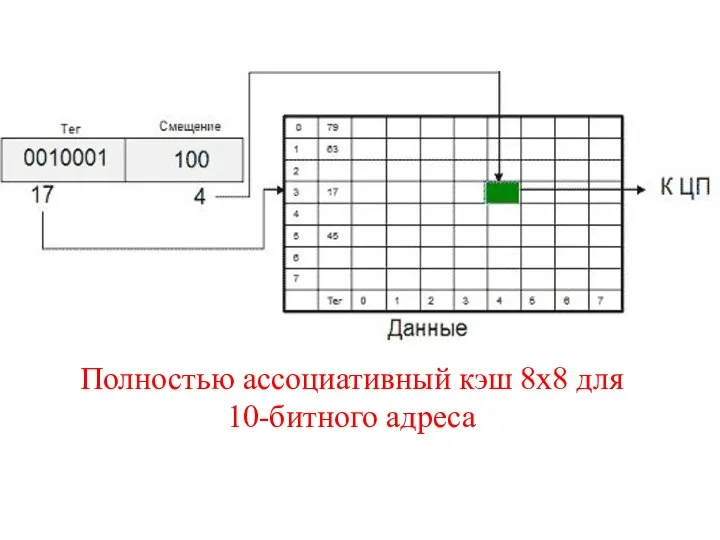

- 12. Полностью ассоциативный кэш 8х8 для 10-битного адреса

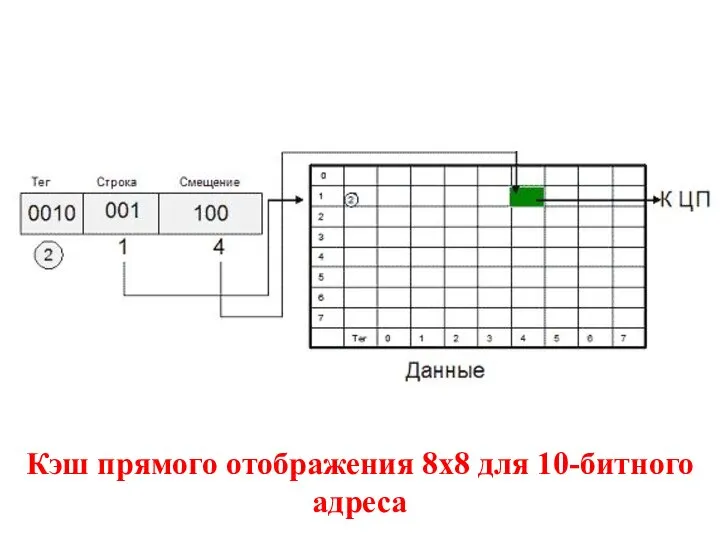

- 13. Кэш прямого отображения 8х8 для 10-битного адреса

- 14. Двухвходовый ассоциативный кэш 8х8 для 10-битного адреса

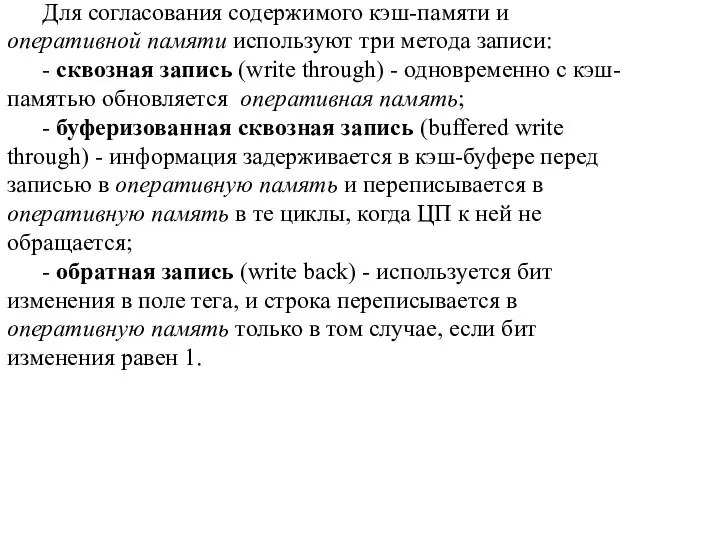

- 15. Для согласования содержимого кэш-памяти и оперативной памяти используют три метода записи: - cквозная запись (write through)

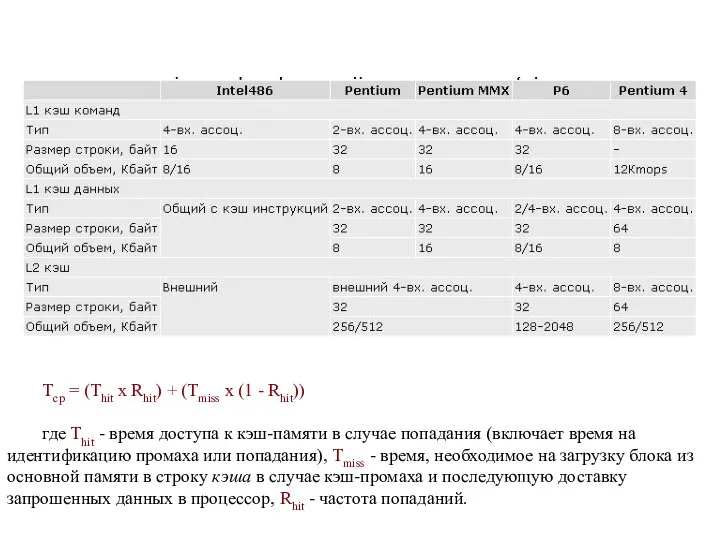

- 16. Tср = (Thit x Rhit) + (Tmiss x (1 - Rhit)) где Thit - время доступа

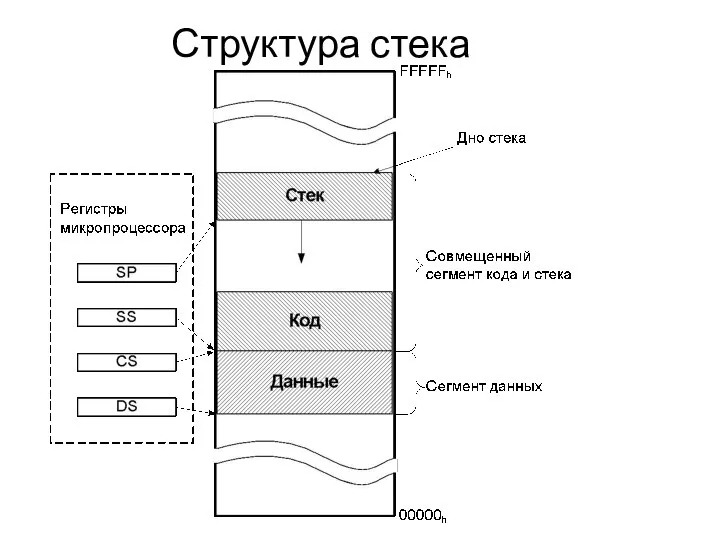

- 17. Структура стека

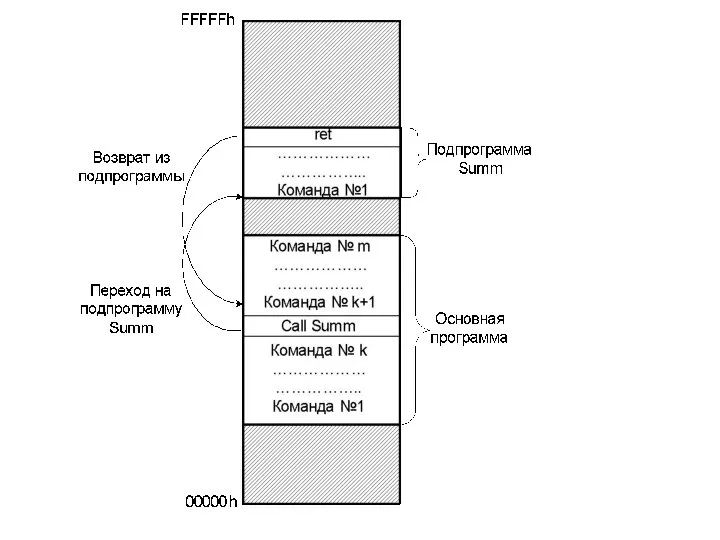

- 18. Схема работы со стеком

- 22. Скачать презентацию

СВОЙСТВА ФУНКЦИИ

СВОЙСТВА ФУНКЦИИ 1С БИГ ФСС - Быкова( 1C)

1С БИГ ФСС - Быкова( 1C) Корпоративная культура организации

Корпоративная культура организации Музыкальная культура барокко и классицизма

Музыкальная культура барокко и классицизма Перспективы выявления на территории г. Кургана объектов советской эпохи, обладающих признаками ОКН

Перспективы выявления на территории г. Кургана объектов советской эпохи, обладающих признаками ОКН Ǵylymı jobamnyń taqyryby: Latyn álipbıine kóshý- qazaq tiliniń jańa beınesi

Ǵylymı jobamnyń taqyryby: Latyn álipbıine kóshý- qazaq tiliniń jańa beınesi Виды проецирования. Признак принадлежности точки – прямой. Деление отрезка прямой в заданном отношении. Теорема Фалеса

Виды проецирования. Признак принадлежности точки – прямой. Деление отрезка прямой в заданном отношении. Теорема Фалеса Атомистическая теория

Атомистическая теория  Макроэкономическая нестабильность: экономические циклы, безработица, инфляция Экономический цикл и динамика основных макроэкон

Макроэкономическая нестабильность: экономические циклы, безработица, инфляция Экономический цикл и динамика основных макроэкон NTFS MFT Example

NTFS MFT Example Опрос по дисциплине: «ТОТТС» Цьопа Фединн

Опрос по дисциплине: «ТОТТС» Цьопа Фединн  ОРГАНИЗАЦИЯ РАБОТЫ С ПИСЬМАМИ И ЗАЯВЛЕНИЯМИ ГРАЖДАН И ВЕДЕНИЕ ДЕЛОПРОИЗВОДСТВА ПО ОБРАЩЕНИЯМ ГРАЖДАН

ОРГАНИЗАЦИЯ РАБОТЫ С ПИСЬМАМИ И ЗАЯВЛЕНИЯМИ ГРАЖДАН И ВЕДЕНИЕ ДЕЛОПРОИЗВОДСТВА ПО ОБРАЩЕНИЯМ ГРАЖДАН  Психолингвистика. Язык и речевая деятельность

Психолингвистика. Язык и речевая деятельность Гжель. Роспись

Гжель. Роспись Презентация на тему "Артериальная гипертензия" - скачать презентации по Медицине

Презентация на тему "Артериальная гипертензия" - скачать презентации по Медицине Презентация на тему "Строение и функции рианодиновых рецепторов" - скачать презентации по Медицине

Презентация на тему "Строение и функции рианодиновых рецепторов" - скачать презентации по Медицине Linux Basics

Linux Basics Презентация ВНЕШНЯЯ ПОЛИТИКА РОССИИ В XVII ВЕКЕ

Презентация ВНЕШНЯЯ ПОЛИТИКА РОССИИ В XVII ВЕКЕ Терминология в сфере нанотехнологий (на материале немецкого языка)

Терминология в сфере нанотехнологий (на материале немецкого языка) День славянской письменности и культуры

День славянской письменности и культуры КГМУ Кафедра общей хирургии Раны и раневой процесс

КГМУ Кафедра общей хирургии Раны и раневой процесс  Презентация на тему "ПЛОМБИРОВОЧНЫЕ МАТЕРИАЛЫ" - скачать презентации по Медицине

Презентация на тему "ПЛОМБИРОВОЧНЫЕ МАТЕРИАЛЫ" - скачать презентации по Медицине Книга рекордов Гиннесса «Хороша книга – точно беседа с умным человеком». &nbs

Книга рекордов Гиннесса «Хороша книга – точно беседа с умным человеком». &nbs Актуальность проблемы духовно-нравственного воспитания школьников Кошелева М.Е., зав.кафедрой педагогики и психологии ПИППКРО,

Актуальность проблемы духовно-нравственного воспитания школьников Кошелева М.Е., зав.кафедрой педагогики и психологии ПИППКРО, Белорусская народная вышивка

Белорусская народная вышивка Social etiquette in the UK

Social etiquette in the UK Адаптация учащихся 5-х классов.

Адаптация учащихся 5-х классов. Идеология и культура 1946-48 г. 9 класс

Идеология и культура 1946-48 г. 9 класс