Содержание

- 2. Характеристики запоминающих устройств Емкость. Разрядность. Способ доступа. Физический тип или тип носителя. Быстродействие. Способ организации. Стоимость.

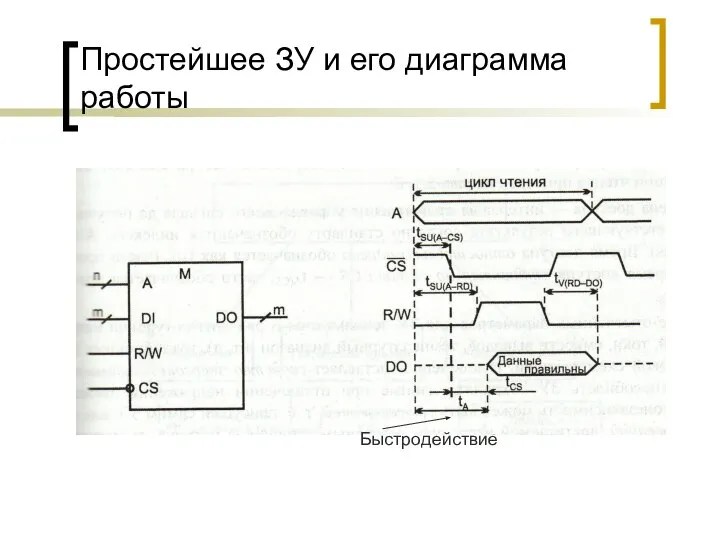

- 3. Простейшее ЗУ и его диаграмма работы Быстродействие

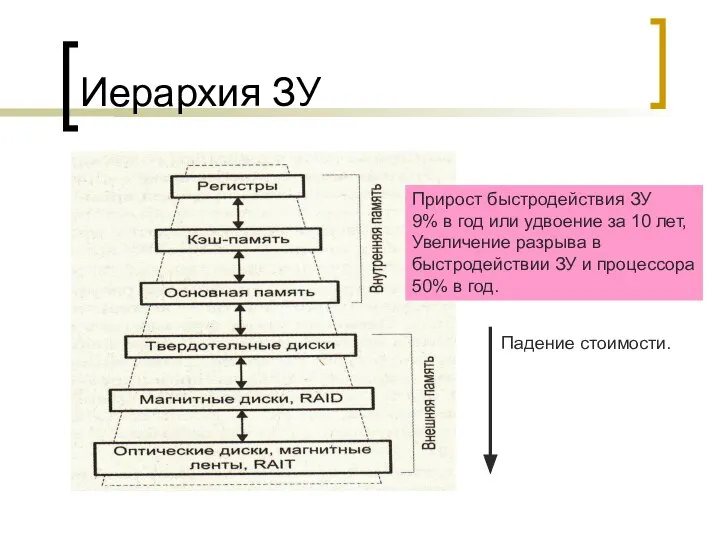

- 4. Иерархия ЗУ Прирост быстродействия ЗУ 9% в год или удвоение за 10 лет, Увеличение разрыва в

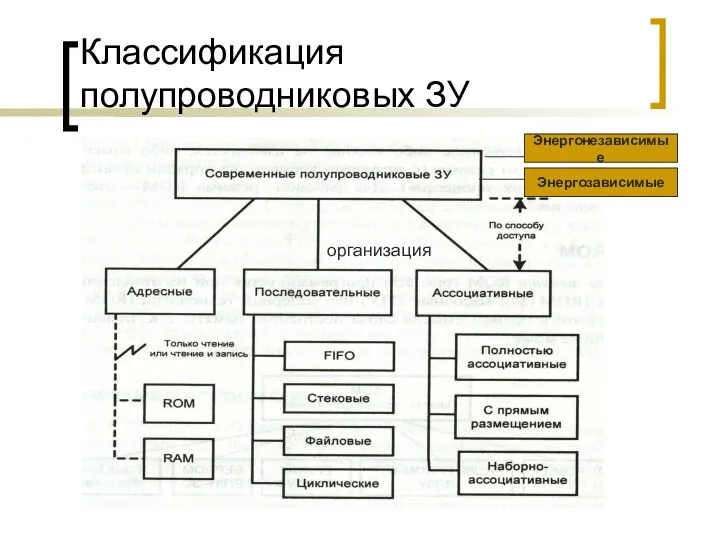

- 5. Классификация полупроводниковых ЗУ организация Энергонезависимые Энергозависимые

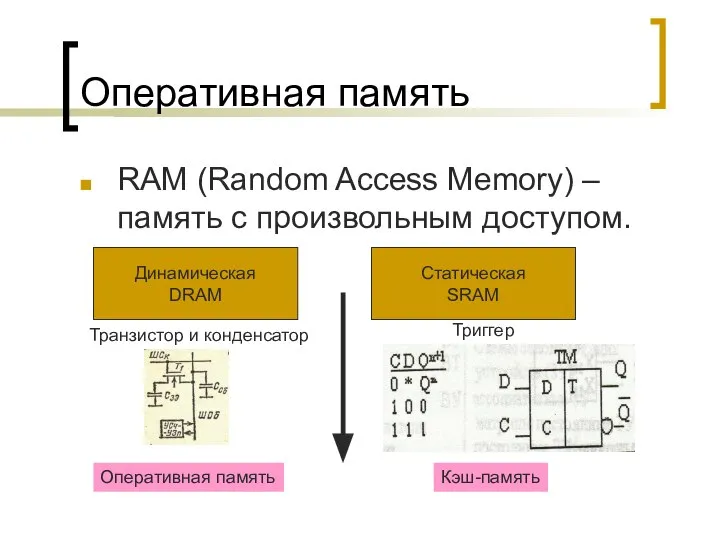

- 6. Оперативная память RAM (Random Access Memory) – память с произвольным доступом. Динамическая DRAM Статическая SRAM Триггер

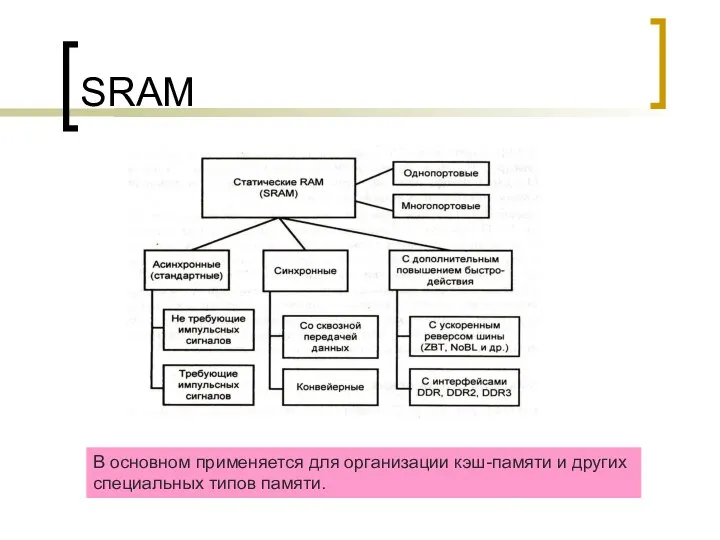

- 7. SRAM В основном применяется для организации кэш-памяти и других специальных типов памяти.

- 8. Способы организации ЗУ Структура 2D; Структура 3D; Структура 2DM; Блочные структуры; Структура видеопамяти; Буфер FIFO; Буфер

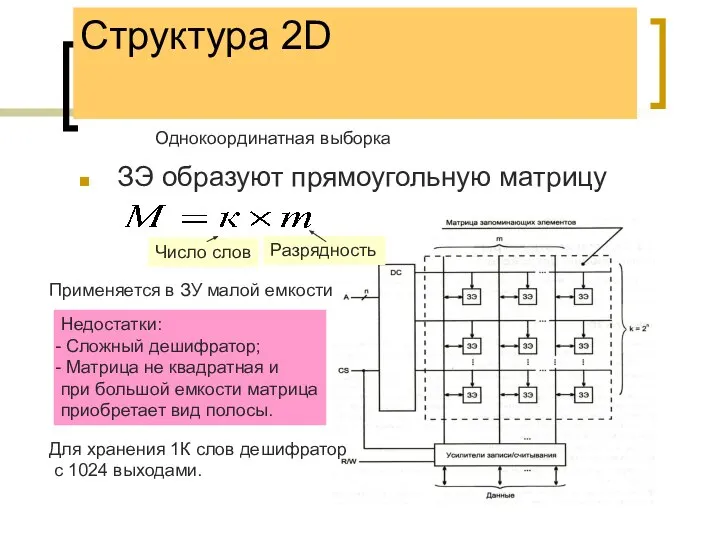

- 9. Структура 2D ЗЭ образуют прямоугольную матрицу Разрядность Число слов Применяется в ЗУ малой емкости Недостатки: Сложный

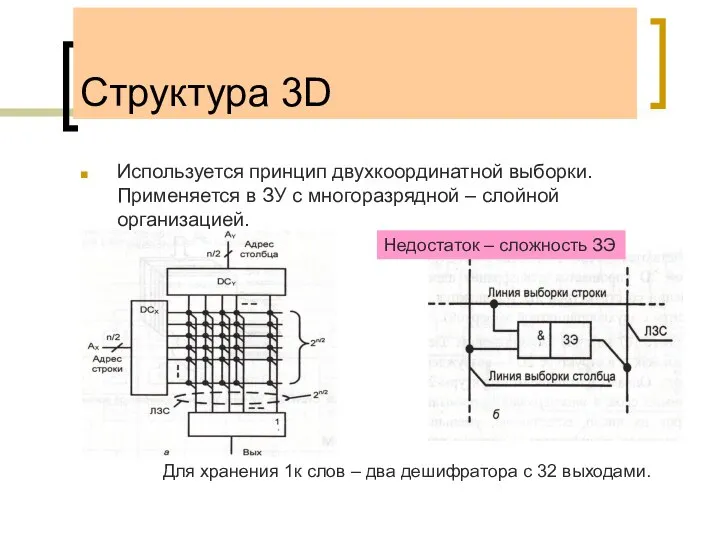

- 10. Структура 3D Используется принцип двухкоординатной выборки. Применяется в ЗУ с многоразрядной – слойной организацией. Для хранения

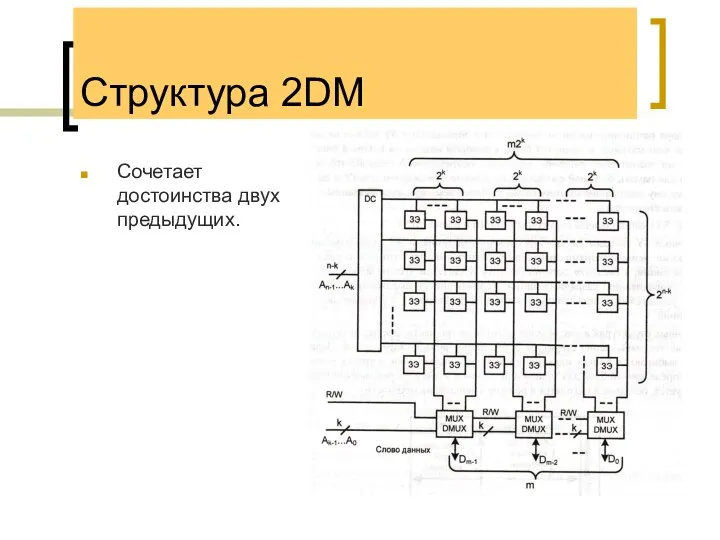

- 11. Структура 2DM Сочетает достоинства двух предыдущих.

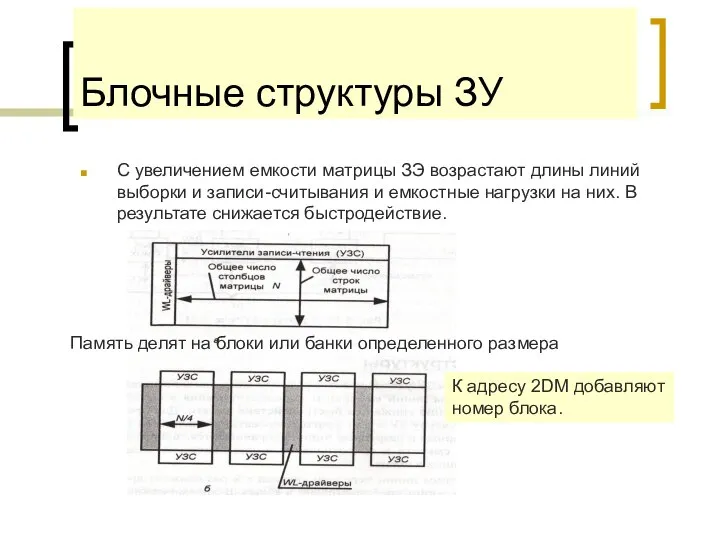

- 12. Блочные структуры ЗУ С увеличением емкости матрицы ЗЭ возрастают длины линий выборки и записи-считывания и емкостные

- 13. Блочная организация оперативной памяти Пока идет регенерация в одном банке, можно работать с другим банком.

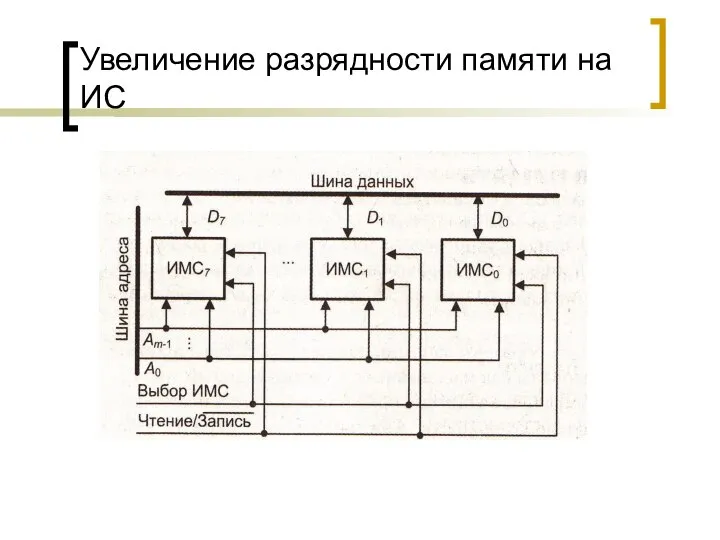

- 14. Увеличение разрядности памяти на ИС

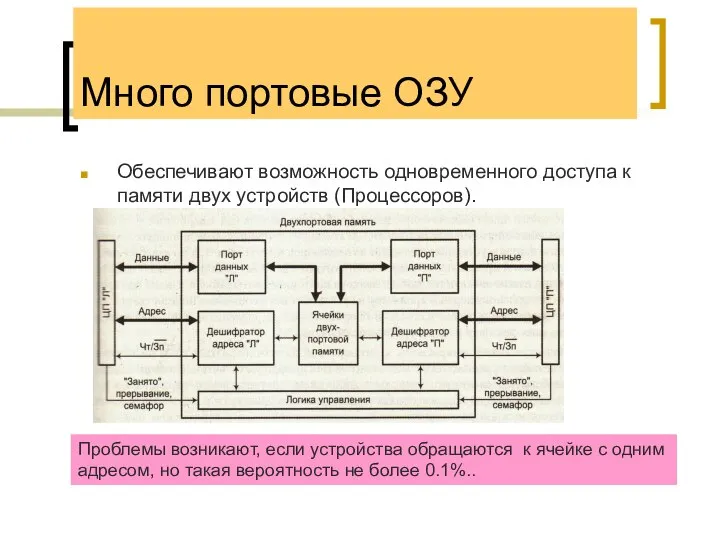

- 15. Много портовые ОЗУ Обеспечивают возможность одновременного доступа к памяти двух устройств (Процессоров). Проблемы возникают, если устройства

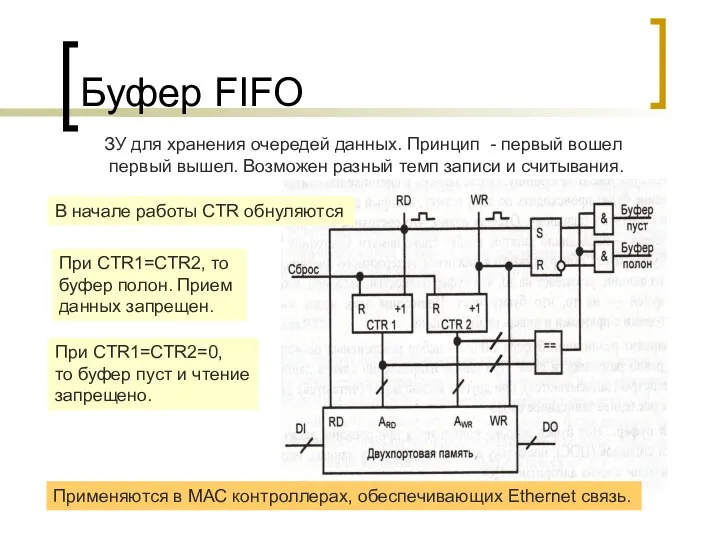

- 16. Буфер FIFO ЗУ для хранения очередей данных. Принцип - первый вошел первый вышел. Возможен разный темп

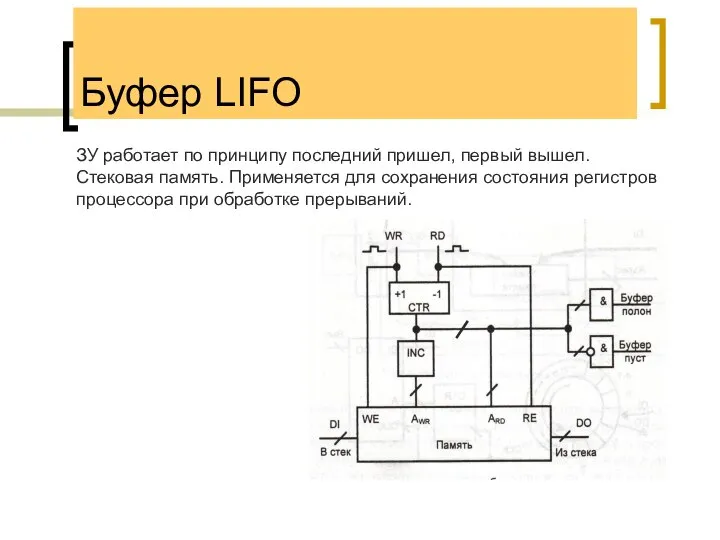

- 17. Буфер LIFO ЗУ работает по принципу последний пришел, первый вышел. Стековая память. Применяется для сохранения состояния

- 18. Круговой буфер Применяется при решении задач цифровой обработки сигналов, обеспечивая задержку данных для реализации алгоритмов ЦОС.

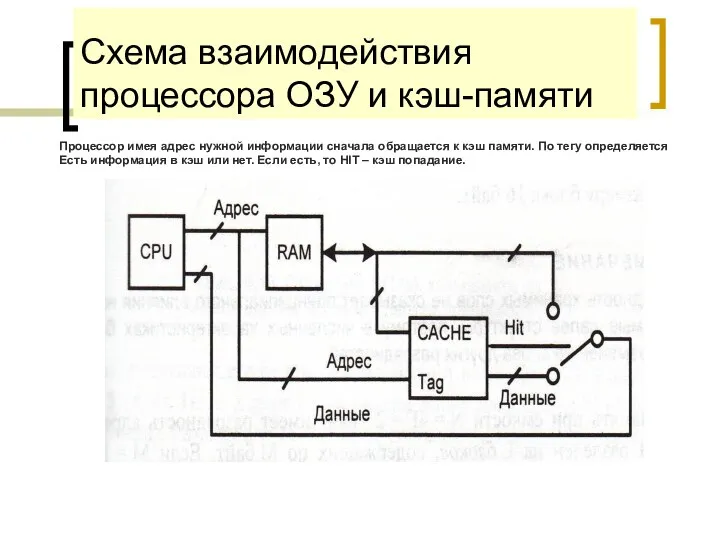

- 19. Схема взаимодействия процессора ОЗУ и кэш-памяти Процессор имея адрес нужной информации сначала обращается к кэш памяти.

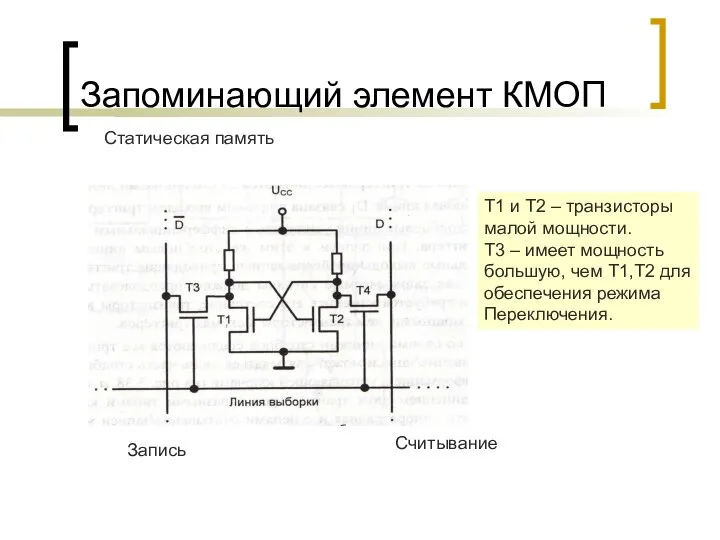

- 20. Запоминающий элемент КМОП Считывание Запись Т1 и Т2 – транзисторы малой мощности. Т3 – имеет мощность

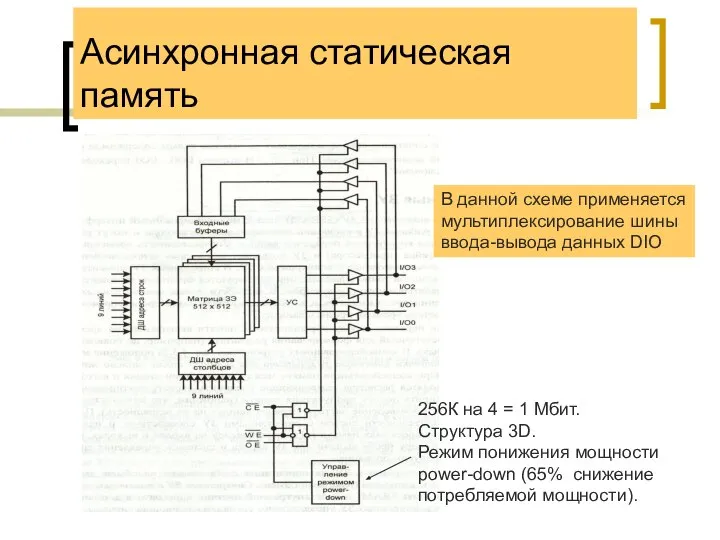

- 21. Асинхронная статическая память 256К на 4 = 1 Мбит. Структура 3D. Режим понижения мощности рower-down (65%

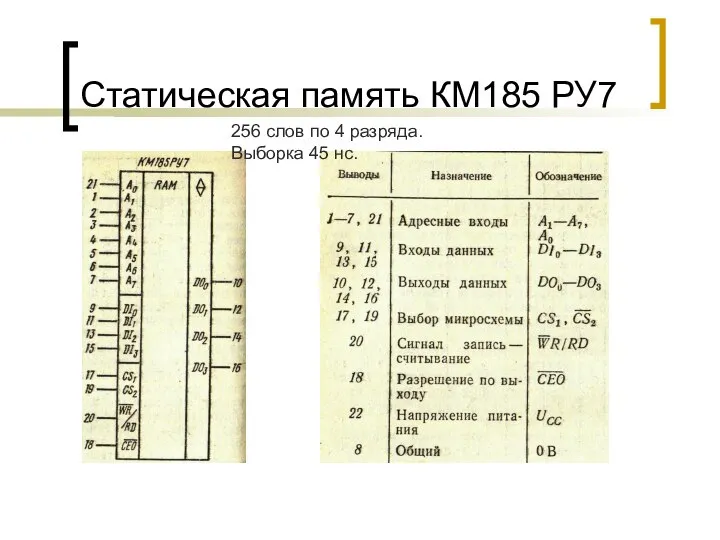

- 22. Статическая память КМ185 РУ7 256 слов по 4 разряда. Выборка 45 нс.

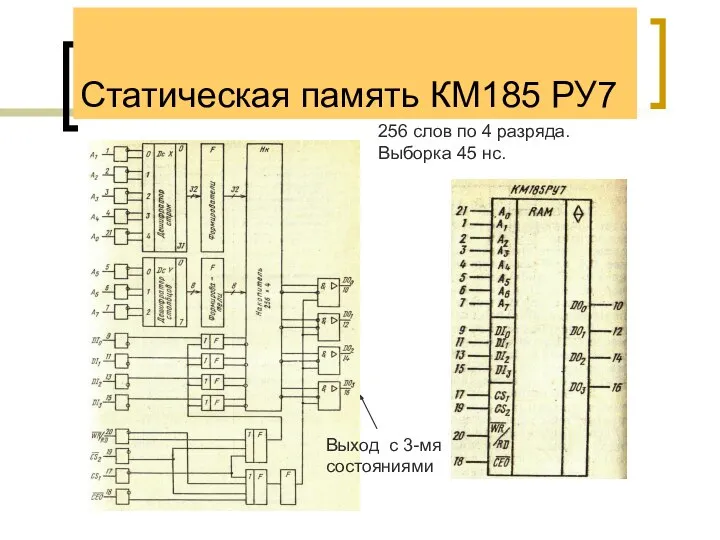

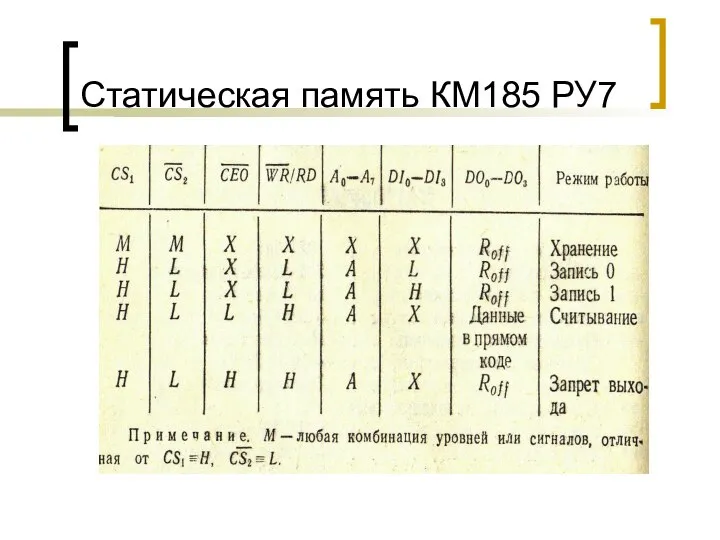

- 23. Статическая память КМ185 РУ7 256 слов по 4 разряда. Выборка 45 нс. Выход с 3-мя состояниями

- 24. Статическая память КМ185 РУ7

- 25. Синхронная статическая память RG RG 9 си При добавлении выделенных регистров, работающих по переднему фронту синхросигнала

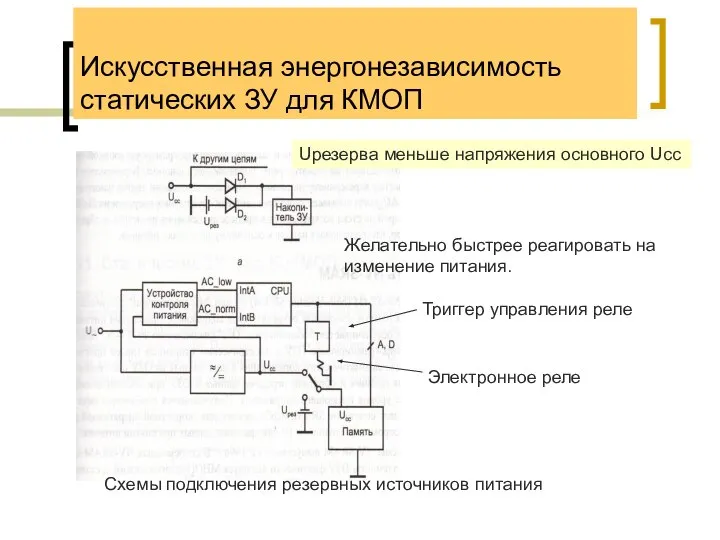

- 26. Искусственная энергонезависимость статических ЗУ для КМОП Схемы подключения резервных источников питания Uрезерва меньше напряжения основного Uсс

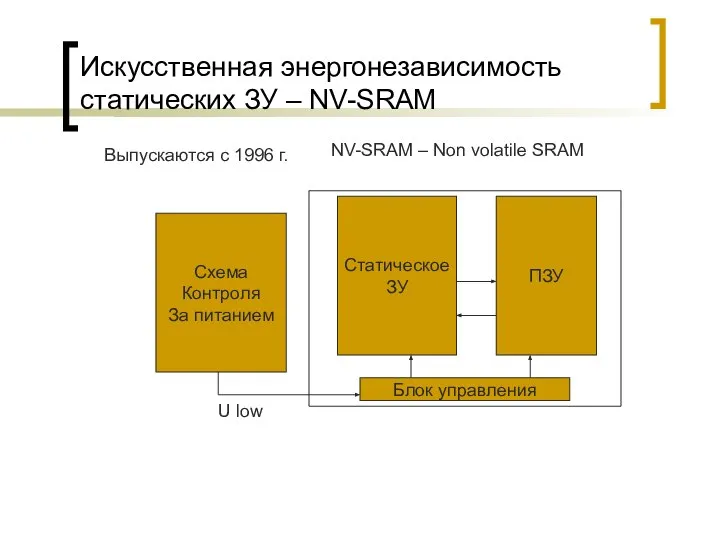

- 27. Искусственная энергонезависимость статических ЗУ – NV-SRAM Выпускаются с 1996 г. Схема Контроля За питанием Статическое ЗУ

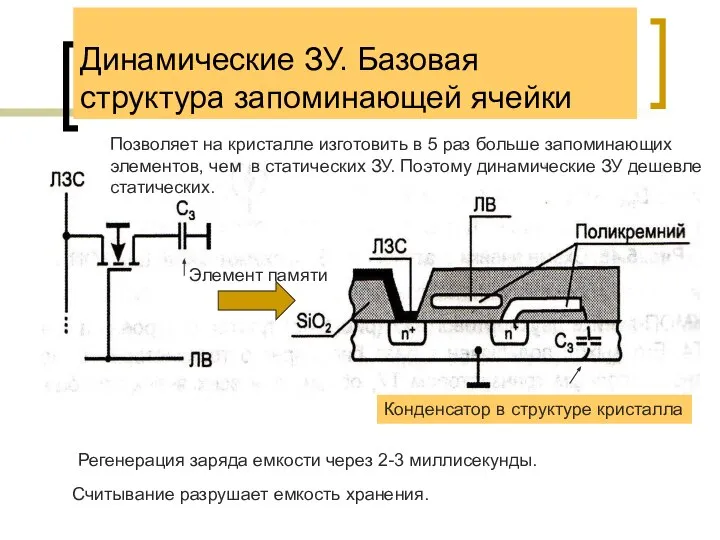

- 28. Динамические ЗУ. Базовая структура запоминающей ячейки Позволяет на кристалле изготовить в 5 раз больше запоминающих элементов,

- 29. Особенности динамических ЗУ Поток обращений к динамическому ЗУ должен учитывать состояние в котором оно находится. Регенерация

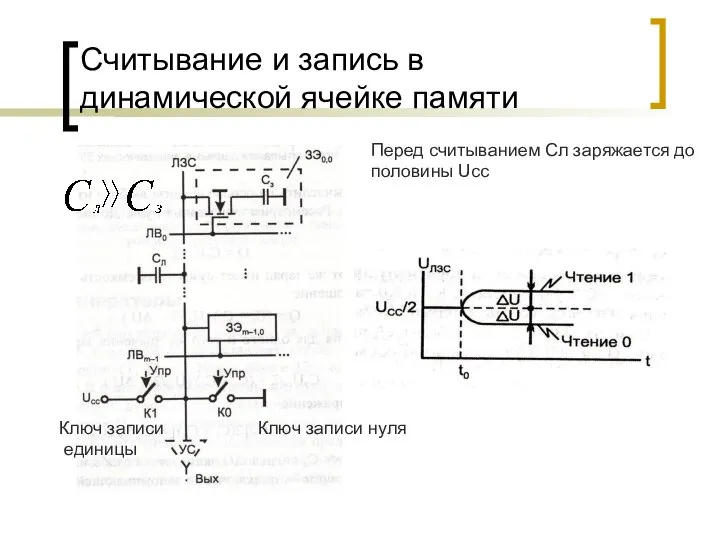

- 30. Считывание и запись в динамической ячейке памяти Ключ записи нуля Ключ записи единицы Перед считыванием Сл

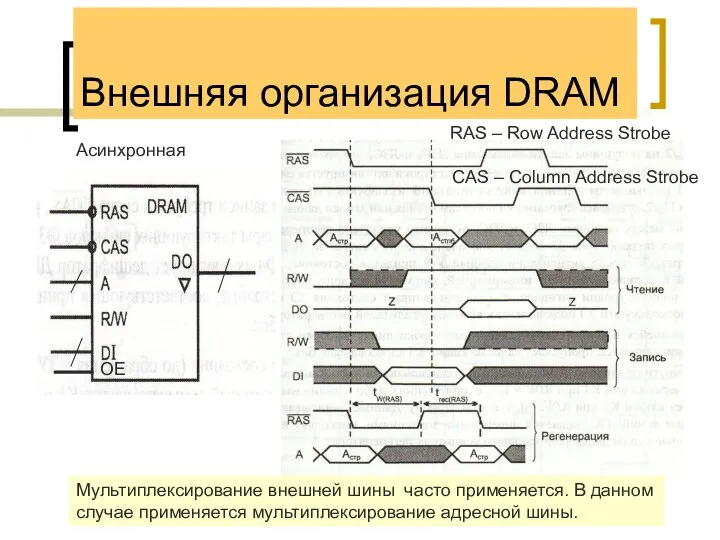

- 31. Внешняя организация DRAM Мультиплексирование внешней шины часто применяется. В данном случае применяется мультиплексирование адресной шины. Асинхронная

- 32. Организация микросхем динамической памяти OE output enable WE write enable CS chip select DIO

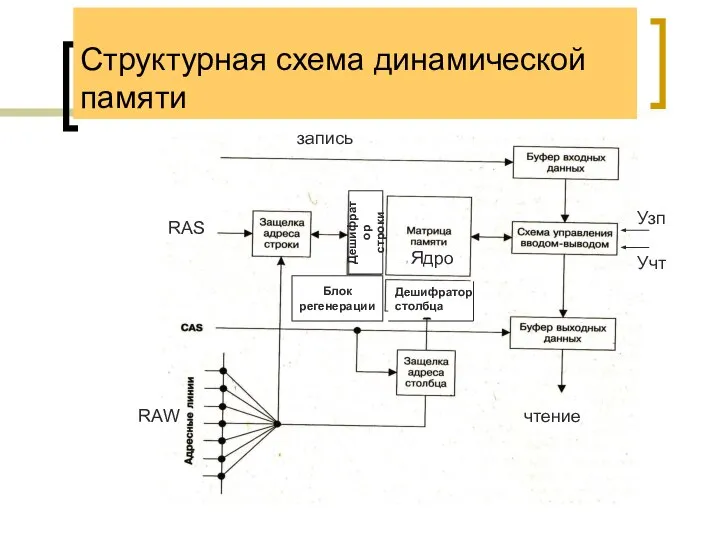

- 33. Структурная схема динамической памяти Блок регенерации RAS RAW Дешифратор столбца Дешифратор строки запись чтение Узп Учт

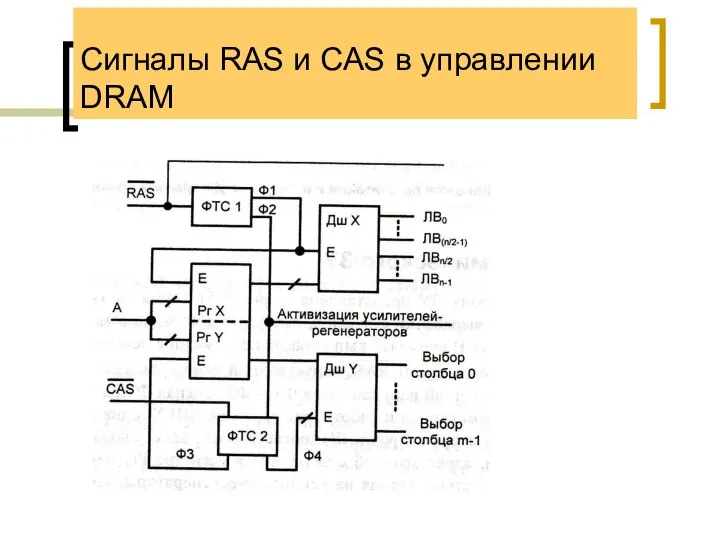

- 34. Сигналы RAS и CAS в управлении DRAM

- 35. Методы повышения быстродействия динамических ЗУ Быстрый страничный доступ. Используется принцип локальности следования адресов. Не требуется смена

- 36. Эволюция оперативной памяти динамического типа FPM – Fast Page Mode – динамическая память с быстрым страничным

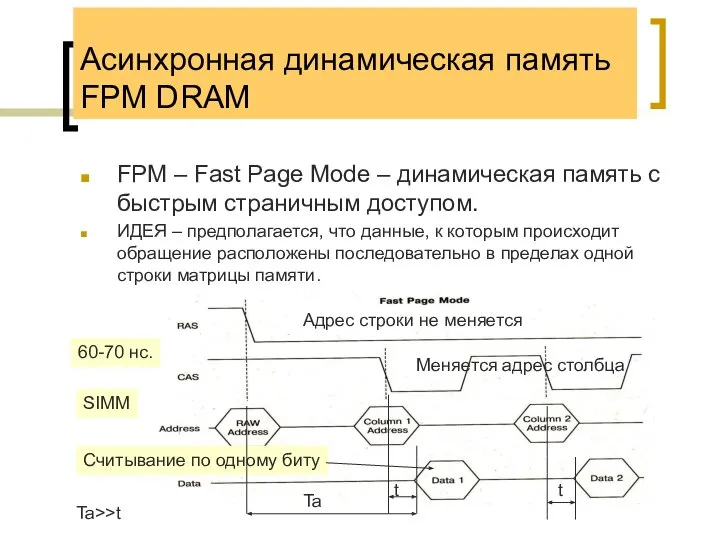

- 37. Асинхронная динамическая память FPM DRAM FPM – Fast Page Mode – динамическая память с быстрым страничным

- 38. Асинхронная динамическая память EDO DRAM EDO – Extended Data Out. Расширенное время удержания данных на выходе.

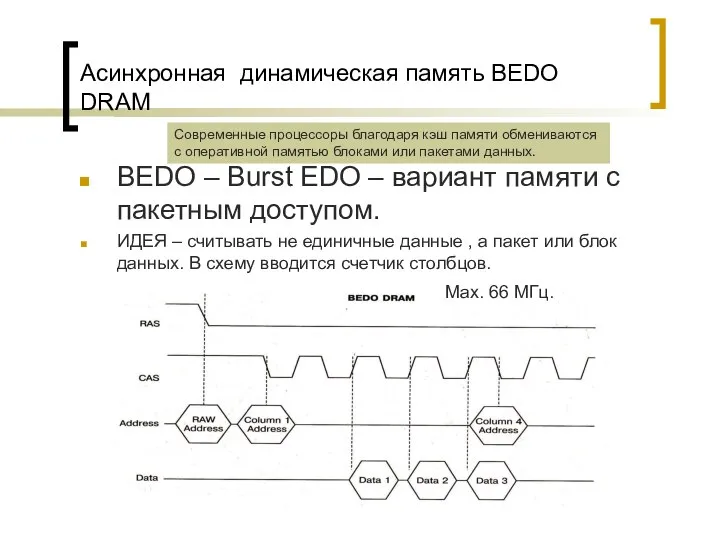

- 39. Асинхронная динамическая память BEDO DRAM BEDO – Burst EDO – вариант памяти с пакетным доступом. ИДЕЯ

- 40. Недостаток асинхронной динамической памяти Процессор ждет выполнение операций с памятью. Других действий при этом он выполнять

- 41. Переход к синхронной динамической памяти. Особенности организации. Увязка операций с тактирующими сигналами. Буферизация адресов и данных.

- 42. Синхронная динамическая память SDRAM Синхронизация входных и выходных сигналов с тактами системного генератора. Но при этом

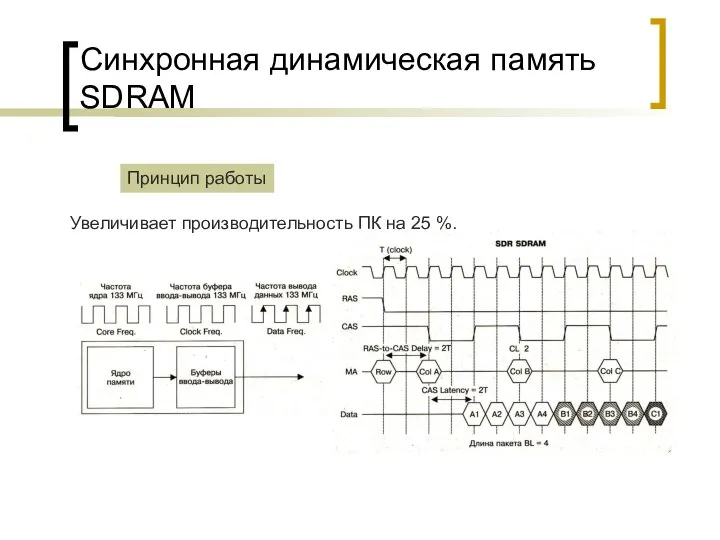

- 43. Синхронная динамическая память SDRAM Принцип работы Увеличивает производительность ПК на 25 %.

- 44. Синхронная динамическая память DDR (Double Data Rate) DDR означает удвоенную скорость передачи данных при вводе выводе.

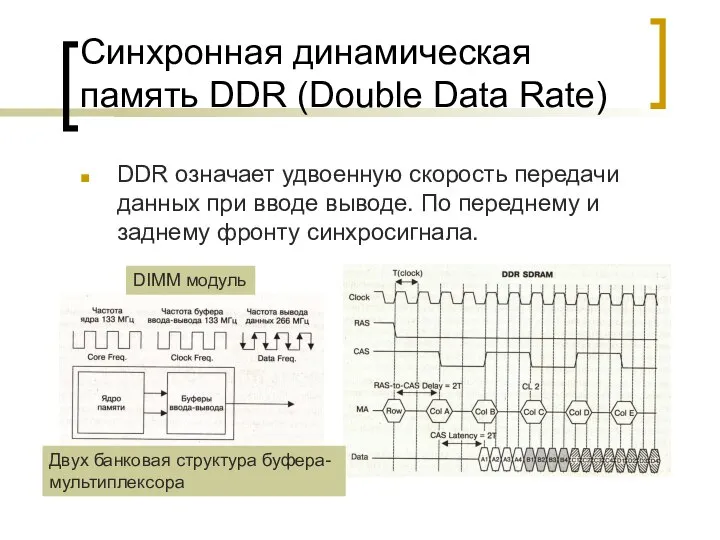

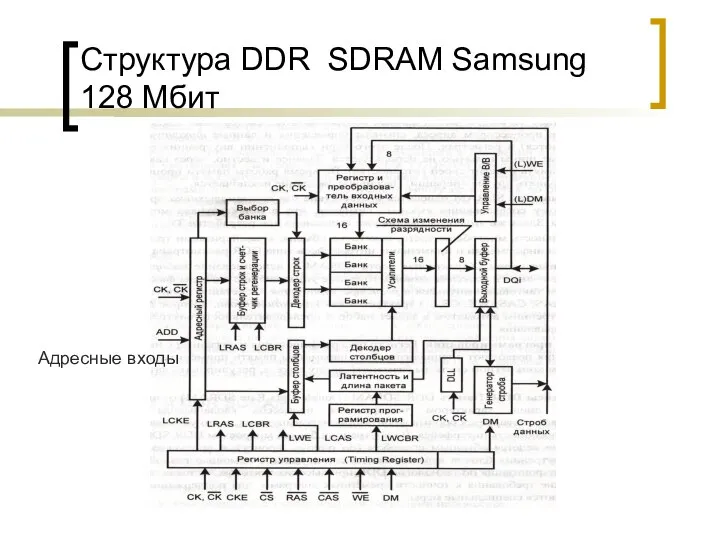

- 45. Структура DDR SDRAM Samsung 128 Мбит Адресные входы

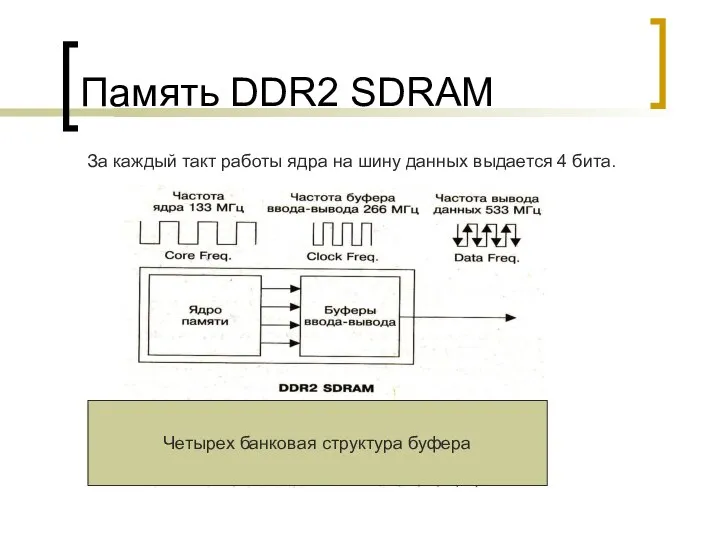

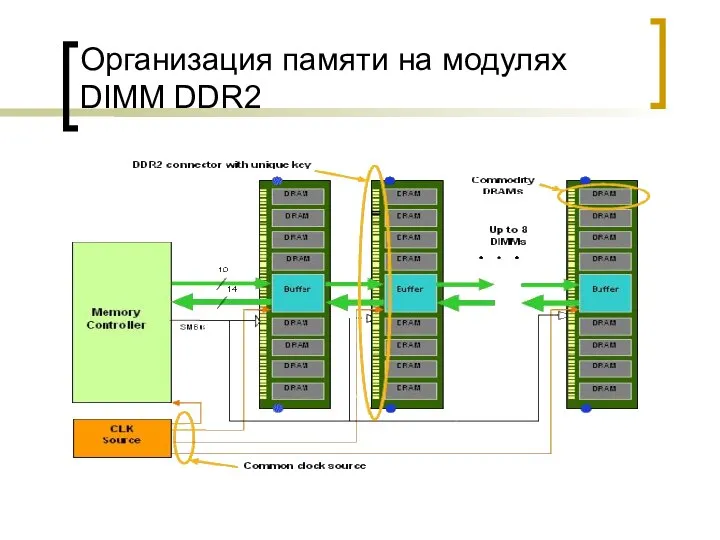

- 46. Память DDR2 SDRAM За каждый такт работы ядра на шину данных выдается 4 бита. Четырех банковая

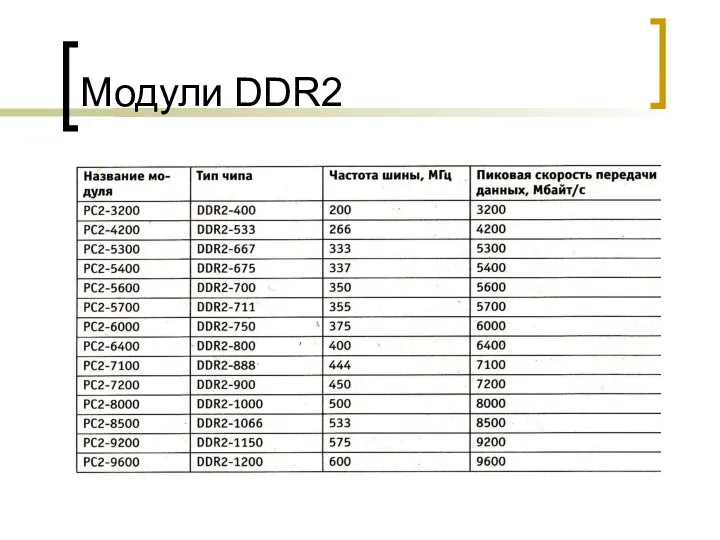

- 47. Модули DDR2

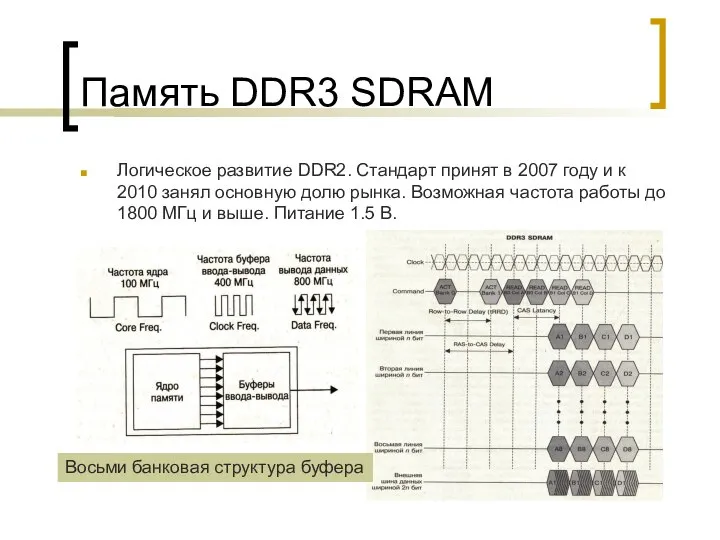

- 48. Память DDR3 SDRAM Логическое развитие DDR2. Стандарт принят в 2007 году и к 2010 занял основную

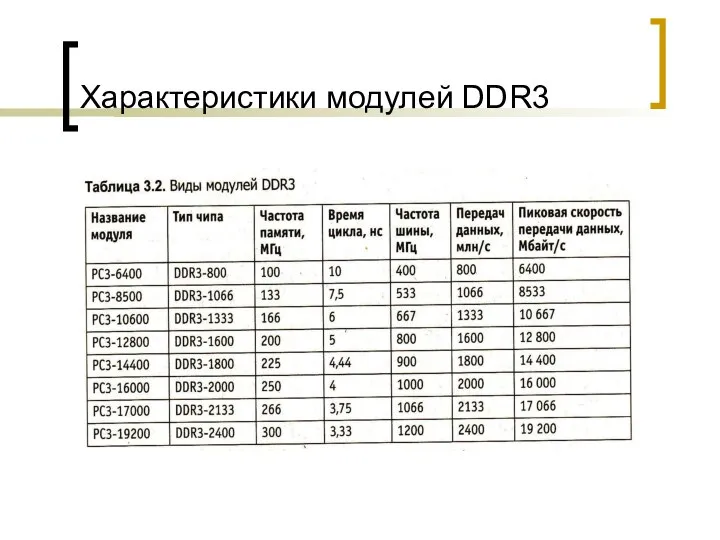

- 49. Характеристики модулей DDR3

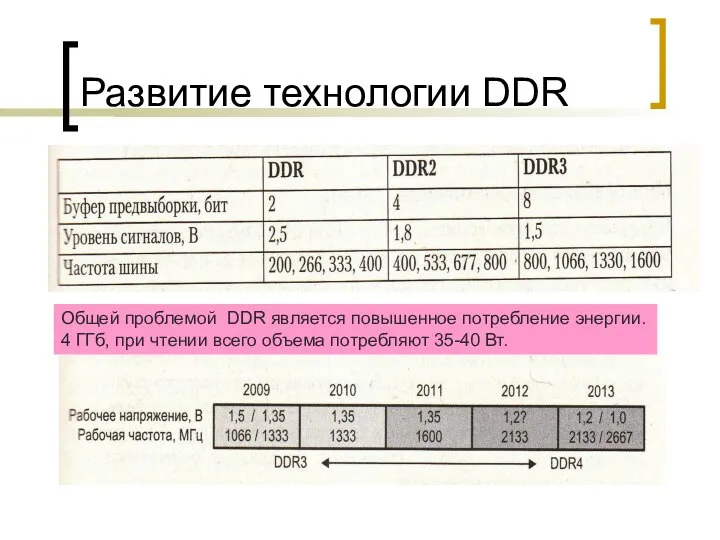

- 50. Развитие технологии DDR Общей проблемой DDR является повышенное потребление энергии. 4 ГГб, при чтении всего объема

- 51. Rambus DRAM Применяется в графических и мультимедийных приложениях – там где надо выдать длинную последовательность слов.

- 52. RLDRAM (Reduced Latency DRAM) Идея – уменьшение длительности полного цикла обращения к памяти , за счет

- 53. FCRAM (Fast Cycle RAM) Идея – сегментация ядра памяти и выполнение одновременной адресации к ячейкам сегмента.

- 54. Перспективные ЗУ FRAM – ферроэлектрические. PFRAM – полимерно-ферроэлектрические. MRAM – магниторезистивные. Использование в качестве элемента памяти

- 55. Виды модулей оперативной памяти SIMM – (Single In-line Memory Module) - печатная плата с односторонним краевым

- 56. Виды модулей оперативной памяти DIMM (Dual In-line Memory Module) – печатная плата с двухсторонним разъемом типа

- 57. Организация памяти на модулях DIMM DDR2

- 58. Виды модулей оперативной памяти RIMM (Rambus In-line Memory Module) – похожи на модули DIMM, микросхемы памяти

- 60. Скачать презентацию

Динамические и статистические закономерности, особенности их проявления

Динамические и статистические закономерности, особенности их проявления Нарушение функционирования рычага механизма переключения коробки передач

Нарушение функционирования рычага механизма переключения коробки передач Методы фиксации цен во внешнеторговых контрактах

Методы фиксации цен во внешнеторговых контрактах Реалистические тенденции в живописи Голландии. Тема 4 Автор: учитель истории Привалова В.С.

Реалистические тенденции в живописи Голландии. Тема 4 Автор: учитель истории Привалова В.С. Закономерности истории политики. (Тема 4)

Закономерности истории политики. (Тема 4) политика монетизации экономика Давлатзода П С Группа Т-093

политика монетизации экономика Давлатзода П С Группа Т-093 Государственные награды РФ

Государственные награды РФ Махамбет Өтемісұлы (1803 – 1846 )

Махамбет Өтемісұлы (1803 – 1846 ) Сжатие данных

Сжатие данных  Презентация "Факторинг" - скачать презентации по Экономике

Презентация "Факторинг" - скачать презентации по Экономике Метод Хюккеля

Метод Хюккеля Презентация "Золотые травы хохломы" - скачать презентации по МХК

Презентация "Золотые травы хохломы" - скачать презентации по МХК tragedia_Beslana

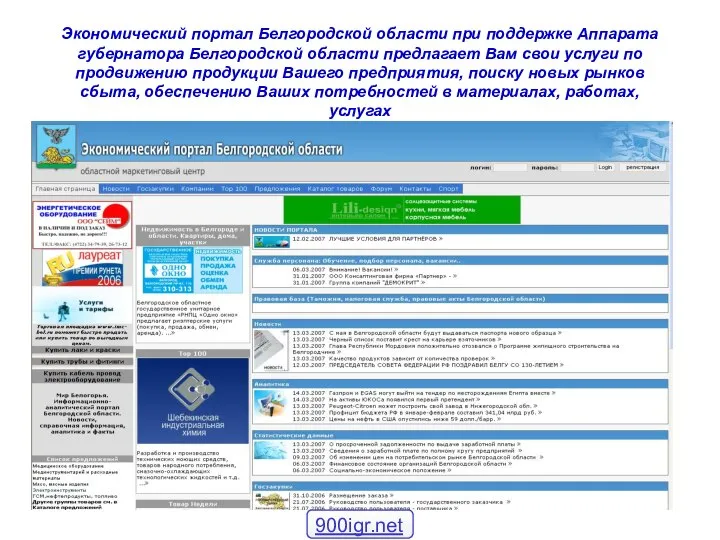

tragedia_Beslana Экономический портал Белгородской области при поддержке Аппарата губернатора Белгородской области предлагает Вам свои услуг

Экономический портал Белгородской области при поддержке Аппарата губернатора Белгородской области предлагает Вам свои услуг ТАЙМ-менеджмент Управление временем в бережливом производстве / офисе Семинар по бережливому производству

ТАЙМ-менеджмент Управление временем в бережливом производстве / офисе Семинар по бережливому производству  Морфологическая структура ландшафта

Морфологическая структура ландшафта Политическая система. Развитие теории политической системы

Политическая система. Развитие теории политической системы 7475

7475 Пресметни и посочи: /в случай че те затрудни, натисни/ 3 + 2 =

Пресметни и посочи: /в случай че те затрудни, натисни/ 3 + 2 = Индуистский храм

Индуистский храм Основные причины низкой эффективности оказания государственных (муниципальных) услуг

Основные причины низкой эффективности оказания государственных (муниципальных) услуг Презентация на тему: «Возникновение государства и права в Армении»

Презентация на тему: «Возникновение государства и права в Армении»  Германская фонология

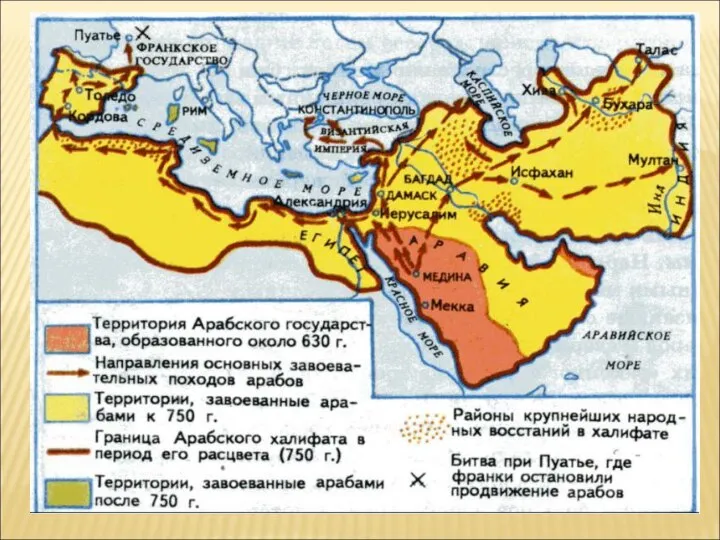

Германская фонология Культура стран халифата

Культура стран халифата СУБКУЛЬТУРЫ Субкультура (подкультура, лат. sub — под и лат. cultura — возделывание, земледелие, воспитание, почитание) в социологи

СУБКУЛЬТУРЫ Субкультура (подкультура, лат. sub — под и лат. cultura — возделывание, земледелие, воспитание, почитание) в социологи Крепежные детали. Резьбовые соединения

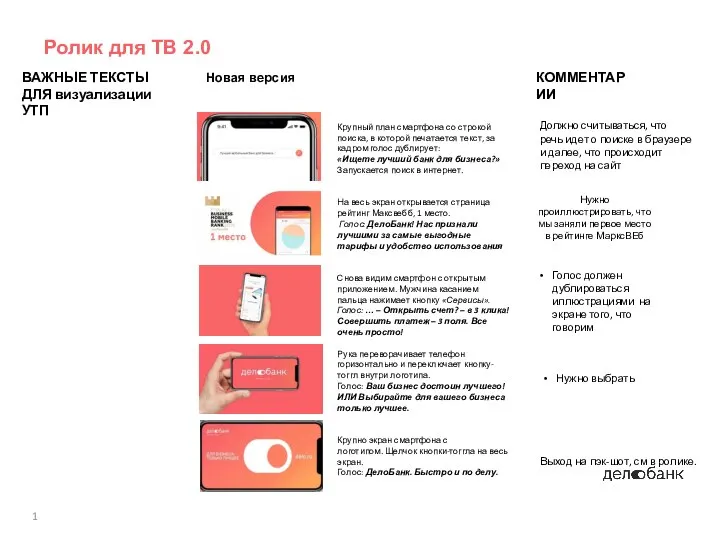

Крепежные детали. Резьбовые соединения ДелоБанк. Ролик для ТВ

ДелоБанк. Ролик для ТВ Город Киров на реке Вятка

Город Киров на реке Вятка