Содержание

- 2. Шевкопляс Б.В. Микропроцессорные структуры. Инженерные решения: Спрапвочник. – М.: Радио и связь, 1990. – 512 с.

- 3. УВК УСО УСОП Д Д Д ИМ ИМ ИМ ВК 1. СОСТАВ ТЕХНИЧЕСКОГО ОБЕСПЕЧЕНИЯ АСУ ТП

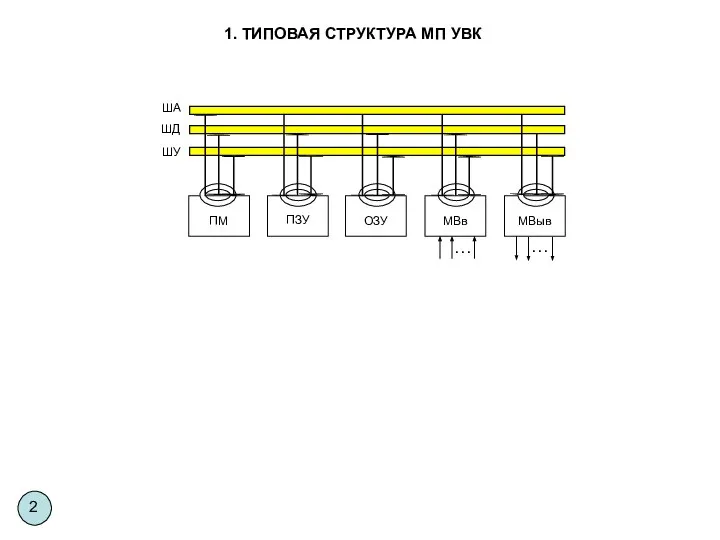

- 4. 1. ТИПОВАЯ СТРУКТУРА МП УВК

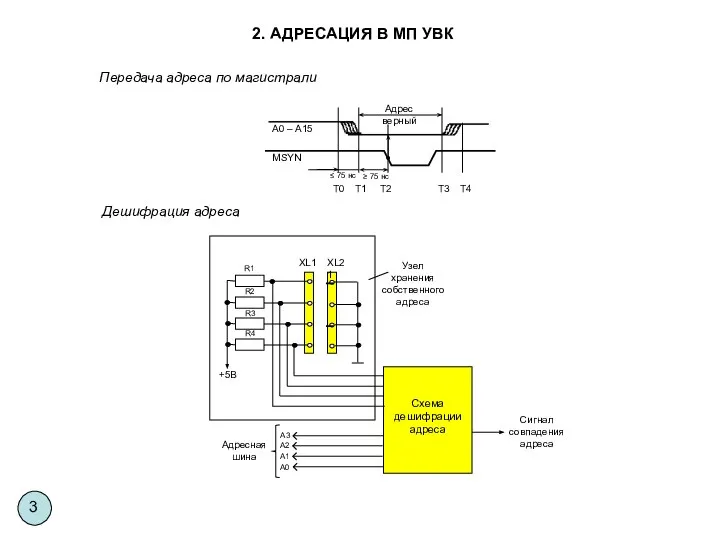

- 5. Схема дешифрации адреса А0 2. АДРЕСАЦИЯ В МП УВК Дешифрация адреса Передача адреса по магистрали

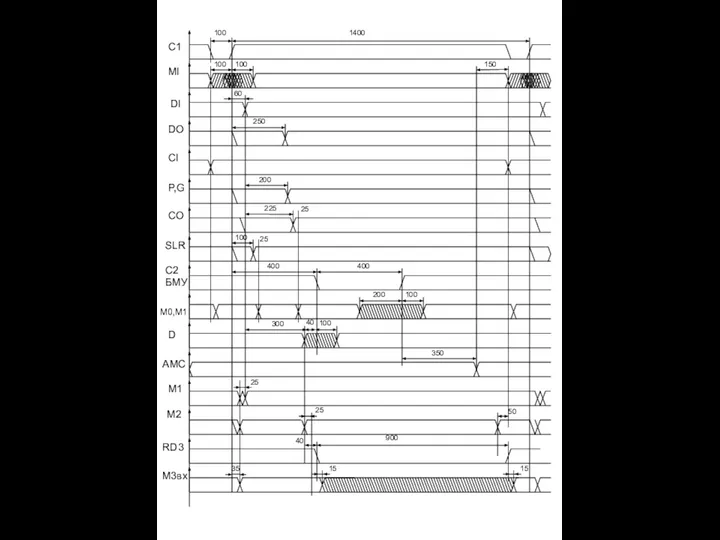

- 6. 3. ОРГАНИЗАЦИЯ ОБМЕНА ДАННЫМИ ПО ВНУТРЕННЕМУ ИНТЕРФЕЙСУ 3.1. Режим записи

- 7. 3. ОРГАНИЗАЦИЯ ОБМЕНА ДАННЫМИ ПО ВНУТРЕННЕМУ ИНТЕРФЕЙСУ 3.2. Режим чтения

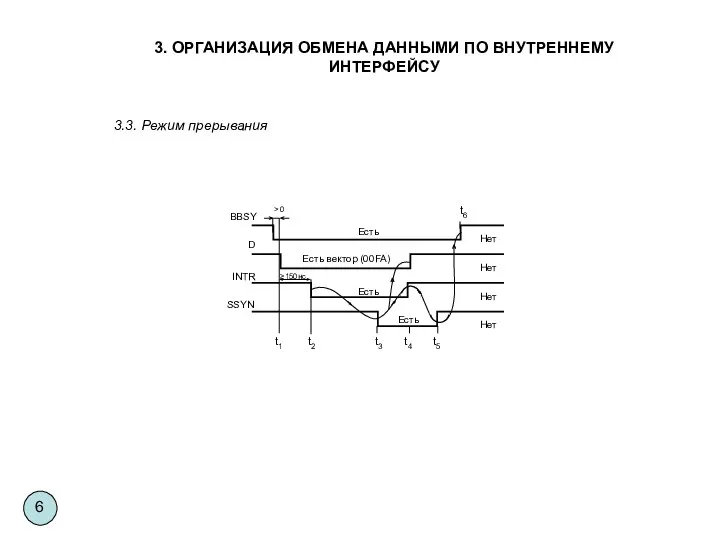

- 8. 3. ОРГАНИЗАЦИЯ ОБМЕНА ДАННЫМИ ПО ВНУТРЕННЕМУ ИНТЕРФЕЙСУ 3.3. Режим прерывания

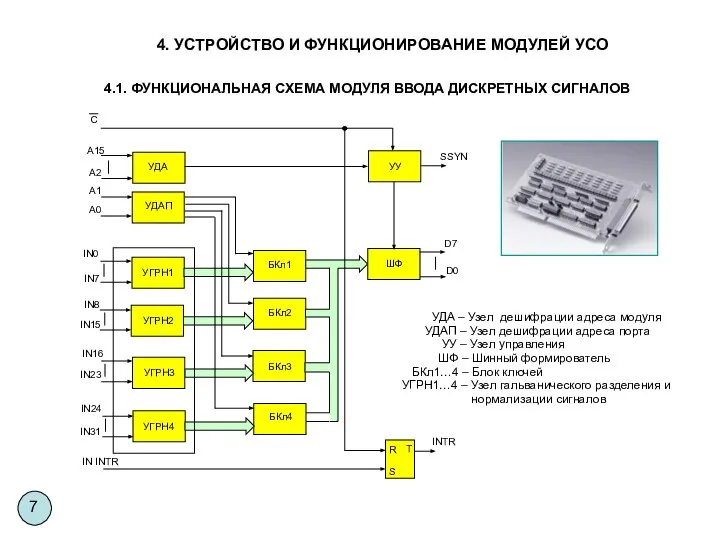

- 9. 4.1. ФУНКЦИОНАЛЬНАЯ СХЕМА МОДУЛЯ ВВОДА ДИСКРЕТНЫХ СИГНАЛОВ УДА – Узел дешифрации адреса модуля УДАП – Узел

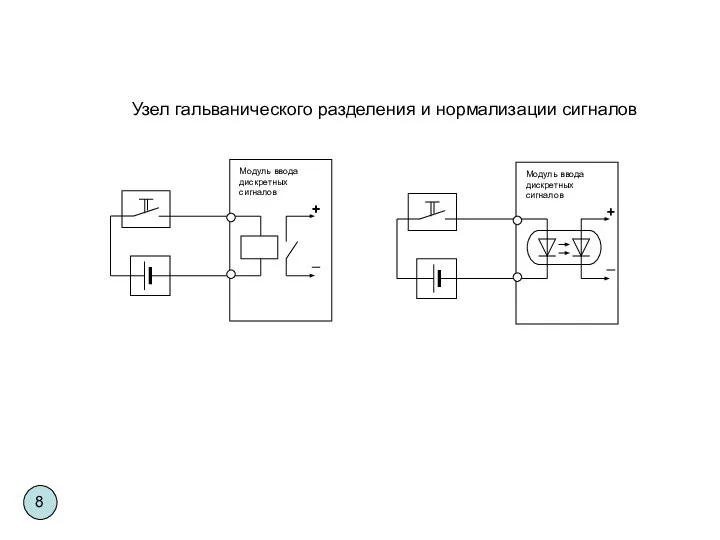

- 10. Узел гальванического разделения и нормализации сигналов

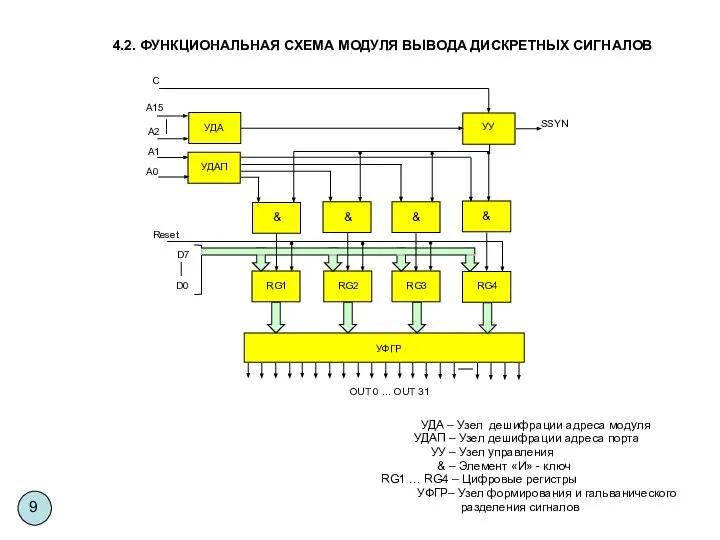

- 11. 4.2. ФУНКЦИОНАЛЬНАЯ СХЕМА МОДУЛЯ ВЫВОДА ДИСКРЕТНЫХ СИГНАЛОВ УДА – Узел дешифрации адреса модуля УДАП – Узел

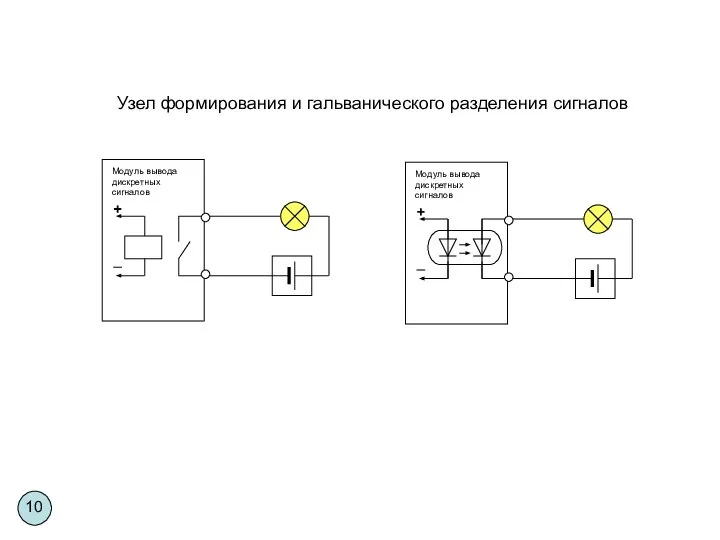

- 12. Узел формирования и гальванического разделения сигналов

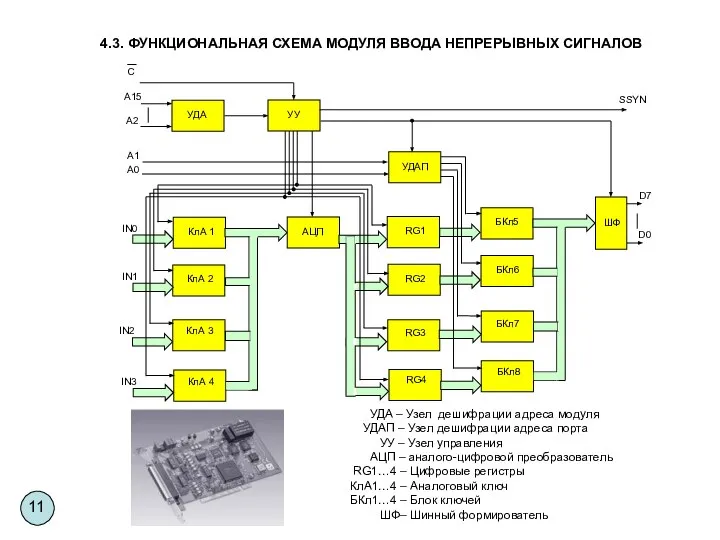

- 13. 4.3. ФУНКЦИОНАЛЬНАЯ СХЕМА МОДУЛЯ ВВОДА НЕПРЕРЫВНЫХ СИГНАЛОВ УДА – Узел дешифрации адреса модуля УДАП – Узел

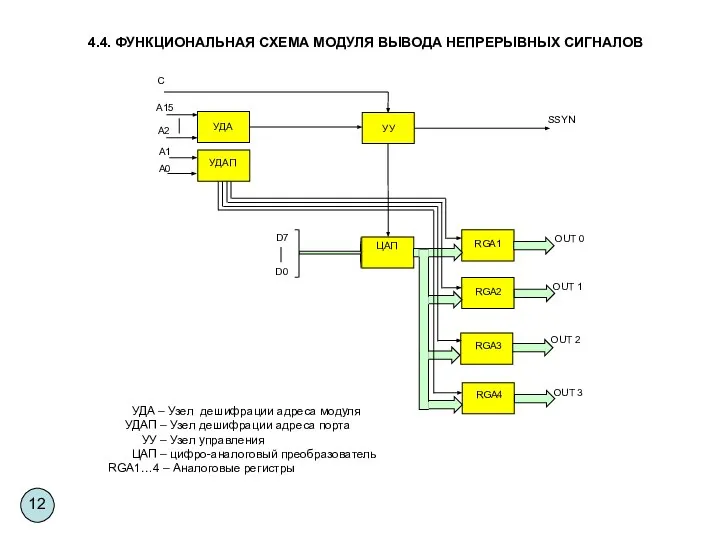

- 14. 4.4. ФУНКЦИОНАЛЬНАЯ СХЕМА МОДУЛЯ ВЫВОДА НЕПРЕРЫВНЫХ СИГНАЛОВ УДА – Узел дешифрации адреса модуля УДАП – Узел

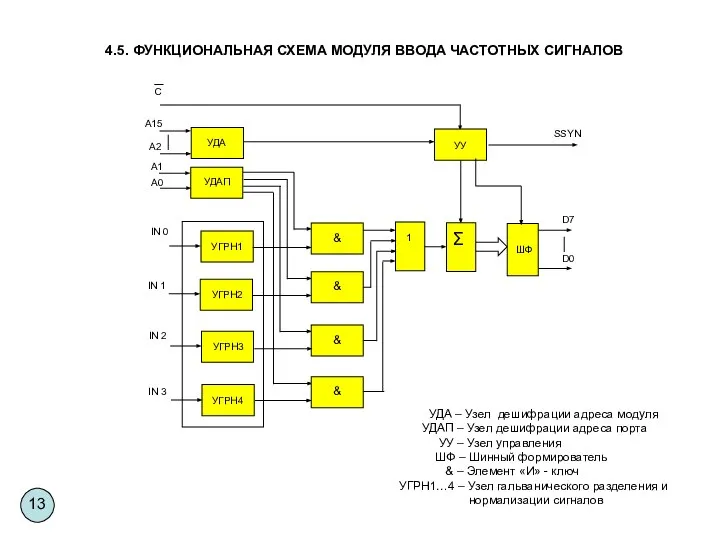

- 15. 4.5. ФУНКЦИОНАЛЬНАЯ СХЕМА МОДУЛЯ ВВОДА ЧАСТОТНЫХ СИГНАЛОВ SSYN A15 A2 A1 A0 IN 1 IN 2

- 16. 5.1. ОРГАНИЗАЦИЯ ЭЛЕКТРОННОЙ ПАМЯТИ В ПЭВМ 5. ОРГАНИЗАЦИЯ ЭЛЕКТРОННОЙ ПАМЯТИ В УВК

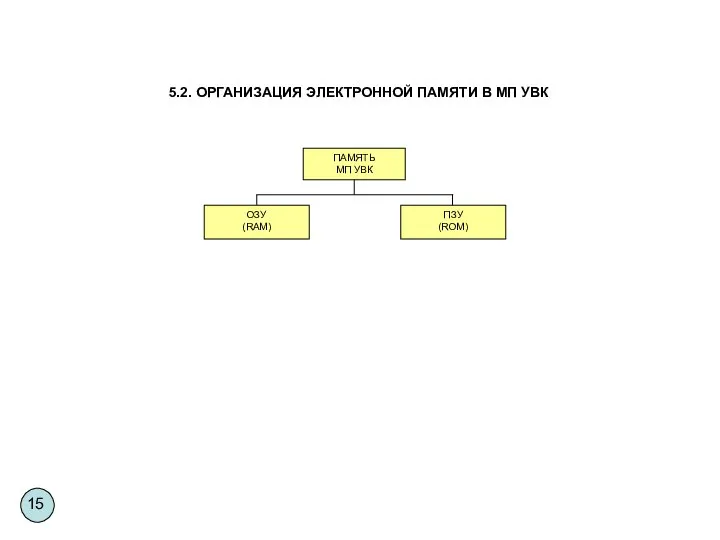

- 17. 5.2. ОРГАНИЗАЦИЯ ЭЛЕКТРОННОЙ ПАМЯТИ В МП УВК

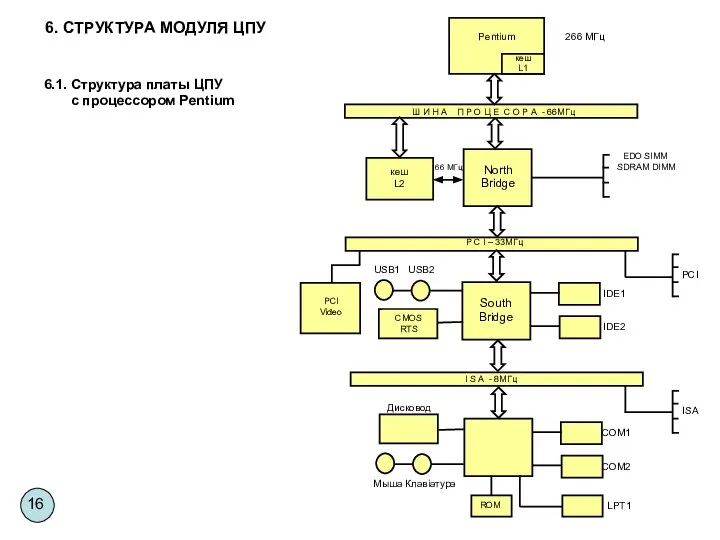

- 18. 6. СТРУКТУРА МОДУЛЯ ЦПУ 6.1. Структура платы ЦПУ с процессором Рentium

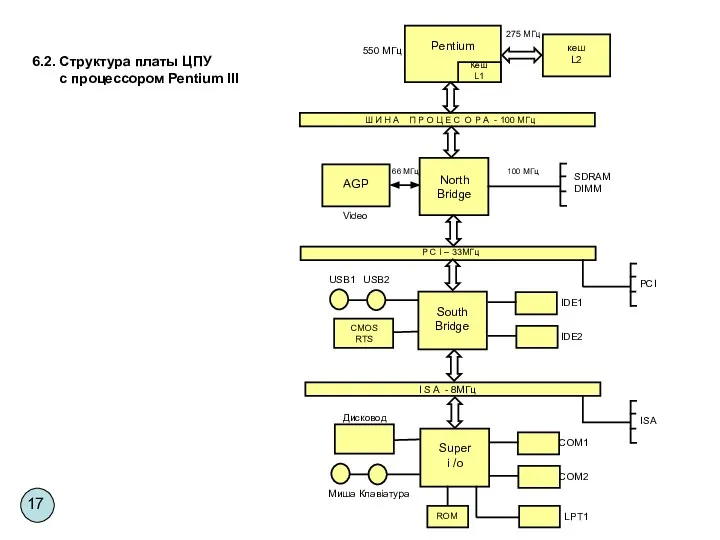

- 19. 6.2. Структура платы ЦПУ с процессором Рentium III

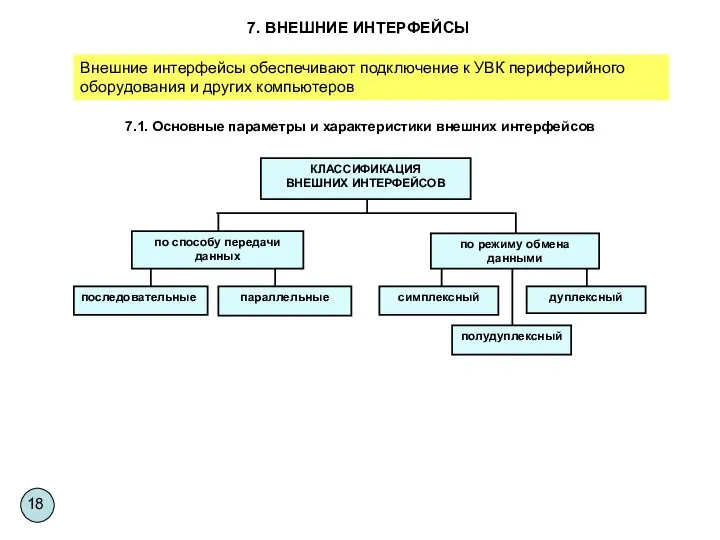

- 20. 7. ВНЕШНИЕ ИНТЕРФЕЙСЫ 7.1. Основные параметры и характеристики внешних интерфейсов Внешние интерфейсы обеспечивают подключение к УВК

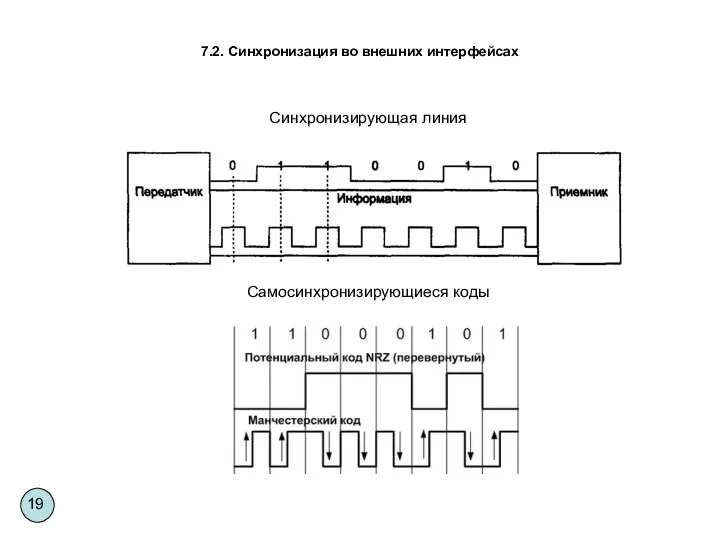

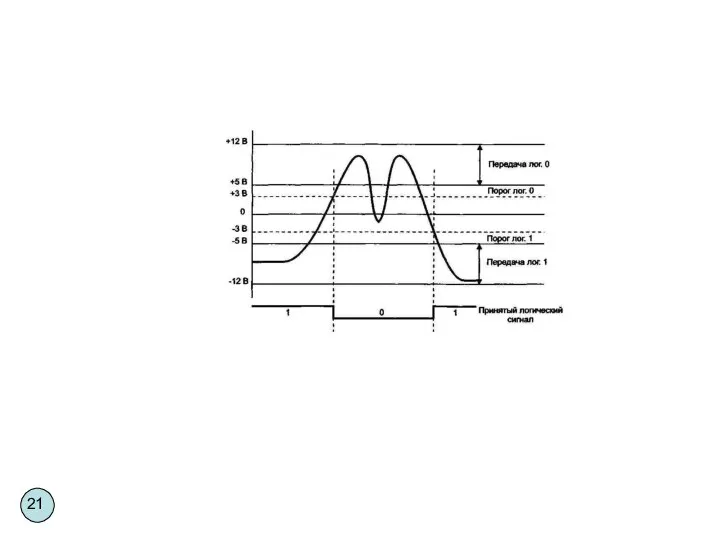

- 21. Самосинхронизирующиеся коды 7.2. Синхронизация во внешних интерфейсах Синхронизирующая линия

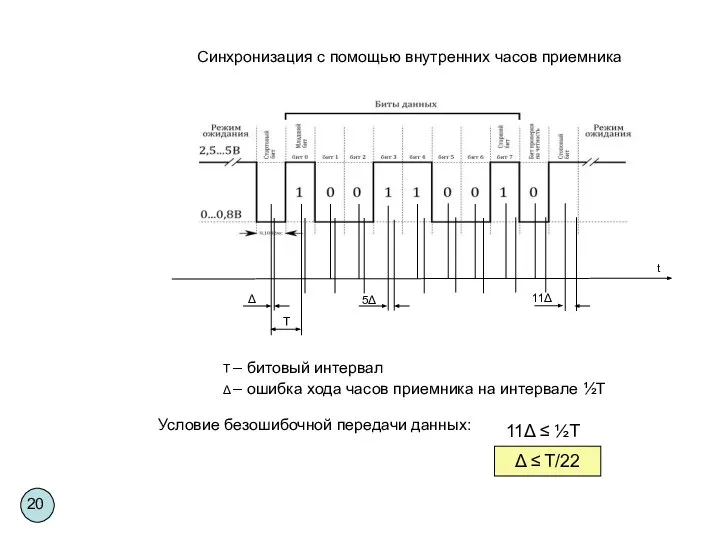

- 22. T – битовый интервал Δ – ошибка хода часов приемника на интервале ½T Условие безошибочной передачи

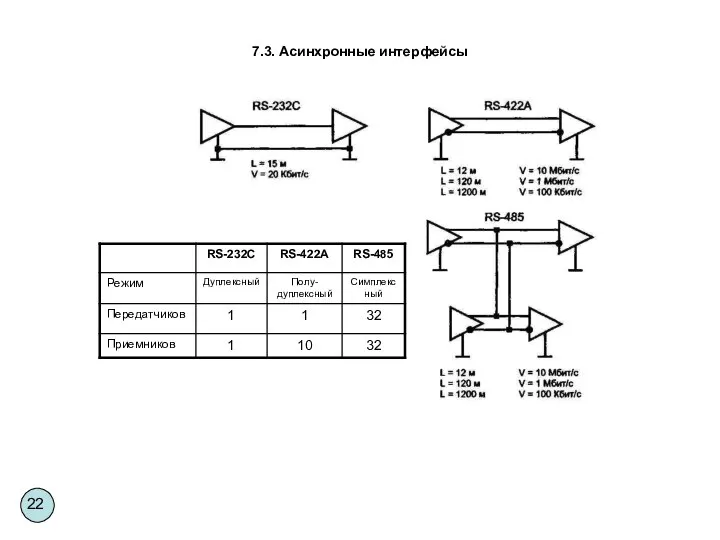

- 24. 7.3. Асинхронные интерфейсы

- 26. Скачать презентацию

Христианское образование

Христианское образование Освоение культурного наследия Многоканальная модель освоения культурного наследия

Освоение культурного наследия Многоканальная модель освоения культурного наследия Введение в XML

Введение в XML Режим дня младшего школьника

Режим дня младшего школьника  Whatsapp-лендинг. Очередь клиентов в любой бизнес без сайта и с конверсией до 80%

Whatsapp-лендинг. Очередь клиентов в любой бизнес без сайта и с конверсией до 80% Вкусовой и обонятельный анализатор

Вкусовой и обонятельный анализатор профессиональный стандарт педагога (ПСП)

профессиональный стандарт педагога (ПСП) Каменная кладка. Четыре стадии работы кладки под нагрузкой при сжатии

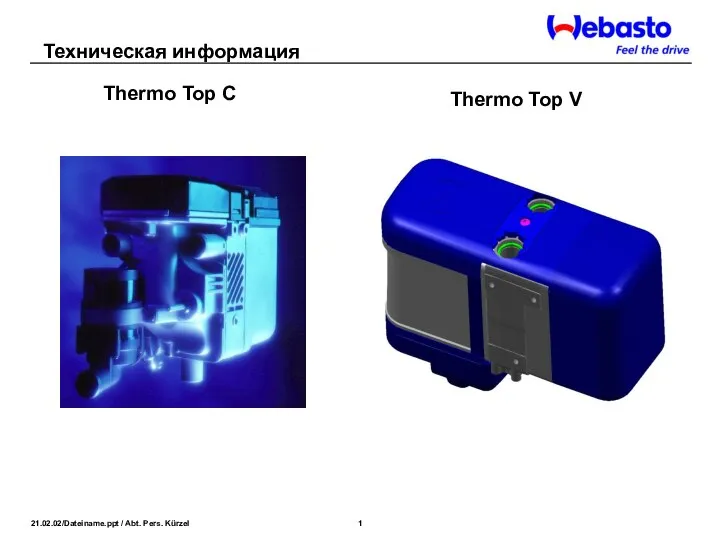

Каменная кладка. Четыре стадии работы кладки под нагрузкой при сжатии Техническая информация Thermo Top C, Thermo Top V

Техническая информация Thermo Top C, Thermo Top V Народные гуляния как традиция, исторически сложившаяся в советскую эпоху

Народные гуляния как традиция, исторически сложившаяся в советскую эпоху Презентация_modif

Презентация_modif  Құқықтық сана және құқықтық тәртіп

Құқықтық сана және құқықтық тәртіп Татарские народные праздники и обычаи

Татарские народные праздники и обычаи МЕТОДИЧЕСКАЯ ТЕМА: «АКТИВИЗАЦИЯ ПОЗНАВАТЕЛЬНОЙ ДЕЯТЕЛЬНОСТИ УЧАЩИХСЯ НА УРОКАХ ПУТЕМ ИСПОЛЬЗОВАНИЯ НОВЫХ ПЕДАГОГИЧЕСКИХ ТЕХН

МЕТОДИЧЕСКАЯ ТЕМА: «АКТИВИЗАЦИЯ ПОЗНАВАТЕЛЬНОЙ ДЕЯТЕЛЬНОСТИ УЧАЩИХСЯ НА УРОКАХ ПУТЕМ ИСПОЛЬЗОВАНИЯ НОВЫХ ПЕДАГОГИЧЕСКИХ ТЕХН План строительства пятиэтажного здания

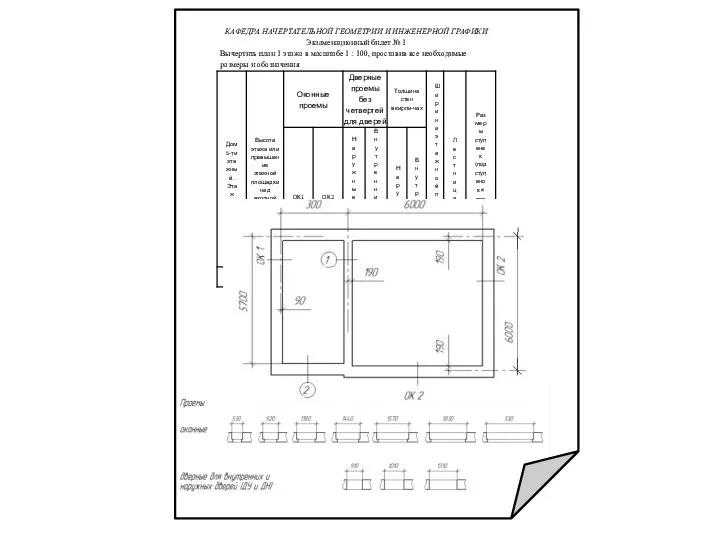

План строительства пятиэтажного здания Студенческие арт-клубы УГНТУ

Студенческие арт-клубы УГНТУ Адаптация учащихся в предметной учебной деятельности формированием понятийного аппарата, или Как овладеть языком предмета - през

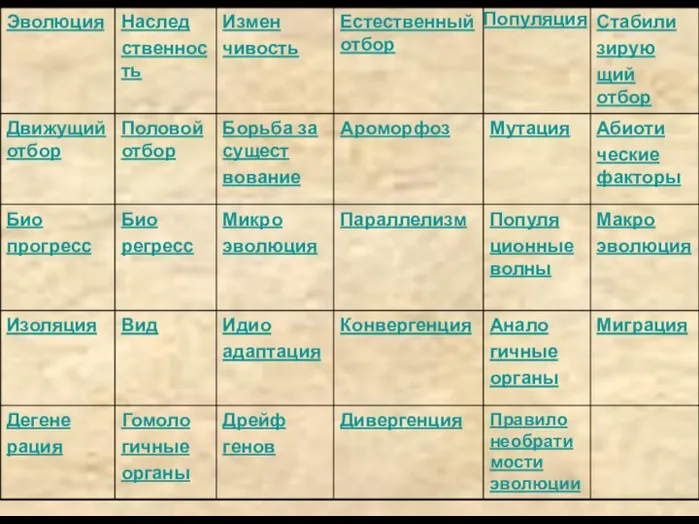

Адаптация учащихся в предметной учебной деятельности формированием понятийного аппарата, или Как овладеть языком предмета - през Общая характеристика Зарубежной Европы

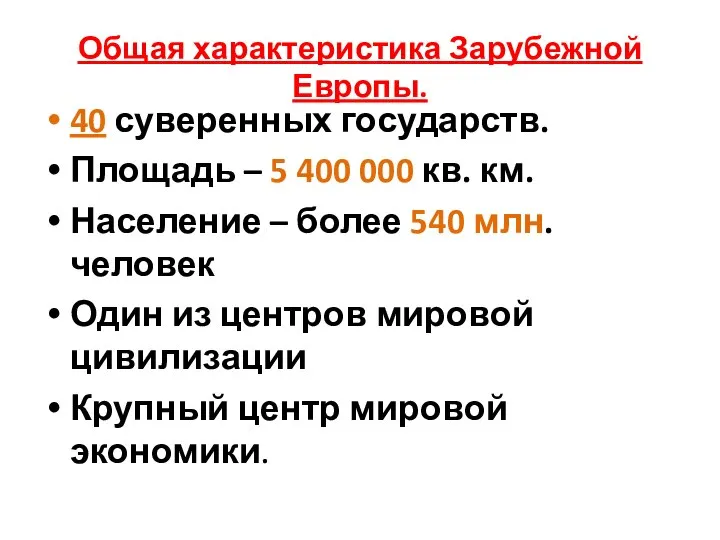

Общая характеристика Зарубежной Европы Карловы Вары

Карловы Вары Формула Тейлора

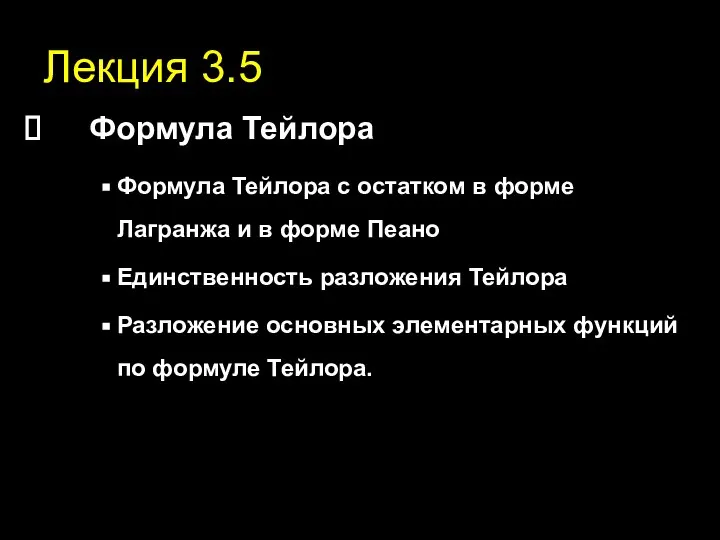

Формула Тейлора  Метод комплексных амплитуд

Метод комплексных амплитуд Социальные проблемы и безработица Выполнили ученицы 11Б класса СОШ№2: Коптева Анастасия Грачева Наталья

Социальные проблемы и безработица Выполнили ученицы 11Б класса СОШ№2: Коптева Анастасия Грачева Наталья  Boże Narodzenie

Boże Narodzenie Выполнила учитель начальных классов МОУ – Сукроменская СОШ Банникова Наталья Олеговна

Выполнила учитель начальных классов МОУ – Сукроменская СОШ Банникова Наталья Олеговна Презентация "Путешествие от барокко к классицизму 4" - скачать презентации по МХК

Презентация "Путешествие от барокко к классицизму 4" - скачать презентации по МХК Современная Front-End разработка. Объектно-ориентированное программирование в JavaScript. (Лекция 4)

Современная Front-End разработка. Объектно-ориентированное программирование в JavaScript. (Лекция 4) Електроємність. Конденсатори. (Лекция 6)

Електроємність. Конденсатори. (Лекция 6) Инклюзивный ПрофГид. Содействие профориентации и трудоустройству лиц с ОВЗ и инвалидностью

Инклюзивный ПрофГид. Содействие профориентации и трудоустройству лиц с ОВЗ и инвалидностью